课程设计报告

题目:常用中规模集成电路的VHDL设计

计算机科学与技术学院

实验一:异步时序逻辑电路的设计

一、实验目的

熟悉并掌握脉冲异步时序逻辑电路的分析方法,加深对异步时序逻辑电路的理解。掌握电平异步时序逻辑电路实验的设计方法及如何消除临界竞争。

二、实验设备与器件

1.Basys2开发板

2.JTAG下载电缆

三、实验内容

用电平异步时序逻辑电路实现下降沿出发的D触发器(无空翻)。

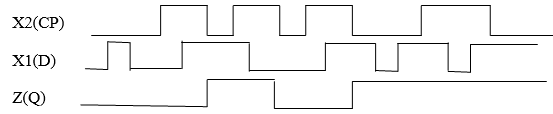

典型的输入输出时间图如下:

实验时先建立该电路的原始流程表及总态图。

四、实验步骤

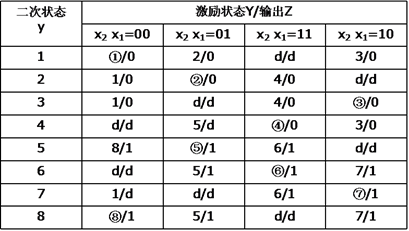

1.建立原始流程表:

2.化简原始流程表:

(1)隐含表 找出相容行对

(2)作合并图,求最大相容行类:

得最大相容类为{(1,2,3),(3,4),(5,6,8),(6,7)};

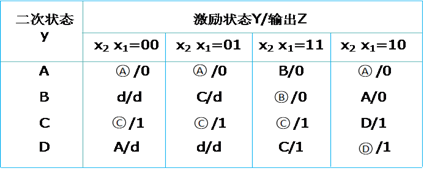

选择其中一个最小闭覆盖:{(1,2,3),(4),(5,6,8),(7)},分别用A,B,C,D表示。

3.最简流程表

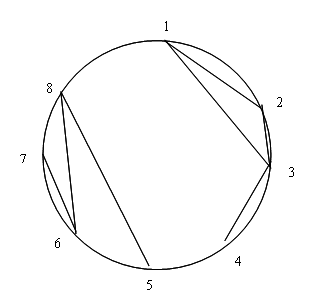

4.状态编码

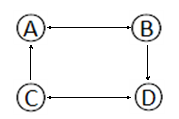

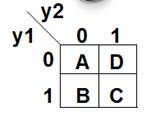

状态相邻图: 状态分配方案:

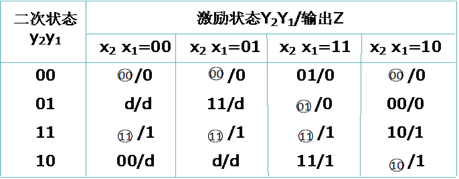

可得二进制流程表如下:

卡诺图化简得激励和输出函数的表达式:

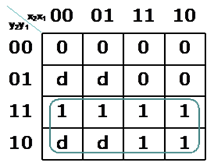

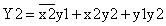

Y2的卡诺图 Y1的卡诺图

Z的卡诺图

5. ISPLEVER进行波形仿真

发现该电路存在着竞争现象。返回检查表达式,发现Y2、Y1都存在着“0”险象,用添加冗余项的方式消除竞争,修改其表达式如下:

重新设计电路如下所示:

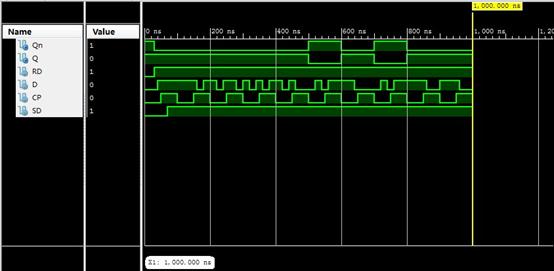

用ISPLEVER仿真,得到如下波形:

6.实验结果测试:

下载到Basys2开发板上,按引脚连线,测试D触发器功能,D端接高电平“1”时,按下按钮给出一个下降沿时钟脉冲,输出端的灯变红,D端接低电平“0”时,按下按钮给出一个下降沿时钟脉冲,输出端的灯变绿。与D触发器的逻辑功能吻合。

五、实验体会

这次试验让我体会最深的就是:“使用ISPLEVER编程环境时要时刻注意保存。”很多次都是因为没有及时保存而软件没有自动保存导致运行时老出错。操作这样一个系统也需要扎实的基础和经验。这是第一次使用这种开发环境设计一个小东西,体会还是蛮深的,相信随着之后对它的进一步了解,我可以学到更多。

实验二:常用中规模集成电路的VHDL设计

一、实验目的

1、进一步熟悉Lattice公司EDA开发系统ISPLEVER软件平台的操作。

2、学习及提高VHDL的设计能力。

3、根据不同的功能要求编写与之对应的优质高效VHDL代码。

二、实验器材

1、Basys2下载板;

2、JTAG下载电缆。

三、实验内容

计数器的设计:

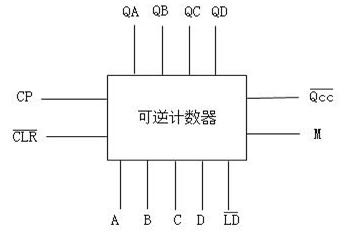

设计一个能清0、置数和进位输出的增1/减1的4位二进制计数器,如下图1所示:

图1

输入信号 为清0端,信号LD为置数端,将A、B、C、D的输入值送到计数器中,并立即在QA、QB、QC、QD中输出。输入信号M为模式选择端,当M=1时加1计数,当M=0时减1计数。当CP端输入一个上升沿信号时进行一次计数,计数有进位/借位时

为清0端,信号LD为置数端,将A、B、C、D的输入值送到计数器中,并立即在QA、QB、QC、QD中输出。输入信号M为模式选择端,当M=1时加1计数,当M=0时减1计数。当CP端输入一个上升沿信号时进行一次计数,计数有进位/借位时 端输出一个负脉冲。

端输出一个负脉冲。

四、实验步骤

1、编写符合要求的VHDL代码

VHDL代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Create Date: 11:16:07 06/11/2013

// Design Name:

// Module Name:

// Project Name:

// Tool versions:

// Revision

// Additional Comments:

//////////////////////////////////////////////////////////////////////////////////

module C_4(load,clr,cp, up_down ,DIN , c ,DOUT ,);

input load ;

wire load ;

input clr ;

wire clr ;

input cp;

//wire cp ;

input up_down ;

wire up_down ;

input [3:0] DIN ;

wire [3:0] DIN ;

output c ;

reg c ;

output [3:0] DOUT ;

wire [3:0] DOUT ;

reg [3:0] data_r ;

assign DOUT = data_r ;

always @ ( posedge cp or negedge clr or negedge load)

begin

if ( clr == 0) //同步清零

data_r <= 0;

else if ( load == 0) //同步预置

data_r <= DIN;

else begin if ( up_down ==1) //转加计数

begin

if ( data_r == 4'b1111) begin //加计数

data_r <= 4'b0000;

c = 0;

end

else begin

data_r <= data_r +1;

c = 1 ;

end

end

else //转减计数

begin

if ( data_r == 4'b0000) begin //减计数

data_r <= 4'b1111;

c = 0;

end

else begin

data_r <= data_r -1;

c = 1 ;

end

end

end

end

endmodule

2、编写约束条件

约束条件代码如下:

NET "cp" TNM_NET = "cp";

NET "DIN[0]" LOC = P11;

NET "DIN[1]" LOC = L3;

NET "DIN[2]" LOC = K3;

NET "DIN[3]" LOC = B4;

NET "DOUT[0]" LOC = M5;

NET "DOUT[1]" LOC = M11;

NET "DOUT[2]" LOC = P7;

NET "DOUT[3]" LOC = P6;

NET "c" LOC = G1;

NET "up_down" LOC = N3;

NET "cp" LOC = A7;

NET "clr" LOC = E2;

NET "load" LOC = F3;

# PlanAhead Generated physical constraints

TIMESPEC TS_cp = PERIOD "cp" 1 KHz HIGH 50%;

3、建立仿真波形,并对其中的某一段波形进行检测来检验程序是否正确

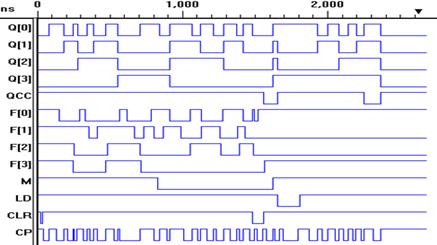

仿真波形图如下图2所示:

图2

4、把熔丝图文件下载到Basys2开发板上并进行测试

下载到Basys2开发板上,按引脚连线,测试四位二进制的加减计数器的功能,当M输入“1”时,按下时钟开关可以实现加1计数,当M输入“0”时,按下时钟开关可以实现减1计数, 而且当CLR置0时,灯全不亮,为零。所以功能完全吻合。

五、实验体会

在《常用中规模集成电路的VHDL设计》这次实验中,第一次接触到用软件对硬件进行仿真。除了初步掌握EDA开发工具和常规基本的使用技巧外,在调试与排错方面,也有很大的收获,对于Verilog的编程能力也有了一定的提升。在FPGA编程环境中对数字电子系统软件工程开发流程和基本思想都有了基本的了解。当然,掌握EDA技术是一个长期实验积累的过程,需要自己不断的努力积累经验,分阶段循序渐进地进行。