西安电子科技大学

实验报告

班 级:

学 号:

姓 名:

地 点: EⅡ-505

批 次: 第二批

时 间:星期五下午、晚上

实验一 3-8译码器电路设计实验

(一)实验名称:

3-8译码器电路设计

(二)实验目的:

1)掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;

2)掌握组合逻辑电路设计的一般方法;

3)掌握程序下载方法,了解UCF文件的格式;

4)初步了解开发板资源,掌握开发板使用方法。重点了解滑动开关和LED显示灯的使用方法。

5)理解并掌握VHDL程序的结构,掌握输入输出端口的含义;

(三)实验内容:

(1)用VHDL实现3-8译码器模块

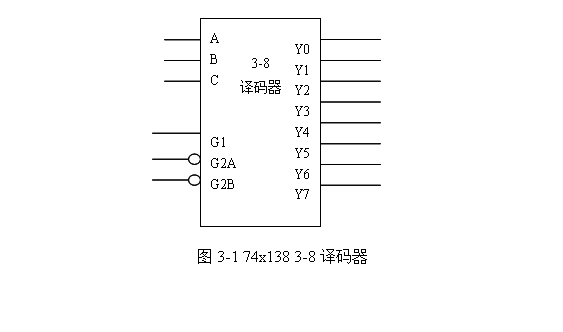

译码器电路如图3-1所示。其功能如表3-1所示。试用VHDL完成该译码器的设计,并在开发板上进行检验。

表3-1 译码器功能表

(2)将程序下载到FPGA并进行检验

l 资源使用要求:

n 用滑动开关SW0~SW4作为输入A,B,C,G1;

n 滑动开关BTN_EAST,BTN_WEST作为控制端G2A,G2B;

n 8个LED灯表示8个输出。

l 检验方法:

当SW0处于OFF(G1=1)或者SW1处于ON(G2A=1)或者SW2处于ON(G2B=1)位置时,所 有LED灯灭;

当SW0处于ON(G1=1),且BTN_EAST,BTN_WEST均处于OFF状态时,反映当前输入的译码输出在LED灯上显示,即当输入为000(滑动开关SW0-SW2处于OFF状态),LED0亮,其它灯灭,等等。

(四)实验步骤:

1)启动ISE,新建工程文件,编写3-8译码器的VHDL模块;

2)新建UCF文件,输入位置约束;

3)完成综合、实现,生成下载文件;

4)连接开发板USB下载线,开启开发板电源;

5)下载到FPGA;

6)拨动开关,验证结果是否正确。

(五)实验代码:

entity decode38 is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

G1 : in STD_LOGIC;

G2A : in STD_LOGIC;

G2B : in STD_LOGIC;

Y : out STD_LOGIC_VECTOR (7 downto 0));

end decode38;

architecture Behavioral of decode38 is

signal din: std_logic_vector(2 downto 0);

begin

din <= C&B&A;

PROCESS(din,G1,G2A,G2B)

begin

if (G1='1' AND G2A='0' AND G2B='0') THEN

case din is

when "000" => Y<="00000001";

when "001" => Y<="00000010";

when "010" => Y<="00000100";

when "011" => Y<="00001000";

when "100" => Y<="00010000";

when "101" => Y<="00100000";

when "110" => Y<="01000000";

when "111" => Y<="10000000";

when others => Y<="00000000";

end case;

elsif(G1='0' OR G2A='1' OR G2B='1')THEN

Y <= "00000000";

else

null;

end if;

end process;

end Behavioral;

约束性文件

NET "A" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP;

NET "B" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP;

NET "C" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP;

NET "G1" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP;

NET "Y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "G2A" LOC = "H13" | IOSTANDARD = LVTTL | PULLdown;

NET "G2B" LOC = "D18" | IOSTANDARD = LVTTL | PULLdown;

实验二 可逆计数器设计实验

(一)实验名称:

八位可逆计数器电路设计

(二)实验目的:

1)进一步熟练ISE开发工具,巩固FPGA开发的基本步骤;

2)掌握设计仿真方法;

3)掌握时序逻辑电路设计的一般方法,掌握时钟分频程序设计方法;

4)理解VHDL的层次结构设计,掌握原理图输入方法;

5)巩固程序下载方法;

6)了解开发板时钟资源,以及时钟分频方法。

(三)实验内容:

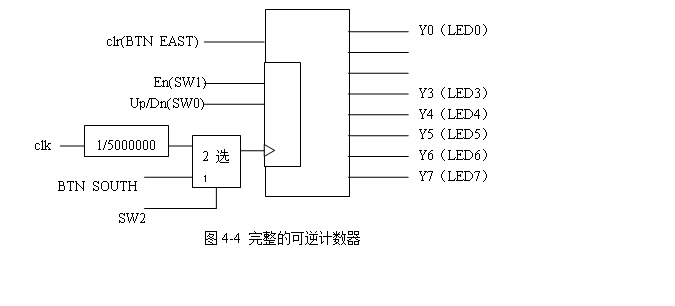

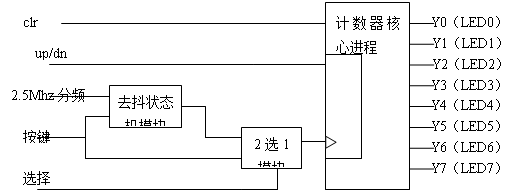

本实验分多个模块实现,采用原理图输入方法完成设计输入。

(1)实现如下八位可逆计数器

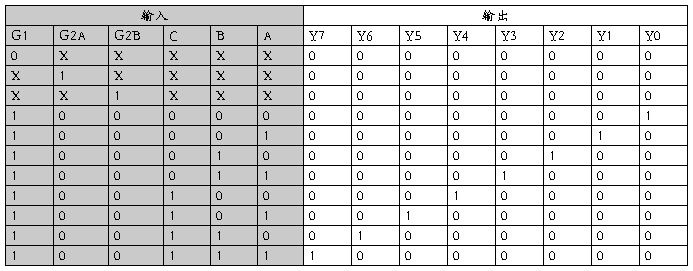

可逆计数器电路图及功能表如图4-1和表4-1所示。用VHDL完成该电路模块的设计,并生成原理图。

表4-1 可逆计数器功能表

(2)资源使用要求及实现方法:

1)用LED0~LED7作为计数器输出显示,LED7为高位,LED0为低位;

2)SW0为计数方向up/dn控制;

3)SW1为计数允许EN控制端;

4)BTN_EAST为clr按钮;

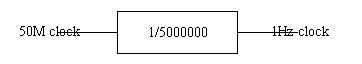

5)计数时钟频率为1Hz,通过对50Mhz系统时钟分频得到,分频电路独立编写一个模块,如图4-2所示。完成模块设计,并生成原理图;

图4-2 1/5000000分频器

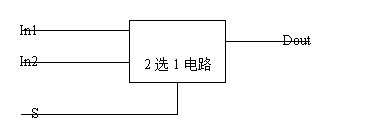

6)计数器扩展:可以对按键次数进行计数(按键为BTN_SOUTH),即通过SW2选择计数源。即当S='1'时,输出In1,当S='0'时,输出In2。

二选一电路如图4-3所示。

图4-3 二选一电路

7)将图4-1~图4-3三个模块连接起来,构成一个完整计数器。如图4-4所示。

(四) 实验步骤:

1)建立工程文件,顶层文件为原理图;

2)编写分频模块程序:输入50MHz系统时钟,输出为1Hz计数时钟;

3)编写2选1模块,输入为按键、1Hz时钟和开关SW2,输出为计数源;

4)编写计数器模块主程序模块;

5)在原理图中,将各个模块连接,使用pinhead分配引脚资源;

6)对程序进行功能仿真;

7)下载程序,进行验证。

(五)实验代码:

计数器COUNTER:

entity COUNTER is

Port ( clr : in STD_LOGIC;

en : in STD_LOGIC;

updown : in STD_LOGIC;

clk : in STD_LOGIC;

y : out STD_LOGIC_VECTOR (7 downto 0));

end COUNTER;

architecture Behavioral of COUNTER is

signal sum:STD_LOGIC_VECTOR (7 downto 0):="00000000";

begin

process(sum,clr,en,updown,clk)

begin

if(clk'event and clk ='1')then

if(clr='1')then

sum<="00000000";

y<="00000000";

elsif(en='0')then

y<=sum;

elsif(updown='1')then

sum<=sum+1;

y<=sum;

else

sum<=sum-1;

y<=sum;

end if;

end if;

end process;

end Behavioral;

分频器FREQ:

entity FREQ is

Port ( clk50M : in STD_LOGIC;

clk1hz : out STD_LOGIC);

end FREQ;

architecture Behavioral of FREQ is

begin

process(clk50M)

variable num:INTEGER range 0 to 50000002:=0;

begin

if(clk50M'event and clk50M ='1')then

num:=num+1;

if(num<25000000)then

clk1hz<='1';

else

clk1hz<='0';

if (num>50000000)then

num:=0;

end if;

end if;

end if;

end process;

end Behavioral;

2选1数据选择器SEL:

entity SEL is

Port ( in1 : in STD_LOGIC;

in2 : in STD_LOGIC;

S : in STD_LOGIC;

Dout : out STD_LOGIC);

end SEL;

architecture Behavioral of SEL is

begin

process(in1,in2,S)

begin

if(S = '0')then

Dout <= in1;

else

Dout <= in2;

end if;

end process;

end Behavioral;

顶层文件TOP:

entity TOP is

Port ( BTN_EAST : in STD_LOGIC;

SW1 : in STD_LOGIC;

SW0 : in STD_LOGIC;

CLK : in STD_LOGIC;

BTN_SOUTH : in STD_LOGIC;

SW2 : in STD_LOGIC;

Y : out STD_LOGIC_VECTOR (7 downto 0));

end TOP;

architecture Behavioral of TOP is

COMPONENT FREQ

PORT(

clk50M : IN std_logic;

clk1hz : OUT std_logic

);

END COMPONENT;

COMPONENT SEL

PORT(

in1 : IN std_logic;

in2 : IN std_logic;

S : IN std_logic;

Dout : OUT std_logic

);

END COMPONENT;

COMPONENT COUNTER

PORT(

clr : IN std_logic;

en : IN std_logic;

updown : IN std_logic;

clk : IN std_logic;

y : OUT std_logic_vector(7 downto 0)

);

END COMPONENT;

signal CLKOUT:STD_LOGIC;

signal JIX:STD_LOGIC;

begin

Inst_FREQ: FREQ PORT MAP(

clk50M =>CLK ,

clk1hz =>CLKOUT

);

Inst_SEL: SEL PORT MAP(

in1 =>CLKOUT,

in2 =>BTN_SOUTH,

S =>SW2,

Dout =>JIX

);

Inst_COUNTER: COUNTER PORT MAP(

clr =>BTN_EAST,

en =>SW1,

updown =>SW0,

clk =>JIX,

y =>Y

);

约束性文件

NET "clr" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP;

NET "en" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP;

NET "updown" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP;

NET "Y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "clk" LOC = "C9" | IOSTANDARD = LVCMOS33 ;

NET "clk" PERIOD = 20.0ns HIGH 40%;

NET "SW2" LOC = "V4" | IOSTANDARD = LVTTL | PULLdown;

实验三 按键抖动消除及验证电路设计

(一)实验名称:

按键抖动消除及验证电路设计

(二)实验目的:

1)进一步熟练ISE开发工具,巩固FPGA开发的基本步骤,掌握功能仿真方法;

2)了解按键抖动的原因,抖动消除方法;

3)掌握状态机的设计方法;

4)掌握消除抖动的状态机设计方法;

5)巩固程序下载方法。

(三)实验内容:

(1) 原理简介

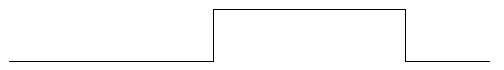

按键动作发生时,按键的输出会出现不稳定的逻辑’0’和逻辑’1’的跳变。该信号直接输入到计数器之类电路,会发生计数错误。如图5-1所示。去抖的目的是根据抖动信号产生如图5-2所示的信号。

图5-1 信号抖动(pushbtn)

图5-2 去抖后的信号(key_out)

(2) 提示:状态机设计思路

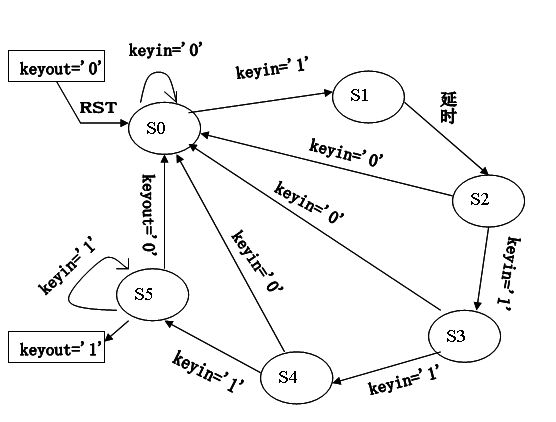

设置六个状态:S0,S1,S2,S3,S4,S5。

电路启动时,进入复位状态S0,在S0状态下,去抖输出信号key_out为‘0’,时钟信号divclk(频率为2.5Mhz,通过50Mhz系统时钟20分频得到)以一定频率采样按键输入信号pushbtn,如果采样到pushbtn = ‘0’,则停留在S0状态,并继续采样,一旦采样到pushbtn=’1’,则转入S1延时状态,进行消抖延时(延时可以用计数器来完成,比如50个divclk周期),当延时结束时,Delay_end=’1’,则转入S2状态,在此状态下,时钟信号divclk以一定频率采样按键输入pushbtn,如果pushbtn = ‘0’则转入S0,否则转入S3;状态S3,S4的转换过程和条件与S2相同,在状态S4下,如果pushbtn=’1’,则转入S5状态,当进入S5时,表示经过S2,S3,S4三个连续状态检测按键输入pushbtn都为‘1’,则认为按键处于稳定状态,在S5输出按键确认信号key_out =’1’。

同时在状态S5下,时钟信号divclk检测按键输入pushbtn,如果pushbtn = ‘1’,表示按键未释放,继续停留在S5,检测输入信号,如果检测到pushbtn= ‘0’,表示按键已经释放,输出key_out= ‘0’, 返回到状态S0,等待下一次按键操作。

(3)完成验证电路设计

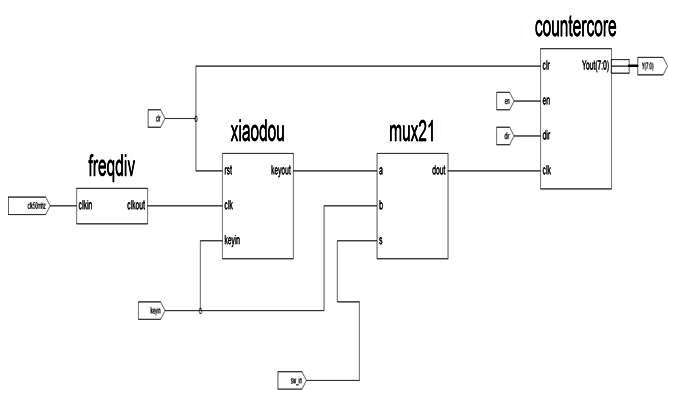

设计一个按键计数器,通过选择开关,对未去抖的信号和去抖后的信号分别进行计数。验证设计的正确性。完整的原理图如图5-3所示。

提示,去抖电路的采样时钟最好通过50Mhz进行分频后产生。

图5-3 完整电路

实际设计电路如下图所示:

资源使用要求:

1)用LED0~LED7作为计数输出。资源约束为:

NET "y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

2)BTN_SOUTH作为待计数的按键。资源约束为:

NET "pushbtn" LOC = "K17" | IOSTANDARD = LVTTL | PULLDOWN; #BTN_SOUTH

3)对去抖信号还是直接按键计数选择用SW1开关控制。即当SW1处于‘1’状态,对去抖后的信号计数,否则直接对按键btn_south计数。资源约束为:

NET "jitteren" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ; #SW1

4)SW0用来控制加1计数还是减1计数,当up/dn = '1'时,加1计数。资源约束为:

NET "updown" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ; #SW0

5)BTN_EAST作为计数器清0控制,当按下时,对计数器清0,资源为:

NET "clr" LOC = "H13" | IOSTANDARD = LVTTL | PULLDOWN ; #BTN_EAST

6)系统时钟为50Mhz,资源为:

NET "clk55Mhz" LOC = "C9" | IOSTANDARD = LVCMOS33 ;

注:状态机使用对系统时钟进行分频后的时钟信号。

(四)实验步骤:

1)画出电路的状态转换图;

2)编写完整的VHDL程序;

3)下载程序,进行验证

(五)实验代码:

器件之间的连接图:

消抖电路的设计

entity xiaoxiao is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

keyin : in STD_LOGIC;

keyout : out STD_LOGIC);

end xiaoxiao;

architecture Behavioral of xiaoxiao is

TYPE states IS (S0,S1,S2,S3,S4,S5);

SIGNAL next_state: states;

BEGIN

PROCESS (clk,rst,keyin)

variable count:integer:= 1000;

begin

IF (rst = '1') THEN

next_state <= s0;

ELSIF (clk'EVENT AND clk = '1')THEN

CASE next_state IS

when s0 =>

if (keyin = '1')then

next_state <= s1;

else null;

end if;

when s1=>

count := count -1;

if (count = 0) then

count := 1000;

next_state <= s2;

else null;

end if;

when s2=>

if (keyin='0') then

next_state <= s0;

else next_state <= s3;

end if;

when s3=>

if (keyin='0') then

next_state <= s0;

else next_state <= s4;

end if;

when s4=>

if (keyin='0') then

next_state <= s0;

else

next_state <= s5;

keyout <= '1';

end if;

when s5=>

if (keyin='0') then

keyout <= '0';

next_state <= s0;

end if;

end case;

end if;

End process;

end Behavioral;

约束性文件

NET "clr" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP;

NET "updn" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP;

NET "sel" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP;

NET "Y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "Y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "divclk" LOC = "C9" | IOSTANDARD = LVCMOS33 ;

NET "divclk" PERIOD = 20.0ns HIGH 40%;

NET "but" LOC = "V4" | IOSTANDARD = LVTTL | PULLdown;

实验四 两人乒乓球游戏

(一)实验名称:

两人乒乓球游戏

(二)实验目的:

1)进一步熟练ISE开发工具,巩固FPGA开发的基本步骤,掌握功能仿真方法;

2)巩固状态机的设计方法;

3)巩固按键消抖电路设计方法;

4)掌握多进程程序设计方法;

5)巩固程序下载方法;

6)了解开发板时钟资源,以及时钟分频方法。

(三)实验内容:

(1) 原理简介

两人乒乓游戏机用8个发光二极管代表乒乓球台,中间两个发光二极管作为乒乓球网,用点亮的发光二极管按照一定的方向移动来表示球的运动。在游戏机的两侧各设置发球和击球开关,甲乙双方按乒乓球比赛规则来操作开关。当甲方按动发球开关时,靠近甲方的第一个发光二极管亮,然后发光二极管由甲方向乙方依次点亮,代表乒乓球的移动,当球过网后,按照设计者规定的球位乙方就可以击球。若乙方提前击球或者未击到球,则甲方得分。然后重新发球比赛,直到一方达到21分为止,记分清0,重新开始新一局比赛。

(2) 提示:状态机设计思路

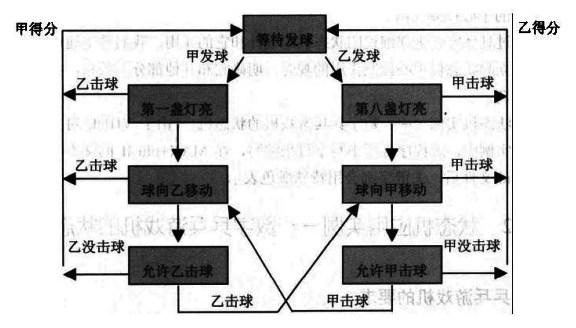

设置七个状态:“等待发球状态”、“第一盏灯亮状态”、“第八盏灯亮状态”、“球向乙移动状态” 、“球向甲移动状态”、“允许甲击球状态” 、“允许乙击球状态”。开始的时候处于“等待发球状态”,若甲发球则状态转移到“第一盏灯亮状态”,若乙发球则转移到“第八盏灯亮状态”。以甲发球为例:若发球后乙没有提前击球(规定球移动到对方第一个发光二极管时允许击球),那么状态机从“第一盏灯亮状态”转移到“球向乙移动状态”,若此时乙依然没有提前击球,状态就转移到“允许乙击球状态”,在此状态下,如果乙击球了,那么状态就转移到“球向甲移动状态”。在“第一盏灯亮状态”、“球向乙移动状态”中,如果乙击球了,就算提前击球,这样甲得分,状态转移到“等待发球状态”等待发球。“球向甲移动状态”之后的过程和前面的过程只不过是甲乙角色的调换而已,状态转移规则一样。状态转换图如图5-1所示。

图6-1 乒乓球游戏状态转换图

(3)实体设计提示

在输入端口上:

1)考虑一个异步置位端口reset,用于在系统不正常时回到初始常态;

2)两个发球输入端serve1和serve2,逻辑‘1’分别标识甲方和乙方发球;

3)两个击球输入端hit1和hit2,逻辑‘1’分别标识甲方和乙方击球;

4)一个开始游戏按钮startbtn,处于逻辑‘1’标识可以游戏;

5)时钟输入端口clk;

输出端口:

8个二极管,标识乒乓球台。

(4)资源使用要求

1)用LED0~LED7作为乒乓球台,其中LED3,LED4作为球网,总是点亮;

2)BTN_EAST作为开始游戏按钮,按下一次,重新开始游戏;

3)BTN_SOUTH,BTN_EAST分别作为甲乙发球按钮;

4)SW0作为甲击球开关,SW3作为乙击球开关。击球的动作为ON-OFF。

(四)实验步骤:

1)画出游戏的状态转换图;

2)建立程序工程;

3)编写按键去抖进程

4)编写状态机进程;

5)下载程序,进行验证。

(五)实验代码:

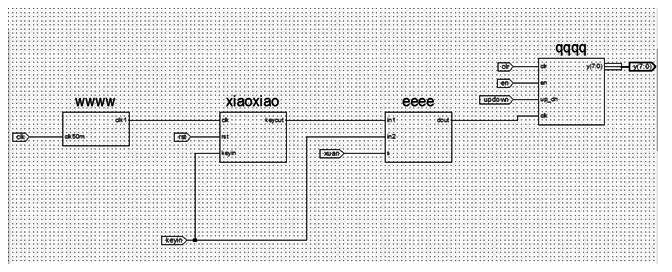

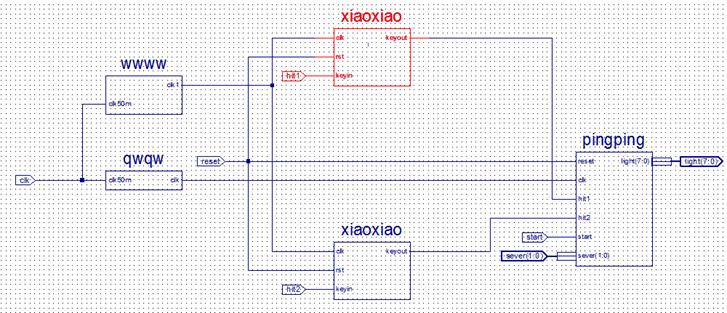

器件之间的连接图:

核心计数器件pingpang:

entity pingping is

Port ( reset : in STD_LOGIC;

clk : in STD_LOGIC;

hit1 : in STD_LOGIC;

hit2 : in STD_LOGIC;

sever : in STD_LOGIC_VECTOR (1 downto 0);

start : in STD_LOGIC;

light : out STD_LOGIC_VECTOR (7 downto 0));

end pingping;

architecture Behavioral of pingping is

type

pingpong is(waitserve,light1on,ballmoveto8,allow2hit,light8on,ballmoveto1,allow1hit);

signal state:pingpong;

signal i:integer range 0 to 9;

signal count1,count2:std_logic_vector(1 to 4):="0000";

signal count:std_logic_vector(1 to 8);

begin

main:process(clk,reset)

begin

if (reset='1') then

i<=0;count1<="0000";count2<="0000";

elsif (clk'event and clk='1')then

if(count1="0101"or count2="0101")then

count<=count1&count2;

i<=9;--结束时显示总比分

--count1<="0000";count2<="0000";

else

case state is

when waitserve=> --发球状态

if (start='1') then

case serve is

when "10"=> i<=1;state<=light1on;

when "01"=> i<=8;state<=light8on;

when "11"=> i<=0;

when others=> i<=0;

end case;

else

count<=count1&count2;i<=9; --暂停时显示当前比分

end if;

when light1on=> --第一盏灯亮状态

i<=2;

if hit2='1' then

i<=0;

count1<=count1+1;state<=waitserve;

else

state<=ballmoveto8;

end if;

when light8on=> --第八盏灯亮状态

i<=7;

if hit1='1' then

i<=0;

count2<=count2+1;state<=waitserve;

else

state<=ballmoveto1;

end if;

when ballmoveto1=> --球向甲方方向移动状态;

if hit1='1' then

i<=0;

count2<=count2+1;state<=waitserve;

elsif i=2 then i<=1;

state<=allow1hit;

else i<=i-1;

end if;

when ballmoveto8=> --球向乙方方向移动状态;

if hit2='1'then

i<=0;

count1<=count1+1;state<=waitserve;

elsif i=7 then i<=8;

state<=allow2hit;

else i<=i+1;

end if;

when allow1hit=> --允许甲方击球状态

if hit1='1' then i<=2;

state<=ballmoveto8;

else count2<=count2+1;i<=0;

state<=waitserve;

end if;

when allow2hit=> --允许乙方击球状态

if hit2='1' then i<=7;

state<=ballmoveto1;

else count1<=count1+1;i<=0;

state<=waitserve;

end if;

end case;

end if;

end if;

end process main;

led:process(clk)

begin

if(clk'event and clk='1')then

if(i=1) then light<="10011000" ;

elsif(i=2) then light<="01011000" ;

elsif(i=3) then light<="00111000" ;

elsif(i=4) then light<="00011000" ;

elsif(i=5) then light<="00011000" ;

elsif(i=6) then light<="00011100" ;

elsif(i=7) then light<="00011010" ;

elsif(i=8) then light<="00011001" ;

elsif(i=9) then light<=count;

elsif(i=0) then light<="00011000" ;

else null;

end if;

end if;

end process led;

end Behavioral;

2.5M分频器件qwqw:

entity qwqw is

Port ( clk50m : in STD_LOGIC;

clk : out STD_LOGIC);

end qwqw

architecture Behavioral of qwqw is

begin

process(clk50m)

variable n : INTEGER RANGE 0 to 50000000;

begin

if (clk50m'event and clk50m='1') then

n:=n+1;

if n<=25000000 then

clk<='0';

elsif n=50000000 then

n:=0;

else

clk<='1';

end if;

end if;

end process;

end Behavioral;

1HZ分频器件wwww:

entity wwww is

Port ( clk50m : in STD_LOGIC;

clk1 : out STD_LOGIC);

end wwww;

architecture Behavioral of wwww is

begin

process(clk50m)

variable n : INTEGER RANGE 0 to 20;

begin

if (clk50m'event and clk50m='1') then

n:=n+1;

if n<=10 then

clk1<='0';

elsif n=20 then

n:=0;

else

clk1<='1';

end if;

end if;

end process;

end Behavioral;

消抖器件xiaoxiao:

entity xiaoxiao is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

keyin : in STD_LOGIC;

keyout : out STD_LOGIC);

end xiaoxiao;

architecture Behavioral of xiaoxiao is

TYPE states IS (S0,S1,S2,S3,S4,S5);

SIGNAL next_state: states;

BEGIN

PROCESS (clk,rst,keyin)

variable count:integer:= 1000;

begin

IF (rst = '1') THEN

next_state <= s0;

ELSIF (clk'EVENT AND clk = '1')THEN

CASE next_state IS

when s0 =>

if (keyin = '1')then

next_state <= s1;

else null;

end if;

when s1=>

count := count -1;

if (count = 0) then

count := 1000;

next_state <= s2;

else null;

end if;

when s2=>

if (keyin='0') then

next_state <= s0;

else next_state <= s3;

end if;

when s3=>

if (keyin='0') then

next_state <= s0;

else next_state <= s4;

end if;

when s4=>

if (keyin='0') then

next_state <= s0;

else

next_state <= s5;

keyout <= '1';

end if;

when s5=>

if (keyin='0') then

keyout <= '0';

next_state <= s0;

end if;

end case;

end if;

End process;

end Behavioral;

约束性文件

NET "sever<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ;

NET "sever<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ;

NET "start" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ;

NET "hit1" LOC = "H13" | IOSTANDARD = LVTTL | PULLDOWN ;

NET "reset" LOC = "V4" | IOSTANDARD = LVTTL | PULLDOWN ;

NET "hit2" LOC = "K17" | IOSTANDARD = LVTTL | PULLDOWN ;

NET "light<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "light<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;

NET "clk" LOC = "C9" | IOSTANDARD = LVCMOS33 ;

实验感悟:

本次实验让我们熟悉了ISE软件的使用以及硬件描述语言的基础使用。学会了设计时序逻辑电路,状态机的设计以及相关流程。在这些实验中学会了分频器的设计,二选一的设计,消抖电路的设计。学会了FPGA开发板的简单使用。总之受益匪浅。