实验一:存储器设计

一、实验目的:

1、掌握随机存储器RAM的工作特性及使用方法;

2、掌握半导体存储器存储和读写数据的工作原理。

二、实验电路及其原理:

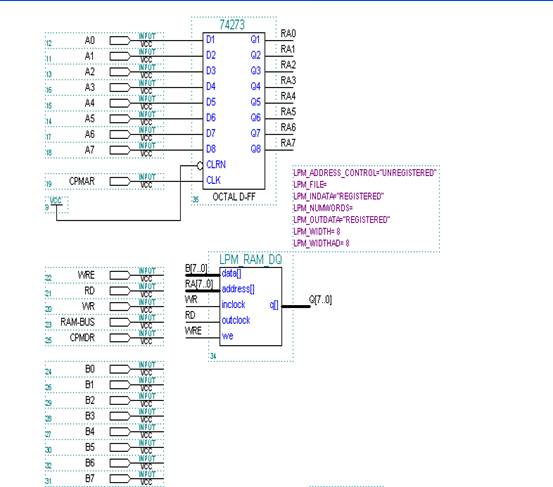

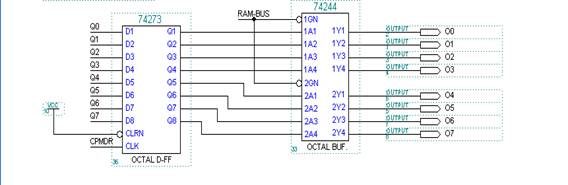

1.实验电路图

2、设计原理

存储器就是选择RAM地址,并对其操作存入数据,在需要时对其读取,并把数据输出到数据总线。实验思路大致为:

①第一个74273用来接收数据存放在RAM里的地址,即A0…7。当CPMAR有效时数据进入芯片。

②当WE=1,RD=0时,RAM进行写操作,接收存储在74273里的数传到地址端口,同时接收从B0…7输入的数据传到数据端口,把数据写到相应RAM里。

③当WE=0。RD=1时,RAM进行读操作,把对应存储单元的数据传到第二个74273,通过74273传到74244芯片输出。

三、实验步骤

1、根据实验原理在maxplus下连接电路图,对其进行编译。

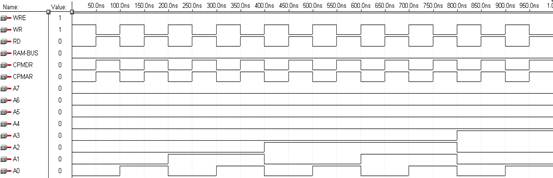

2、根据实验原理设计各个输入端的波形图,对其进行仿真模拟获得输出数据,仿真波形如下图。

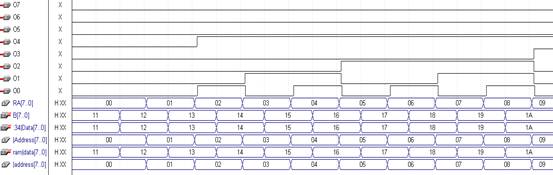

四、仿真图

说明:RAM在WRE=1时才工作,为方便起见WRE置为1;74244在RAM_BUS=0时工作,为方便起见RAM_BUS置为0。因CPMOR为一个周期变换一次,为了不浪费存储空间,A0为两倍的周期变换,A1为四周期变换,以此类推。存储的数据从11H起依次增加。

五、实验总结

通过本次实验熟练掌握MAX+PLUS软件,并运用该软件设计存储器,了解了存储器的结构设计和工作原理,并在理解的基础上自己设计了一个简单的存储器。在之后的波形仿真图模拟时,发现自己不能很好控制各个芯片的片选信号,不知道如何使各个芯片在合适的时间工作,在经过仔细分析后,设置了上图的波形图,保证每个存储单元都可以存到数,没有刚开始的浪费现象,数据在各个数据线之间的传输也正常,存储器的数据输出为两个周期输出一次(这是因为WR、RD为一个周期变换一次,在两个周期后才会读有效)。

通过此次实验对MAXPLUS有了初步了解,同时也对存储器的结构有了一定的了解,初步掌握了一些设置波形的技巧。

第二篇:静态存储器实验报告

静态随机存储器实验

组员:

组号:21组

日期:周二5、6节

【实验目的】

掌握静态随机存储器RAM工作特性及数据的读/写方法。

【实验设备】

实验仪一台、PC机一台(观察波形)

【实验原理】

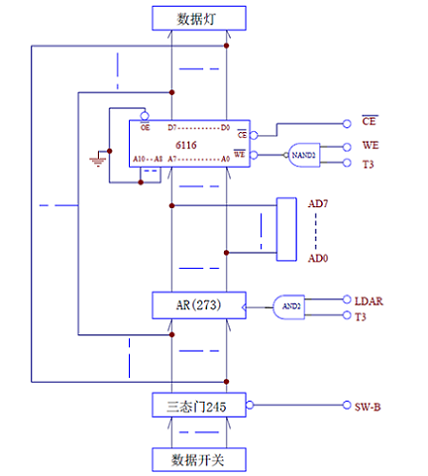

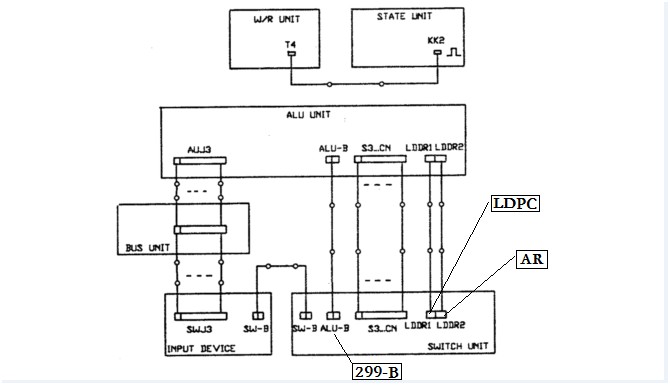

由一片6116(2K x 8)芯片、一片8位锁存器(74LS273)、一片8位三态门(74LS245)构成存储器原理图。

存储器实验原理图

由于存储器地址是由数据开关(input device)锁存在(273),存储器写数据也是由数据开关提供的,因此要分时给出地址和写数据。

因地址寄存器为8 位,所以接入6116 的地址为A7~A0,而高三位A8~A10 接地,所以其实际容量为256 字节。6116 有三个控制线:CE(片选线)、OE(读线)、WE(写线)。当片选有效(CE=0)时,OE=0 时进行读操作,WE=0 时进行写操作。本实验中将OE 常接地,在此情况下,当CE=0、WE=0 时进行读操作,CE=0、WE=1 时进行写操作,其写时间与T3 脉冲宽度一致。

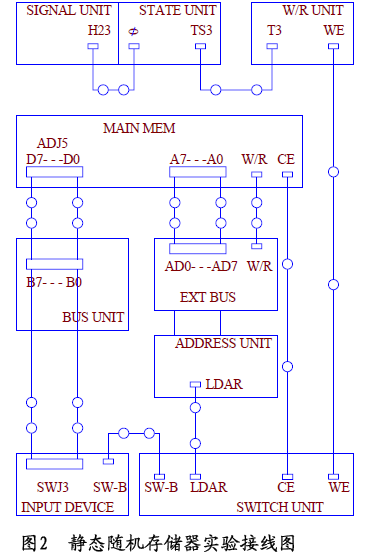

实验时将T3 脉冲接至实验板上时序电路模块的TS3 相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B 为低电平有效,LDAR 为高电平有效。

【实验步骤】

(1) 形成时钟脉冲信号T3。具体接线方法和操作步骤如下:

① 接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1 及W2 ,使H23 端输出实验所期望的频率及占空比的方波。

② 将时序电路模块(STATE UNIT)单元中的ф和信号源单元(SIGNAL UNIT)中的H23 排针相连。

③ 在时序电路模块中有两个二进制开关“STOP”和“STEP” 。将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则TS3端即输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3 输出实验要求的脉冲信号。当“STOP”开关置为“RUN”状态、“STEP”开关置为“STEP”状态时,每按动一次微动开关START,则T3 输出一个单脉冲,其脉冲宽度与连续方式相同。若用PC 联机软件中的示波器功能也能看到波形,可以代替真实示波器。实验测得的实验频率和周期分别为:f=104.49HZ,T=9.57ms

(2) 按图连接实验线路,仔细查线无误后接通电源。

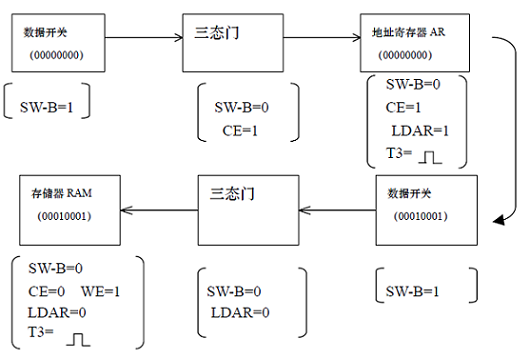

(3) 写存储器

给存储器的00、01、02、03、04 地址单元中分别写入数据11、12、13、14、15。

由上面的存储器实验原理图看出,由于数据和地址全由一个数据开关来给出,这就要分时地给出。下面的写存储器要分两个步骤,第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动START 产生T3 脉冲将地址打入到地址锁存器,第二步写数据,关掉地址锁存器门控信号(LDAR=0),打开存储器片选,使处于写状态(CE=0,WE=1),由开关给出此单元要写入的数据,按动START 产生T3 脉冲将数据写入到当前的地址单元中。写其它单元依次循环上述步骤。

写存储器流程如下:(以向00 号单元写入11 为例)

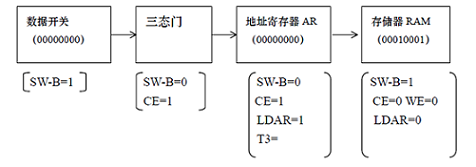

(4) 读存储器

依次读出第 00、01、02、03、04 号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。同写操作类似,读每个单元也需要两步,第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动START 产生T3 脉冲将地址打入到地址锁存器;第二步读存储器,关掉地址锁存器门控信号(LDAR=0),关掉数据开关三态门(SW-B=1),片选存储器,使它处于读状态(CE=0,WE=0),此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。读其它单元依次循环上述步骤。读存储器操作流程如下:(以从00 号单元读出1 1 数据为例。

(5)将存储单元内数据进行运算

在原来实验连线的基础上,按如下所示图连线。

其中,由于某些端口需要重复连接,所以为防止出现运算错误,借连接到其他端口上。,如:ALU-B借连接到299-B,LDDR1借连接到LDPC,LDDR2借连接到AR上。

① 进行读操作,读出03号地址中数据,然后置SW-B=1,ALU-B=1(即使299-B开关置1),LDAR=0,CE=0,LDDR1=1(LDPC=1),LDDR2=0( AR=0),按动微动开关KK2,则将03号地址中的数据输入保存到LDDR1中。

② 进行读操作,读出04号地址中数据,然后SW-B, ALU-B, LDAR, CE开关置数保持不变,LDDR1=0,LDDDR2=1,按动微动开关KK2,则将04号地址中数据输入保存到LDDR2。

③ SW-B=1,ALU-B=0,CE=1,再分别将S3、S2、S1、S0、M、Cn分别置为100101,则3、4号地址中数据进行加法运算。

④ 将结果送入8号单元,将LDDR1,LDDR2全置0,然后按动微动开关KK2,将加法运算的结果送入LDDR1中,接着进行写地址操作:CE=1,LDAR=1,SW-B=0,由开关给出地址(00001000),按动START键产生T3脉冲将地址打入地址锁存器。然后写入数据: SW-B=0,ALU-B=0,按动KK2开关,将LDDR1中的数据输出到总线上,然后关闭地址锁存器LDAR=0打开存储器片选,使CE=0,WE=1,按动START开关将总线上的数据写入到8号地址单元中。

【结果分析】

将3号单元与4号单元中的数进行加法运算以后,然后得出结果为00101001(29),而3号单元中的00010100(14)与4号单元中的00010101(15),进行加法运算的结果也的确为00101001(29),可知运算器运算结果正确。将数据送入8号单元后,进行读数据操作,8号单元中的数据也与结果相符,说明操作无误。

【出现问题】

由于线路在写、读数据和进行运算时,线路有共用现象,所以在进行写、读数据的时候要保持ALU-B关闭,在进行运算器运算时要关闭片选CE,否则会出现地址和数据混乱的情况,不能得到正确的输入和输出结果,在实验的时候要特别注意。