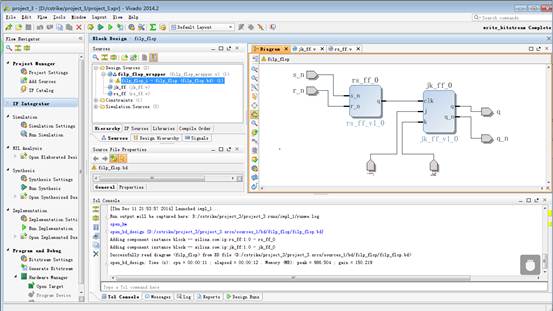

触发器功能测试

031210425 刘思何

一.实验目的

1.了解时钟脉冲的触发作用

2.掌握基本RS、JK、D触发器的逻辑功能、编写和使用

3.理解触发器所实现的状态转换功能

二.实验器件

开发板、计算机、vivado软件

三.实验内容

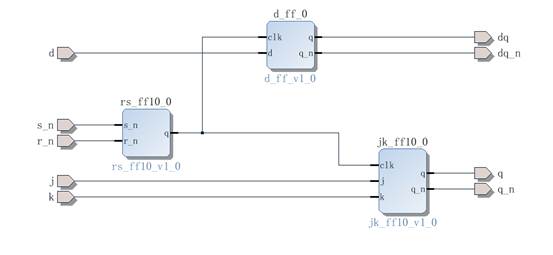

1.基本RS触发器的编写,验证并且生成IP核。连接电路图,在R,S两引脚输入不同的电平,测试输出端电平。

module rs_ff10(

input s_n,

input r_n,

output q

);

reg q;

always@*

begin

case({s_n,r_n})

2'b00 : q=1'bx;

2'b01 : q=1'b1;

2'b10 : q=1'b0;

2'b11 : q=q;

endcase

end

endmodule

2.JK触发器的编写,验证并且生成IP核。

module jk_ff10(

input clk,

output q,

output q_n,

input j,

input k

);

reg q;

always@(posedge clk)

begin

case({j,k})

2'b00 : q<=q;

2'b01 : q<=1'b0;

2'b10 : q<=1'b1;

2'b11 : q<=~q;

default : q<=1'bx;

endcase

end

assign q_n=~q;

endmodule

先将s_n、r_n置于10或01状态,然后将其置于11状态,给j、k一个初始激励信号,随后一上一下拨动s_n、r_n的开关,输入一个时钟信号,观察q、q_n灯的亮灭情况。

3.D触发器的编写,验证

如JK触发器一样进行验证。

四.实验数据及分析

R触发器

V16 (s_n) V17 (r_n) U16

0 0 不定

0 1 暗

1 0 亮

1 1 保持上个状态

JK触发器(上升沿触发)

R2T1(s_n,r_n) V16(J) V17(K) U16(q) E19(q_n)

11->10->01->11 0 1 暗 亮 置0

11->10->01->11 1 0 亮 暗 置1

11->10->01->11 0 0 亮 暗 保持

11->10->01->11 1 1 暗 亮 翻转

D触发器(上升沿触发)

R2T1 W13(d) V13(q) V14(q_n)

10->01 0 暗 亮

10->01 1 亮 暗

五.实验心得及体会

这是第三次在实验课上用开发板,对于VIVADO程序的操作已经比较熟练了,已经基本熟悉操作的流程.虽然是按照老师给的步骤一步一步做,但自己已经能理解很多选项的意思。本次试验是一开始先做的RS触发器,接着再做JK触发器,最后做D触发器,这样的步骤降低了实验的难度,并且让我们了更多的的方法,并且清晰的反映了各个触发器的联系,让我们对触发器的原理和工作方式有了更深入的了解。不用再去纠结于电路的连接,或是示波器的调节,给我们更多的时间去理解实验的原理。

第二篇:JK触发器的逻辑功能测试

实验三 JK触发器的逻辑功能测试

[实验目的]

1、学习触发器逻辑功能的测试方法。

2、掌握基本JK、D触发器的逻辑功能。

3、掌握JK触发器转换成D触发器的方法及D触发器的逻辑功能。

[主要仪器设备及耗材]数字电路实验板、74LS112芯片、74LS00芯片、数字万用表、数据线。

[实验基本原理]

触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

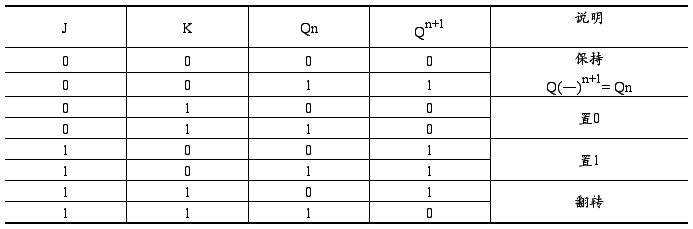

1、JK触发器

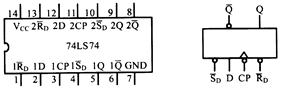

在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112(或74LS76)双JK触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符号如图1-1所示。

图1-1 74LS112双JK触发器引脚排列及逻辑符号

JK触发器的状态方程为

Qn+1=J +

+ Qn,

Qn,  =

= =1

=1

J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。Q与Q为两个互补输出端。通常把Q=0、Q=1的状态定为触发器“0”状态;而把Q=1、Q=0定为“1”状态。

JK触发器常被用来构成缓冲存储器、移位寄存器和计数器。

图1-1左图为双下降沿JK触发器74LS112的外引线排列图。

JK触发器的工作原理如下:

(1) 和

和 可将触发器置于额定状态1或0;之后应保持在高电平1。

可将触发器置于额定状态1或0;之后应保持在高电平1。

(2) =

= =1时,

=1时,

A、当J=K=0时,在CP脉冲的作用下触发器保持原状态,即Qn+1=Qn;

B、当J=0,K=1时,在CP脉冲的作用下,触发器置“0”, 即Qn+1=0;

C、当J=1,K=0时,在CP脉冲的作用下,触发器置“1”, 即Qn+1=1;

D、当J=K=1时,在CP脉冲的作用下,触发器状态翻转,即Qn+1=

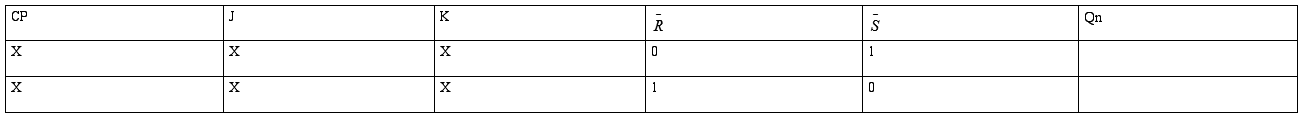

下降沿触发JK触发器的功能如表1-1。

表1-1

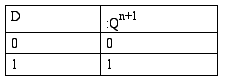

2、D触发器

在输入信号为单端的情况下,D触发器用起来最为方便,其状态方程为Qn+1=Dn,其输出状态的更新发生在CP脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D端的状态。D触发器的应用很广,可用作数字信号的寄存、移位寄存、分频和波形发生等。有很多种型号可供各种需要而选用,如双D 74LS74、四D 74LS175、六D 74LS175等。表1-2为其真值表。

表1-2

图1-2为双D 74LS74的引脚排列及逻辑符号。

图1-2 74LS74引脚排列及逻辑符号

[实验步骤]

1、集成JK触发器逻辑功能测试

(1)异步置位及复位功能的测试

表1-3

将J、K、CP端开路,将 、

、 端分别接到数据开关相应的插孔,在

端分别接到数据开关相应的插孔,在 、

、 为表1-4中情况时,观察Q端显示的高低电平,并转换成逻辑状态填入表1-3中,用万用表测试Q端显示的电位加以验证。

为表1-4中情况时,观察Q端显示的高低电平,并转换成逻辑状态填入表1-3中,用万用表测试Q端显示的电位加以验证。

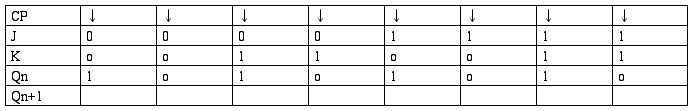

2、测试双JK触发器74LS112(或74LS76)逻辑功能

(1)  、

、 端仍如上连接不变,并将

端仍如上连接不变,并将 、

、 端置高电位,将J、K端分别接到数据开关的其它插孔、将CP端接至单脉冲的插孔。先将触发器置0或置1,按表1-4的要求改变CP、J、K的状态,观察Qn及Qn+1的显示,并转换成逻辑状态填入表1-5中。注意观察触发器状态更新是否发生在CP脉冲的下降沿(即CP由1→0)。从右至左观察最好。

端置高电位,将J、K端分别接到数据开关的其它插孔、将CP端接至单脉冲的插孔。先将触发器置0或置1,按表1-4的要求改变CP、J、K的状态,观察Qn及Qn+1的显示,并转换成逻辑状态填入表1-5中。注意观察触发器状态更新是否发生在CP脉冲的下降沿(即CP由1→0)。从右至左观察最好。

表1-4

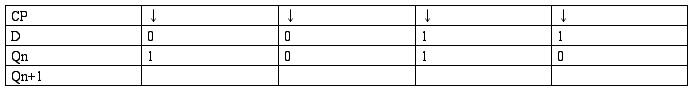

(3)将J-K触发器转化成D触发器。

将J-K触发器转化成D触发器,即K= 。测试上述D触发器的逻辑功能。将

。测试上述D触发器的逻辑功能。将 、

、 和D分别接到数据开关的插孔、将CP端接至单脉冲的插孔,按表1-5的要求提供数据,观察Qn、 Qn+1端的显示,并转换成逻辑状态填入表1-5中。

和D分别接到数据开关的插孔、将CP端接至单脉冲的插孔,按表1-5的要求提供数据,观察Qn、 Qn+1端的显示,并转换成逻辑状态填入表1-5中。

表1-5

[实验数据及处理结果]

1、列表整理各类触发器的逻辑功能。

2、根据实验结果,总结触发器的逻辑功能和特点。