EDA技术及应用

—Verilog HDL

实 验 报 告

学院:电气与信息工程学院

班级:电子信息1203

指导老师:谭会生

姓名: 李炎

学号:12401720504

实验一 数字秒表的设计

一、 实验类型:综合性实验

二、实验仪器设备与工具软件

1.PC机(要求内存在256M以上);

2.EDA实验开发系统;

3.Quartus II软件

三、实验目的与任务

1.实验目的:(1)熟悉Quartus II/ISE Design suite/ispLEVER软件的基本使用方法

(2)熟悉EDA实验开发系统(B-ICE-EDA实验开发系统)的使用;

(3)熟悉Verilog HDL过程区块语句、if条件语句和元件实例化语句的综合使用。

(4)熟悉计数器、分频器等Verilog HDL基本逻辑电路的综合设计应用,掌握程序仿真是根据实际情况进行有关参数的调整方法。

2.实验任务:用Verilog HDL设计一个计时范围为0.01秒~1小时的数字秒表,并用Quartus II进行调试和验证,熟悉Verilog HDL程序的基本设计,熟悉Quartus II的设计输入、设计编译、仿真验证、时序分析、器件编程等基本操作。

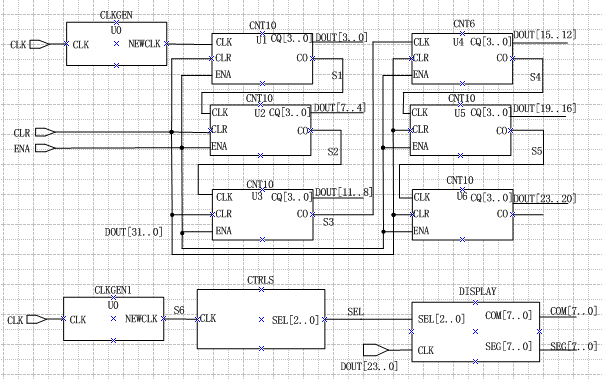

四、实验基本原理与电路原理图

设计一个计时范围为0.01秒~1小时的数字秒表,首先需要获得一个比较精确的计时基准信号,这里是周期为1/100秒的计时脉冲。其次,除了对每一计数器需设置清零信号输入外,还需在六个计数器设置时钟使能信号,即计时允许信号,以便作为秒表的计时起、停控制开关。因此数字秒表可由一个分频器、四个十进制计数器(分别按1/100秒、1/10秒、1秒、1分的周期进行计数)以及两个六进制计数器(分别按10秒、10分的周期进行计数)组成,如图1.1所示。六个计数器中的每一计数器的4位输出,通过外设的BCD译码器输出显示。图1.1中六个4位二进制计数输出的最小显示值分别为:dout[3:0] 1/100秒、dout[7:4]

1/100秒、dout[7:4] 1/10秒、dout[11:8]

1/10秒、dout[11:8] 1秒、dout[15:12]

1秒、dout[15:12] 10秒、dout[19:16]

10秒、dout[19:16] 1分、dout[23:20]

1分、dout[23:20] 10分。 实验原理图如下图1.1

10分。 实验原理图如下图1.1

图1.1 数字秒表电路逻辑图

五、实验步骤

1、Verilog HDL源程序

1) ?3 MHz→100 Hz分频器的源程序clkgen.v

module clkgen(clk, newclk);

input clk;

output newclk;

reg newclk;

integer cnt=0;

always @(posedge clk)

begin

//if(cnt1<29999) //实际系统分频值

if(cnt < 29) //仿真时的分频值

begin

newclk <= 1'b0;

cnt = cnt + 1;

end

else

begin

newclk <= 1'b1;

cnt = 0;

end

end

endmodule

2) 六进制计数器的源程序cnt6.v

module cnt6(clk,clr,ena,cq,co);

input clk, clr, ena;

output [3:0] cq;

output co;

reg [3:0] cnt;

reg co;

always @(posedge clk or posedge clr)

begin

if (clr)

cnt <= 4'b0;

else

if (ena)

if (cnt==4'h5)

cnt <= 4'h0;

else

cnt <= cnt + 1;

end

assign cq = cnt;

always @(posedge clk )

begin

if (cnt==4'h5)

co = 4'h1;

else

co= 4'h0;

end

endmodule

3)十进制计数器源程序cnt10.v

module cnt6(clk,clr,ena,cq,co);

input clk, clr, ena;

output [3:0] cq;

output co;

reg [3:0] cnt;

reg co;

always @(posedge clk or posedge clr)

begin

if (clr)

cnt <= 4'b0;

else

if (ena)

if (cnt==4'h5)

cnt <= 4'h0;

else

cnt <= cnt + 1;

end

assign cq = cnt;

always @(posedge clk )

begin

if (cnt==4'h5)

co = 4'h1;

else

co= 4'h0;

end

endmodule

4)数字秒表的源程序times.v

module times(clk, clr, ena, dout);

input clk, clr, ena;

output [23:0] dout;

wire clk, clr, ena;

wire [23:0] dout;

wire s0, s1, s2, s3, s4, s5, s6, s7, s8;

clkgen u0 (.clk(clk), .newclk(s0));

cnt10 u1 ( .clk(s0), .clr(clr),.ena(ena), .cq (dout[3:0]),.co (s1));

cnt10 u2 ( .clk(s1), .clr(clr),.ena(ena), .cq (dout[7:4]),.co (s2));

cnt10 u3 ( .clk(s2), .clr(clr),.ena(ena), .cq (dout[11:8]),.co (s3));

cnt6 u4 ( .clk(s3), .clr(clr),.ena(ena), .cq (dout[15:12]),.co (s4));

cnt10 u5 ( .clk(s4), .clr(clr),.ena(ena), .cq (dout[19:16]),.co (s5));

cnt6 u6 ( .clk(s5), .clr(clr),.ena(ena), .cq (dout[23:20]),.co ( ));

endmodule

2、程序仿真结果

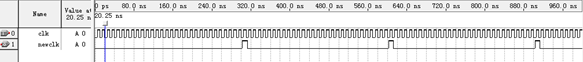

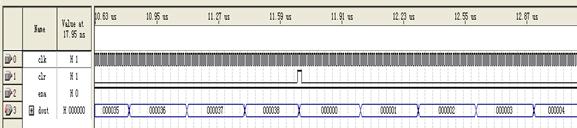

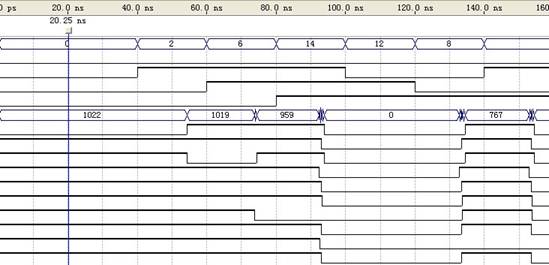

1)下图1.3和14分别为使用Quartus II 8.0对clkgen和times的时序仿真的结果

图1.3clkgen的时序仿真结果图(分频常数改为30

图1.4times的时序仿真结果

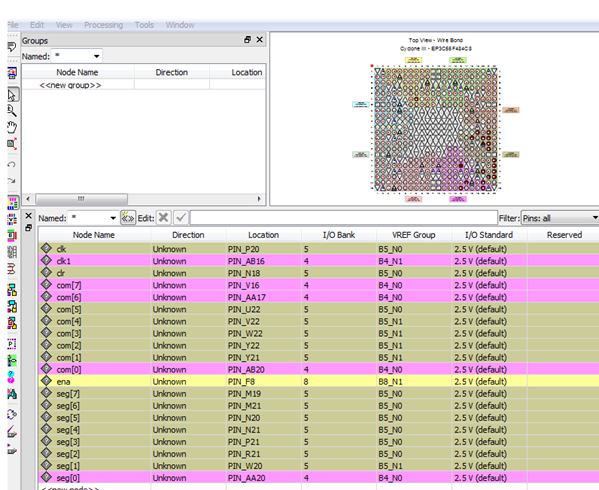

3、管脚锁定

图1.5管脚锁定

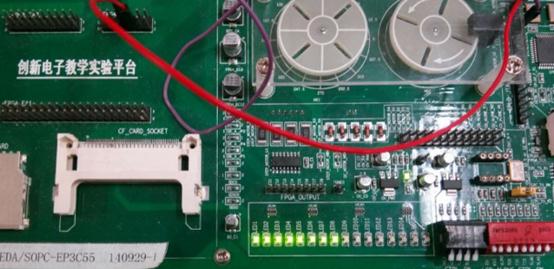

4.硬件逻辑验证

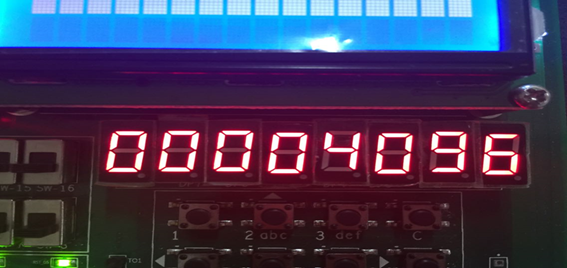

若使用GW48-CK EDA实验开发系统进行硬件逻辑验证,可选择实验电路结构图1.1和图1.4锁定。时钟信号clk可接CLOCK0,计数清零信号接键3,计数使能信号接键4,数码管1~数码管6分别显示以1/100 秒、1/10 秒、1 秒、10 秒、1 分、10分为计时基准的计数值。

进行硬件验证时方法如下:选择实验模式0,时钟信号clk与CLOCK0信号组中的3 MHz信号相接,键3和键4分别为计数清零信号和计数使能信号,计数开始后时间显示在六个数码管上。

六、实验总结

VerilogHDL版实验中,编写程序要特别细心,少了一个分号都会导致程序的语法错误,从而无法进行下面的实验步骤,还要注意文件的存放位置与文件名,以便容易查找,在硬件验证时需要修改相关参数,分频值需要修改为29999,通过本次实验对verilogHDL语言程序编写有了进一步的掌握。

实验二 SOPC设计的基本应用

一、实验类型:研究探索性实验

二、实验目的与任务

1.实验目的:熟悉NIOS II嵌入式处理器的设计过程和方法,熟悉QuartusII的SOPC开发

2.实验任务:通过创建一个Quartus II工程,创建Quartus II模块,将图标添加到BDF文件中,编译工程设计文件,配置FPGA等步骤完成一个Nios II嵌入式处理器的设计,再通过完成相应的软件实现,开发一个以Nios II为嵌入式处理器的SOPC

三、实验仪器设备与工具软件

1.PC机(要求内存在256M以上);

2.EDA实验开发系统(含Altera Nios Cyclone适配板);

3.Quartus II软件(含Nios II)。

四、实验基本原理

1.硬件开发流程

(1)用SOPC Builder系统综合软件来选取合适的CPU、存储器以及外围器件。

(2)使用Quartus II软件来选取具体的Altera可编程器件系列,并对SOPC Builder生成的HDL设计文件进行布局仿真;再使用Quartus II软件来选取目标器件并对Nios II系统上的各种I/O口进行分配管脚,另外还要根据硬件编译选项或时序约束的设置。在编译的过程中,Quartus II从HDL源文件综合生成一个适合目标器件的网表。最后,生成配置文件。

(3)使用Quartus II编程器和Altera下载电缆,将配置文件(用户定制的NIOS II处理器系统的硬件设计)下载到开发板上。当校验完当前硬件设计后,软件开发者就可以把此开发板作为软件开发的初期硬件平台进行软件功能的开发验证了。

2.软件设计流程

(1)在用SOPC Builder系统集成软件进行硬件设计的同时,就可以开始编写独立于器件的C/C++软件,比如算法或控制程序。用户可以使用现成的软件库和开放的操作系统内核来加快开发进程。

(2)在Nios II IDE中建立新的软件工程时。IDE会根据SOPC Builder对系统的硬件配置自动生成一个定制HAL(硬件抽象层)系统库。这个库能为程序和底层硬件的通信提供借口驱动程序,它类似于创建Nios II系统时SOPC Builder生成的SDK。

(3)使用Nios II IDE对软件工程进行编译、调试。

(4)将硬件设计下载到开发板上后,就可以将软件下载到开发板上并在硬件上运行。

五、实验内容

1、硬件的设计

1)通过创建一个Quartus II工程,创建Quartus II模块,

2)添加一个NIOS2软核

3)添加 NIOS II 处理器

4) 添加外设

a添加符合JTAG 接口标准的Debug接口 b 添加System ID

c 添加系统时钟 d 添加FLASH

f 添加SDRAM g添加革新公司的IP 核SRAM (sram_256x16bit)

h 添加一个Avalon Tri-state Bridge i 添加非易失性配置芯片

j 添加button I/O输入端口 k添加LED_PIO输出端口

l添加 RS232串行口 m 进行Aalon 数据线的连接

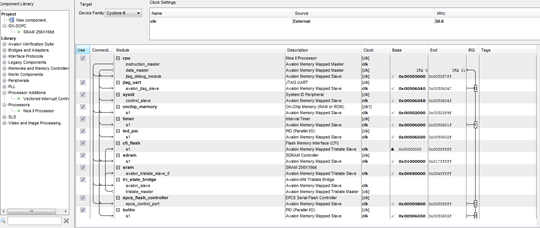

图2.1 Nios Ⅱ系统配置及其地址映射表

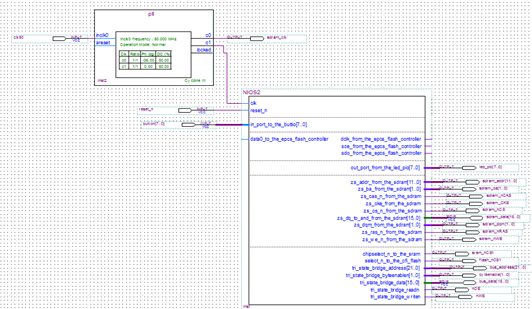

图2.2 完成原理图编辑后的结果

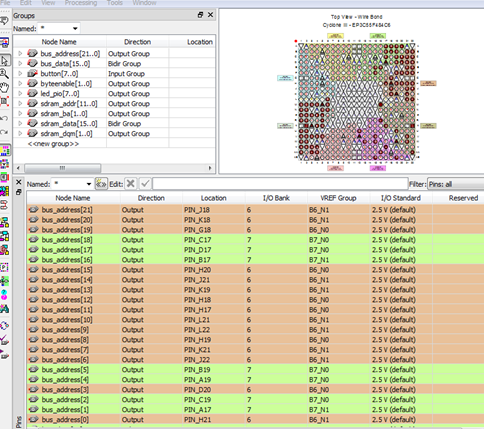

5)配置FPGA,进行管脚锁定

图2.3管脚锁定

6)下载到B-ICE-EDA/SOPC实验开发平台中

2、软件的设计

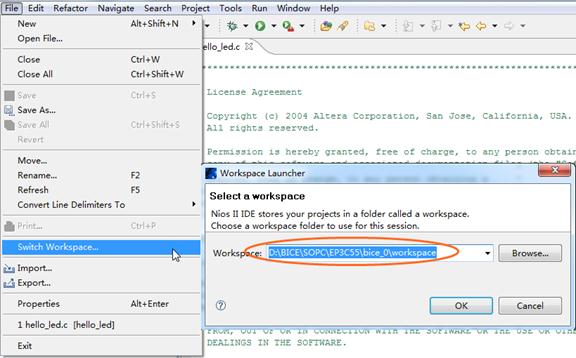

1)打开Nios II 10.1 IDE ,用它打开已编程好的软件

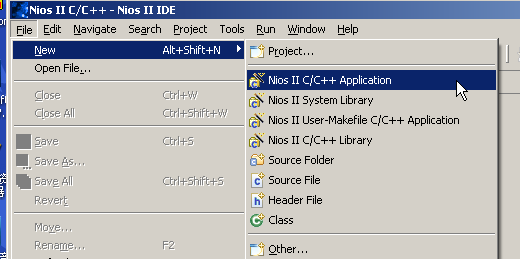

2)选择File>New>Nios II C/C++ Application:在Select Project Template 模板中,选择Blank Project Select Target Hardware 硬件目标板,选择bice_0.pdf应用程序工程名输入 LED。

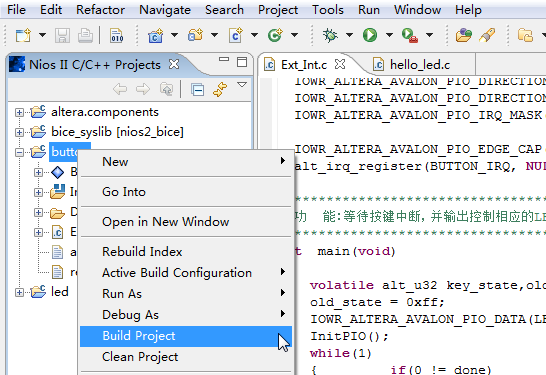

3)编译工程,选中工程点击右键选择Build Project。

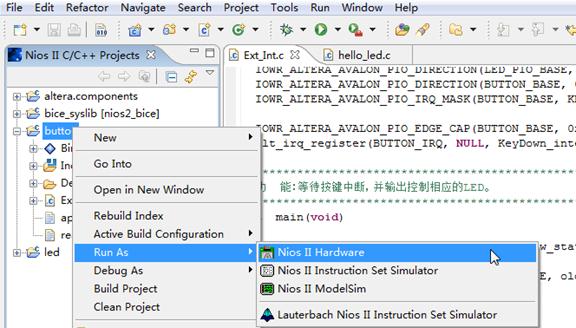

4)编译完成,选择Buttong工程,点击鼠标右键,运行Run As-》Nios II Hardware

4)编译完成,选择Buttong工程,点击鼠标右键,运行Run As-》Nios II Hardware

(5)调试程序。

(6)将程序下载到Flash中,硬件参考问价夹中的视频。

六、实验总结

通过本次实验对sopc开发的基本步骤有了进一步的了解,虽然基于Nios II的SOPC系统的设计比较复杂,但经过老师的指导和查阅书籍,最终顺利完成了硬件部分,但是软件部分始终调试不出来,最后老师也没做要求了,但是自己还是要思考原因,深入学习eda的知识。

第二篇:EDA实验报告 (4)

实验四 VHDL组合逻辑电路设计

一 实验目的:

在学习了VHDL语言的语句,语法以及利用VHDL语言设计逻辑电路的基本方法之后,进行本次试验。通过本次试验,使学生了解常见组合逻辑电路的VHDL描述,并且通过仿真,深入了解一种组合逻辑电路的功能和特性。通过编辑VHDL程序熟悉VHDL语言结构和词法元素的规则,了解常见的语法错误,学习利用QUARTUSII文本编辑器对VHDL语言程序进行编译,调试,并利用波形编辑器进行逻辑关系验证。

二 实验内容:

本实验是一个设计型实验,利用所学VHDL语言,设计实现8421BCD码十进制转换。通过本次试验,使学生能够熟练使用VHDL语言描述设计简单的组合逻辑电路。进一步掌握VHDL描述的结构以及语法规则。

三 实验仪器:

1.PC机一台 2.QUARTUSII软件 3.EDA实验箱

四 实验原理:

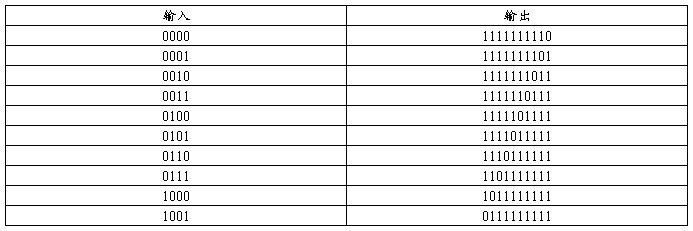

8421BCD码—十进制转换的逻辑关系如下表所示。

五 实验步骤:

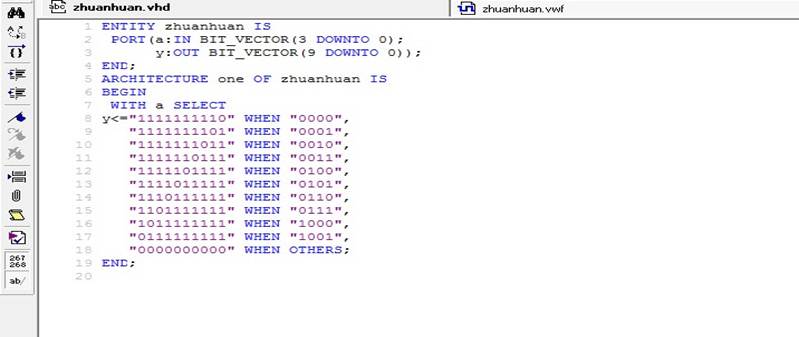

1.编译得到如图4.1所示。

图4.1

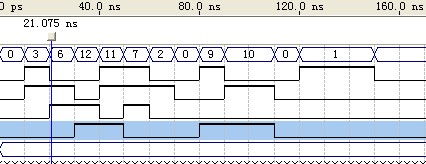

2.仿真得到如4.2所示波形。

图4.2

六 实验总结

。通过本次试验,加深了我对常见组合逻辑电路的VHDL描述的了解,并且通过仿真,深入了解一种组合逻辑电路的功能和特性。