第二篇:实验七 100进制计数器设计

实验七 100进制计数器设计实验报告

一、实验要求

1、GW48实验箱;

2、用层次设计方式设计100进制计数器,并进行编译、仿真、下载;

3、总结实验步骤和实验结果。

二、实验内容

在数字系统中,计数器不仅能记录输入时钟脉冲的个数,还可以实现分频、定时、产生节拍脉冲和脉冲序列等。常用的计数器包括加法计数器、减法计数器和加减可逆计数器。

用层次化设计方法设计一个可控的100进制计数器的计数、译码电路,

(1)计数器的时钟输入信号为1s

(2)计数器的功能是从0到99计数,输出显示采用8421BCD码的编码方式。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用下(如下表所示),计数器具有复位、增或减计数、暂停功能。

这里作为的层次设计方法是指“Top-Down”的设计方法,它能够把复杂的设计分解为许多简单的逻辑来实现。本例中可分为两个子模块,一个是计数模块,一个是译码模块,由顶层模块将两个子模块组合起来。

多层次结构电路的描述既可以采用文本方式,也可以用图形和文本混合设计的方式,这里我们采用文本方式。

(1)计数器模块设计

Module zdws(q,clk,clr,plus,minus);

inputclk,clr,plus,minus;

output[7:0]q;

reg[7:0]q;

always@(posedgeclk or negedgeclr)

begin

if(!clr) q<=8'h00;

else

case({plus,minus})

2'b10:begin //递增

if(q[3:0]==4'd9)

begin

q[3:0]<=4'd0;

if(q[7:4]==9)q[7:4]=4'd0;

else q[7:4]<=q[7:4]+1'b1;

end

else q[3:0]<=q[3:0]+1'b1;

end

2'b01:begin //递减

if(q[3:0]==4'd0)

begin

q[3:0]<=4'd9;

if(q[7:4]==0)q[7:4]=4'd9;

else q[7:4]<=q[7:4]-1'b1;

end

else q[3:0]<=q[3:0]-1'b1;

end

2'b11:q<=q; //暂停

default:q<=4'bx;

endcase

end

endmodule

(2)译码电路模块

module BCD(in,out);

output[6:0]out;

input[3:0]in;

reg[6:0]out;

always@(in)

begin

case(in)

4'd0:out=7'b1111110;

4'd1:out=7'b0110000;

4'd2:out=7'b1101101;

4'd3:out=7'b1111001;

4'd4:out=7'b0110011;

4'd5:out=7'b1011011;

4'd6:out=7'b1011111;

4'd7:out=7'b1110000;

4'd8:out=7'b1111111;

4'd9:out=7'b1111011;

default:out=7'bx;

endcase

end

endmodule

(3)顶层电路模块

module top(out1,out2,clk,clr,plus,minus);

output[6:0]out1,out2;

inputclk,clr,plus,minus;

wire[7:0]qout;

zdws u1(qout,clk,clr,plus,minus);

//模块调用,端口采用位置对应调用法

bcd u2(qout[7:4],out1);

bcd u3(qout[3:0],out2);

endmodule

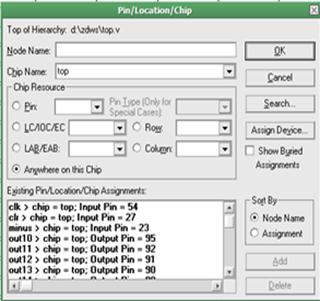

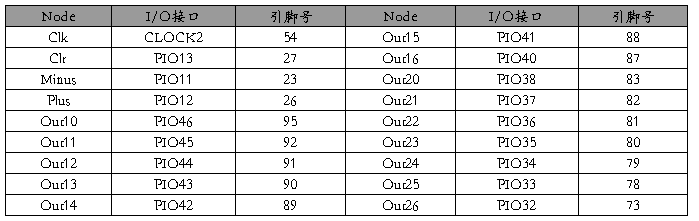

硬件逻辑验证:选择实验电路结构图NO.6.可取实验电路结构图的PIO40~PIO46接out1[6..0],PIO32~PIO38接out2[6..0],CLOCK0接clk,PIO13接clr(键8),PIO12接plus(键7),PIO11接minus(键6)。

三、实验步骤

1、实验源程序

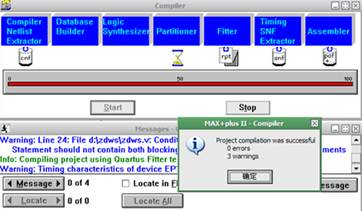

2、编译

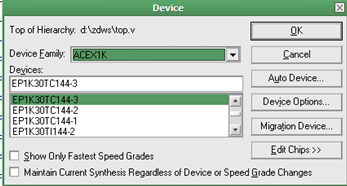

3、芯片选择及仿真

1)芯片选择

2)仿真结果

BCD模块仿真:

top模块仿真:

通过仿真,知结果正确,可以进行引脚锁定及下载

4、选择电路模式并引脚锁定

1)电路模式NO.6

2)引脚锁定

5、下载

成功!实验完成

四、实验结果

选择实验电路结构图NO.6.可取实验电路结构图的PIO40~PIO46接out1[6..0],PIO32~PIO38接out2[6..0],CLOCK0接clk,PIO13接clr(键8),PIO12接plus(键7),PIO11接minus(键6)。

通过编译、仿真、硬件逻辑验证,实验结果正确。