西安邮电大学

Verilog HDL大作业报告书

实验一 异或门设计

一、实验目的

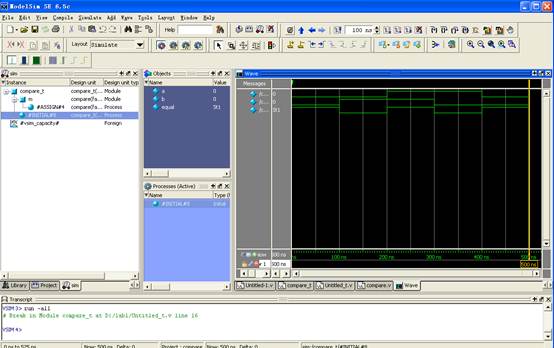

(1)熟悉Modelsim 软件

(2)掌握Modelsim 软件的编译、仿真方法

(3)熟练运用Modelsim 软件进行HDL 程序设计开发

二、实验内容

my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z=x’y+xy’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真

1、实验要求

用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤

1、建立工程

2、添加文件到工程

3、编译文件

4、查看编译后的设计单元

5、将信号加入波形窗口

6、运行仿真

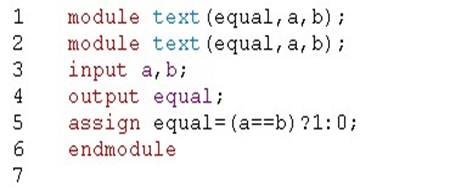

实验描述如下:

module my_and(a_out,a1,a2);

output a_out;

input a1,a2;

wire s1;

nand(s1,a1,a2);

nand(a_out,s1,1'b1);

endmodule

module my_not(n_out,b);

output n_out;

input b;

nand(n_out,b,1'b1);

…… …… 余下全文

![Y_]883GK0(9{6E75(]PGDIX](https://upload2.fanwen118.com/wk001/4084888/4084888_img_002.jpg)