大连理工大学城市学院

数字电路与系统课程设计

设计题目:数字频率计

学 院:电子与自动化学院

专 业: 自动化

学 生: 揣智涵

同 组 人: 王晓宁 周英茹

指导教师: 于海霞

完成日期: 20##年3月26日

目 录

第一章 设计任务

1.1项目名称

1.2项目设计说明

1.2.1设计任务和要求

1.2.2进度安排

1.3项目总体功能模块图

第二章 需求分析

2.1问题基本描述

(要求分析得出整个系统流程图)

2.2系统模块分解及各模块功能的基本要求

第三章 设计原理

3.1 设计原理

3.2 MAXPLUSII介绍

第四章 系统功能模块设计

4.1 FEN模块

4.1.1 FEN模块流程图

4.1.2 输入输出引脚及其功能说明

4.1.3 程序代码实现

4.2 SEL模块

4.2.1 SEL模块流程图

4.2.2输入输出引脚及其功能说明

…… …… 余下全文

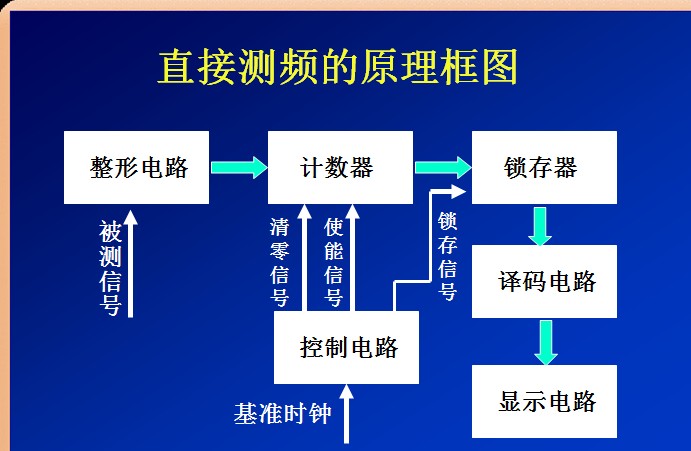

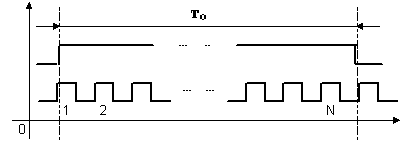

如左图所示为数字频率计测量频率的原理图。已知给定标准时钟脉冲高电平时间

如左图所示为数字频率计测量频率的原理图。已知给定标准时钟脉冲高电平时间 ,将此高电平信号作为计数器闸门电平,通过计数器得到

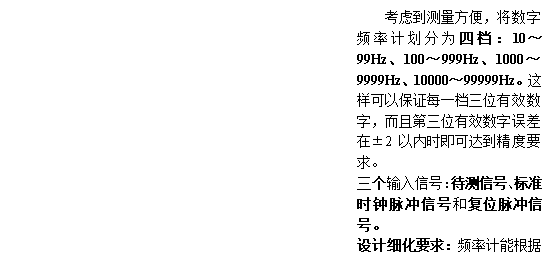

,将此高电平信号作为计数器闸门电平,通过计数器得到 。由图示可以看出,一个闸门电平时间内计数的最大误差为N±1,为保证误差要求取N≥100。经计算,四档的闸门电平时间

。由图示可以看出,一个闸门电平时间内计数的最大误差为N±1,为保证误差要求取N≥100。经计算,四档的闸门电平时间

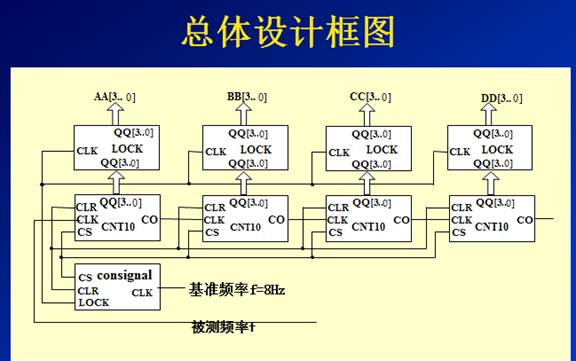

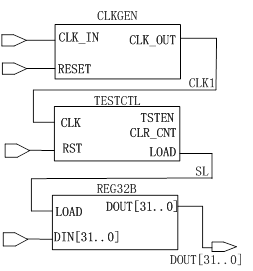

图 4.2 dtFREQ电路原理图

图 4.2 dtFREQ电路原理图