组合逻辑电路的设计与调试

一、 实验目的

1、掌握用门电路设计组合逻辑电路的方法。

2、掌握组合逻辑电路的调试方法。

二、 实验器材

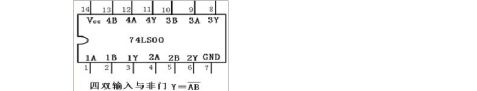

数字电路实验箱一台、74LS00若干

三、 实验内容

1、用与非门实现散人多数表决器电路

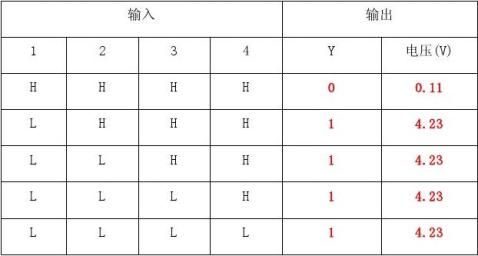

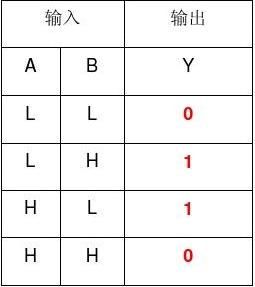

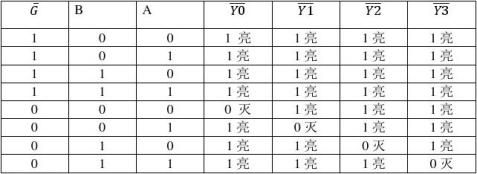

(1) 真值表

(2) 表达式化简及变形

(3) 逻辑图

2、用与非门实现

(1)真值表

(2)表达式化简及变形

(3)逻辑图

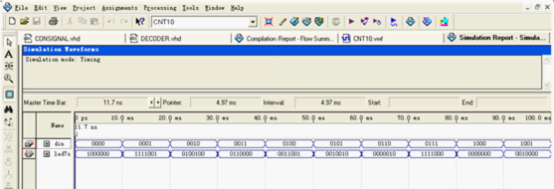

译码器应用电路的设计与测试

一、实验目的

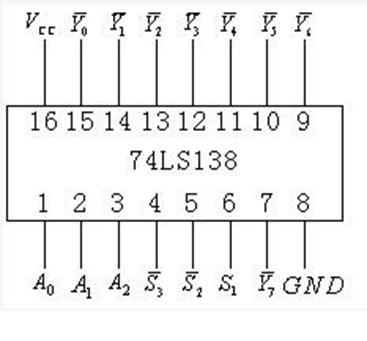

1、熟悉集成译码器的性能和使用方法

2、学会使用二进制译码器实现组合逻辑电路的方法

二、实验器材

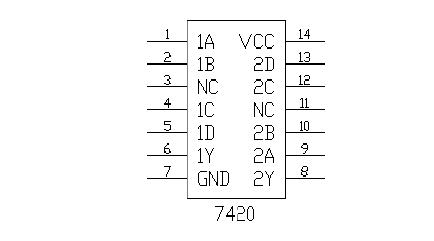

数字电路实验箱一台、74LS138一片、74LS20一片

三、实验内容

1、用74LS138及74LS20实现三人多数表决器电路

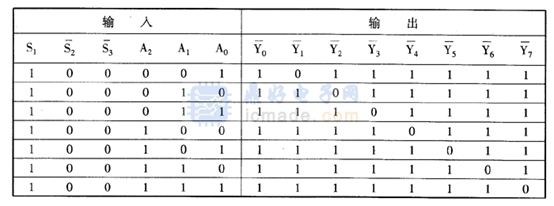

(1)真值表

(2)表达式转换

(3)逻辑图

2、用74LS138及74LS20实现

(1)表达式转换

(2)逻辑图

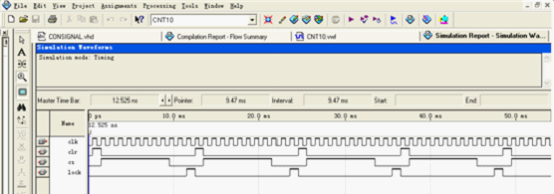

数据选择器的设计与调试

一、实验目的

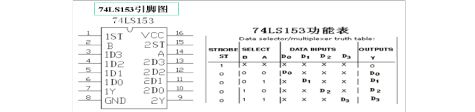

1、熟悉数据选择器的性能及使用方法

2、学会使用数据选择器进行逻辑设计的方法

二、实验器材

数字电路实验箱一台、74LS151一片

三、实验内容

1、用74LS151实现三人多数表决器

(1)真值表

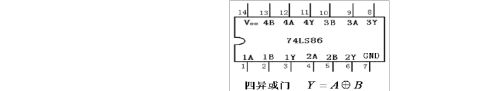

(2)比较卡诺图求出

(3)逻辑图

2、用74LS151实现

(1)比较卡诺图求出

(2)逻辑图

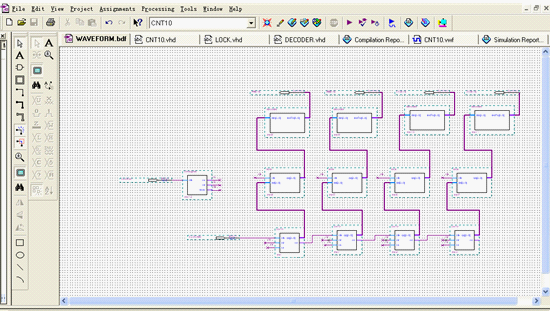

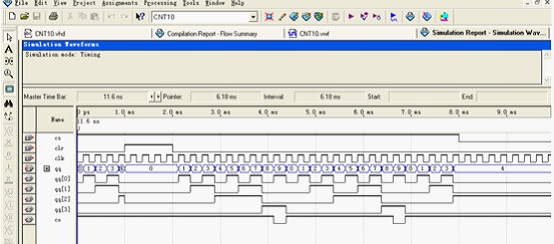

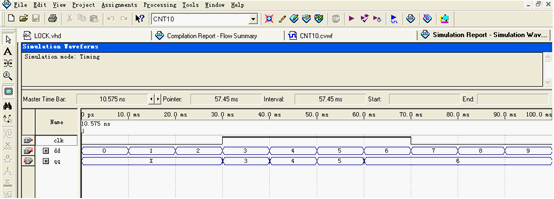

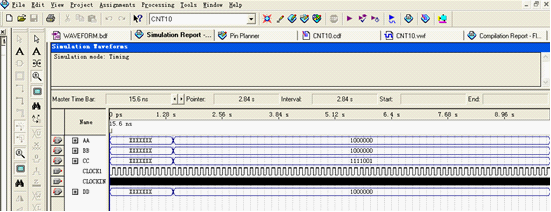

N进制计数器的设计与测试

一、实验目的

1、掌握集成技术器的测试方法

…… …… 余下全文