DSP设计报告

题目CPU内部AD转换

学 院: 物理与信息工程学院

专 业: 测 控

姓 名: 程啟忠

学 号: 112207202139

指导老师: 漆为民

20##年1月2日

目 录

一:设计目的…………………………………..........…………3

二:实验设备..……………………………………………3

三:实验原理.……………………………………………...……4

四:实验说明..…………………………………………………7

五:实验数据…………………………………..……………10

六:心得与体会……………………………………………11

A/D实验(CPU)

一:设计目的

1. 熟悉CPU内部AD转换的基本原理。

2. 掌握TMS320F2812的内部ADC功能模块的指标和常用方法。

二、实验设备

计算机,CCS3.3版本软件,DSP仿真器,E300实验箱,2812CPU板(新的),信号线,示波器

三、实验原理与任务

1、实验原理:

TMS320F2812DSP自带16路12位单极性ADC转换器,并且内置双采样保持器。快速转换时间运行在25MHz。16个通道可配置为两个独立的8通道模块以便为事件管理器A和B服务。两个独立的8通道模块可以级联组成一个16通道模块。虽然有多个输入通道和两个序列器,但是ADC模块只有一个转换器。

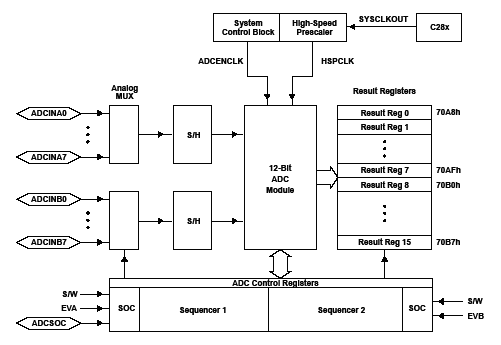

下图给出了F2812的ADC模块框图。

两个8通道模块具有一对系列转换和自动序列化的能力,通过模拟多路复用器,每个模块都可以选择可用的8个通道中的任何一个通道。在级联模式下,自动序列发生器可作为一个单一的16通道序列发生器。在每个序列发生器上,一旦转换结束,已选择的通道值就保存在各个通道的结果寄存器ADCRESULT中。

自动序列化允许系统对同一通道转换多次,允许用户执行过采样算法。这较传统的单一采样转换结果增加了更多的解决方案。

输入模拟电压的数字值为:

数字值=4095×(输入模拟电压值)/3

多触发源启动序列转换(SOC)包括:

●S/W:软件直接启动;

●EVA/B:事件管理器A/B(EVA/B内有多个事件源);

●S/W:外部引脚。

具体的原理和相关内容,请读者参阅相关的文档和书籍。

2、实验任务一:

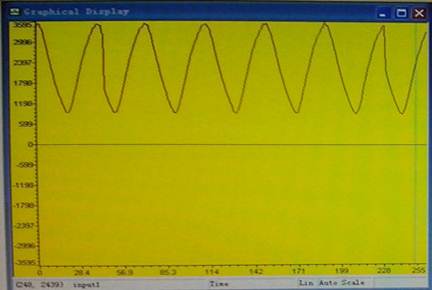

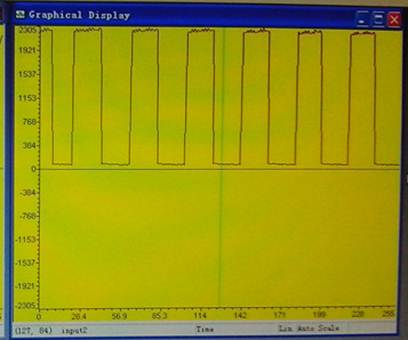

通过信号发生器,产生方波和正玄波,由DSP自带AD将数据采集到DSP内,经过CCS自带的graph功能,运行程序,观察测试结果。

3、程序框图

4、主要程序:

#include "DSP281x_Device.h" // DSP281x Headerfile Include File

#include "DSP281x_Examples.h" // DSP281x Examples Include File

interrupt void adc_isr(void);

Uint16 LoopCount;

Uint16 ConversionCount;

Uint16 input1[256];

Uint16 input2[256];

Uint16 Mixing[256];

void main(void)

{

InitSysCtrl();

EALLOW;

SysCtrlRegs.PLLCR.all=0x8;

SysCtrlRegs.HISPCP.all = 0x3;

EDIS;

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

PieVectTable.ADCINT = &adc_isr;

EDIS;

InitAdc();

PieCtrlRegs.PIEIER1.bit.INTx6 = 1;

IER |= M_INT1;

EINT;

ERTM;

LoopCount = 0;

ConversionCount = 0;

AdcRegs.ADCTRL1.bit.SEQ_CASC = 1;

AdcRegs.ADCMAXCONV.all = 0x0001;

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x2;

AdcRegs.ADCTRL2.bit.EVA_SOC_SEQ1 = 1;

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;

EvaRegs.T1CMPR = 0x0380;

EvaRegs.T1PR = 0x07FF;

EvaRegs.GPTCONA.bit.T1TOADC = 1;

EvaRegs.T1CON.all = 0x1042;

for(;;)

{

LoopCount++;

}

}

interrupt void adc_isr(void)

{

input1[ConversionCount] = AdcRegs.ADCRESULT0 >>4;

input2[ConversionCount] = AdcRegs.ADCRESULT1 >>4;

Mixing[ConversionCount] = input1[ConversionCount] + input2[ConversionCount];

if(ConversionCount == 256)

{

ConversionCount = 0;//加软件断点

}

else ConversionCount++;

AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1;

AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

return;

}

四、实验说明:

1、本实验是用DSP自带的ADC转换器采集信号源的信号。并将采集到的信号储存到指定的内存区域。由于ADC是单极性的,所以从信号源过来的双极性信号经过偏置电路转换成单极性信号然后由ADC采样。

2、实验中相关语句说明:

/*************************头文件*********************************/

#include "DSP281x_Device.h" // DSP281x Headerfile Include File

#include "DSP281x_Examples.h" // DSP281x Examples Include File

// Prototype statements for functions found within this file.

interrupt void adc_isr(void);

采用中断方式来处理AD转换,也就是在AD转换完后可以产生中断,然后由DSP处理。

// Global variables used in this example:

Uint16 LoopCount;

Uint16 ConversionCount; AD转换的次数

Uint16 input1[256];

Uint16 input2[256];

Uint16 Mixing[256];

void main(void)

{

InitSysCtrl();

EALLOW;

SysCtrlRegs.PLLCR.all=0x8;

SysCtrlRegs.HISPCP.all = 0x3; // HSPCLK = SYSCLKOUT/6

EDIS;

DINT;

初始化外设中断控制器

InitPieCtrl();

禁止中断,同时清中断标记和中断允许。

IER = 0x0000;

IFR = 0x0000;

初始化外设中断控制器向量表。

InitPieVectTable();

将中断服务程序地址填入中断向量表。

EALLOW; // This is needed to write to EALLOW protected register

PieVectTable.ADCINT = &adc_isr;

EDIS; // This is needed to disable write to EALLOW protected registers

初始化ADC,该程序在后面有详细介绍。

InitAdc(); // For this example, init the ADC

以下程序开AD转换中断。

PieCtrlRegs.PIEIER1.bit.INTx6 = 1;

IER |= M_INT1; // Enable CPU Interrupt 1

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

LoopCount = 0;

ConversionCount = 0;

设置AD转换参数:

AdcRegs.ADCTRL1.bit.SEQ_CASC = 1; 16通道采样模式,排序器1,2进行级联

AdcRegs.ADCMAXCONV.all = 0x0001; // SEQ1中有两个通道采样

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // ADCINA0 在SEQ1中第一个采样

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x2; // ADCINA2 在SEQ1中第二个采样

AdcRegs.ADCTRL2.bit.EVA_SOC_SEQ1 = 1; // 启动SEQ1采样

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1; // 允许SEQ1采样中断

参见资料Spru060d,

以下设置定时器1的比较寄存器的值

EvaRegs.T1CMPR = 0x0380; // Setup T1 compare value

设置周期寄存器的值

EvaRegs.T1PR = 0x07FF; // Setup period register

将定时器1用于AD转换的定时

EvaRegs.GPTCONA.bit.T1TOADC = 1; // Enable EVASOC in EVA

允许定时器1进入比较模式。

EvaRegs.T1CON.all = 0x1042; // Enable timer 1 compare (upcount mode)

等待AD转换时间。

for(;;)

{

LoopCount++;

}

}

AD转换 中断服务程序

interrupt void adc_isr(void)

{

将采集来的值进行保存

input1[ConversionCount] = AdcRegs.ADCRESULT0 >>4;

input2[ConversionCount] = AdcRegs.ADCRESULT1 >>4;

Mixing[ConversionCount] = input1[ConversionCount] + input2[ConversionCount];

if(ConversionCount == 256)

{最多采集256个数。

ConversionCount = 0;//加软件断点

}

else ConversionCount++;

// Reinitialize for next ADC sequence

以下使SEQ1可以重新进行中断,和采样。

AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1; // Reset SEQ1

AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1; // Clear INT SEQ1 bit

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; // Acknowledge interrupt to PIE

return;

}

在文件dsp281x_Adc.c中定义

void InitAdc(void)

{

内部参考基准上电

AdcRegs.ADCTRL3.bit.ADCBGRFDN = 0x3; // Power up bandgap/reference circuitry

模拟电路上电。

AdcRegs.ADCTRL3.bit.ADCPWDN = 1; // Power up rest of ADC

// DELAY_US(ADC_usDELAY2); // Delay after powering up ADC

}

五、实验数据

六、心得体会:

通过这些实验的设计与操作,我们深深体会到DSP的理论知识与实践相结合的重要性。在老师的指导下,我们完成了DSP的所有实验,并学会了CCS 3.1版软件,DSP仿真器,E300实验箱,2812CPU板等的基本操作,掌握了外部断的处理方法、数据存储实验、CUP定时器中断方式控制程序流程A/D转换模块的使用、拨码开关、了解DSP开发系统的组成和结构、掌握F2812的CPU定时器的控制方法,同时非常感谢老师和同学们的帮助。

1、实验指导书中已给出一部分内容的完整代码,需要自己思考改动的地方不多,因此实验难度不大。

2、硬件是基础,做实验时要首先检查硬件设备是否可用,保证后续实验的可检测性。特别是要确定程序能输入到实验箱中。

3、、在实验中应不要带电接线、插拔芯片;插拔接线时轻微转动,便于插拔。 4、在实验中更加熟练地使用示波器等设备进行观察、测量。

第二篇:DSP课程设计 完成

DSP原理及应用

课程设计

题 目: FIR滤波器设计

学 院: 信息工程学院

专业班级: 信息0802班

姓 名: 焦全军

学 号: 2008001222

一、设计题目:有限脉冲响应FIR滤波器的设计

二、设计目的:

1、 掌握数字滤波器的设计过程;

2、 了解FIR的原理和特性;

3、 熟悉设计FIR数字滤波器的原理和方法;

4、 学习FI R滤波器的DSP实现原理;

5、 学习使用CCS的波形观察窗口观察输入/输出信号波形和频谱变化情况。

三、设计原理:

滤波器就是在时间域或频域内,对已知激励产生规定响应的网络,使其能够从信号中提取有用的信号,抑制并衰减不需要的信号,滤波器的设计实质上就是对提出的要求给出相应的性能指标,再通过计算,使物理可实现的实际滤波器响应特性逼近给出的频率响应特性。

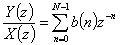

FIR数字滤波器是一种非递归系统,其传递函数为:

=

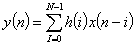

=

由此可得到系统的差分方程为:

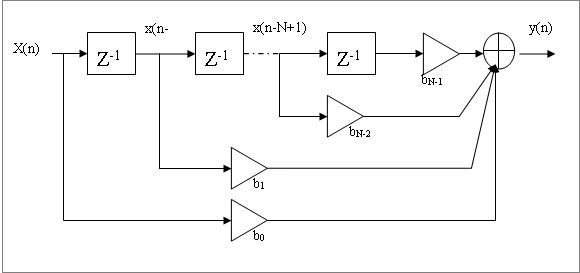

则,FIR滤波器的结构如下图:

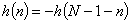

其冲激响应 是有限长序列,它 滤波器系数向量

是有限长序列,它 滤波器系数向量 ,N 为FIR滤波器的阶数。

,N 为FIR滤波器的阶数。

在数字信号处理应用中往往需要设计线性相位的滤波器,FIR滤波器在保证幅度特性满足技术要求的同时,很容易做到严格的线性相位特性为了使滤波器满足线性相位条件,要求其单位脉冲响应 为实序列,且满足偶对称或奇对称条件,即

为实序列,且满足偶对称或奇对称条件,即 或

或 .这样,当N为偶数时,偶对称线性相位FIR滤波器的差分方程表达为

.这样,当N为偶数时,偶对称线性相位FIR滤波器的差分方程表达为

由上可见,FIR滤波器不断地对输入样本 延时后,再做乘法累加运算,将滤波器结果

延时后,再做乘法累加运算,将滤波器结果 输出。因此,FIR实际上是一种乘法累加运算。而对于线性相位FIR滤波器系数的对称特性,可以采用结构精简的FIR结构将乘法器数目减少一半。

输出。因此,FIR实际上是一种乘法累加运算。而对于线性相位FIR滤波器系数的对称特性,可以采用结构精简的FIR结构将乘法器数目减少一半。

应用MATLAB设计FIR滤波器的主要任务就是根据给定的性能指标设计一个 ,使其逼近这一指标,进而计算并确定滤波器的系数

,使其逼近这一指标,进而计算并确定滤波器的系数 ,再将所设计滤波器的幅频响应、相频响应曲线作为输出,与设计要求进行比较,对设计的滤波器进行优化,设计完成之后将得到的FIR滤波器的单位冲激响应序列

,再将所设计滤波器的幅频响应、相频响应曲线作为输出,与设计要求进行比较,对设计的滤波器进行优化,设计完成之后将得到的FIR滤波器的单位冲激响应序列 的各个参数值。

的各个参数值。

四、总体设计方案:

1、 利用MATLAB来确定FIR滤波器的参数;

2、 启动CCS,在CCS中建立一个C源文件和一个命令文件,并将这两个文件添加到工程再编译并装载程序;

3、设置波形时域观察窗口,得到滤波前后的波形变化图;

4、设置频域观察窗口,得到滤波前后的频谱变化图。

五、 CCS开发环境

CCS是一种针对TMS320系列DSP的集成开发环境,在windows操作系统下,采用图形接口界面,提供环境配置、源文件编辑、程序调试、跟踪和分析等工具,提供了配置、建立、调试、跟踪和分析程序的工具,从而完成编辑、编译、链接、调试和数据分析等工作。

利用ccs集成开发软件,用户可以在一个开发环境下完成工程项目创建、程序编辑、编译、链接、调试和数据分析等工作环节。使用ccs开发应用程序的一般步骤为:

1.打开或创建一个工程项目文件,包括源程序、目标文件、库文件、链接命令文件和包含文件。

2.编辑各类文件。可以使用ccs提供的集成编辑环境,对头文件、链接命令文件和源程序进行编辑。

对工程项目进行编译。如出现语法错误,将在构建窗口中显示错误信息。用户可以根据显示信息定位错误信息,更改错误。

4.对结果和数据进行分析和算法评估。用户可以利用ccs提供的探测点、图形显示、性能评价等工具,对运行结果、输出数据进行分析,评估算法性能。

六、参数及其设计步骤:

1、滤波器的参数n=40,wp=0.3π,ws=0.35π

2、matlab系数产生:由f=[0 0.3 0.35 1];

m=[1 1 0 0];

b=fir2(39,f,m)

得到matlab的系数为:

b =

Columns 1 through 11

0.0007 -0.0001 -0.0012 -0.0017 -0.0001 0.0033 0.0050 0.0009 -0.0077 -0.0124 -0.0038

Columns 12 through 22

0.0157 0.0274 0.0113 -0.0300 -0.0607 -0.0335 0.0691 0.2087 0.3090 0.3090 0.2087

Columns 23 through 33

0.0691 -0.0335 -0.0607 -0.0300 0.0113 0.0274 0.0157 -0.0038 -0.0124 -0.0077 0.0009

Columns 34 through 40

0.0050 0.0033 -0.0001 -0.0017 -0.0012 -0.0001 0.0007

(2)汇编源程序:

.title "FIR.ASM"

.mmregs

.bss y,1

K_FIR_BFFR .set 40

PA0 .set 0

PA1 .set 1

FIR_COFF_TABLE .usect "FIR_COFF", 40

D_DATA_BUFFER .usect "FIR_BFR" , 40

.data

COFF_FIR_START .word 7*32768/10000, -1*32768/10000 ;b0,b1

.word -12*32768/10000, -17*32768/10000 ;b2,b3

.word -1*32768/10000, 33*32768/10000 ;b4,b5

.word 50*32768/10000, 9*32768/10000 ;b6,b7

.word -77*32768/10000, -124*32768/10000 ;b8,b9

.word -38*32768/10000, 157*32768/10000 ;b10,b11

.word 274*32768/10000, 113*32768/10000 ;b12,b13

.word -300*32768/10000, -607*32768/10000 ;b14,b15

.word -335*32768/10000, 691*32768/10000 ;b16,b17

.word 2087*32768/10000, 3090*32768/10000 ;b18,b19

.word 3090*32768/10000, 2087*32768/10000 ;b20,b21

.word 691*32768/10000, -335*32768/10000 ;b22,b23

.word -607*32768/10000, -300*32768/10000 ;b24,b25

.word 113*32768/10000, 274*32768/10000 ;b26,b27

.word 157*32768/10000, -38*32768/10000 ;b28,b29

.word -124*32768/10000, -77*32768/10000 ;b30,b31

.word 9*32768/10000, 50*32768/10000 ;b32,b33

.word 33*32768/10000, -1*32768/10000 ;b34,b35

.word -17*32768/10000, -12*32768/10000 ;b36,b37

.word -1*32768/10000, 7*32768/10000 ;b38,b39

.text

.def FIR_INIT

.def FIR_TASK

FIR_INIT: SSBX FRCT

STM #FIR_COFF_TABLE,AR5

RPT #K_FIR_BFFR-1

MVPD #COFF_FIR_START,*AR5+

STM #D_DATA_BUFFER,AR4

RPTZ A,#K_FIR_BFFR-1

STL A,*AR4+

STM #(D_DATA_BUFFER+K_FIR_BFFR-1),AR4

STM #(FIR_COFF_TABLE+K_FIR_BFFR-1),AR5

STM #-1,AR0

LD D_DATA_BUFFER,DP

PORTR PA1,@D_DATA_BUFFER

FIR_TASK: STM #K_FIR_BFFR,BK

RPTZ A,#K_FIR_BFFR-1

MAC *AR4+0%,*AR5+0%,A

STH A,@y

PORTW @y,PA0

BD FIR_TASK

PORTR PA1,*AR4+0%

.end

3、汇编源程序的链接命令文件:

MEMORY

{

PAGE 0: EPROM: org=0E000H len=1000H

VECS: org=0FF80H len=0080H

PAGE 1: SPRAM: org=0060H len=0020H

DARAM: org=0080H len=1380H

}

SECTIONS

{

.text : > EPROM PAGE 0

.text : > VECS PAGE 0

.data : > EPROM PAGE 0

.bss : > SPRAM PAGE 1

FIR_BFR : align(128){}> DARAM PAGE 1

FIR_COFF : align(128){}> DARAM PAGE 1

}

七、实验结果及分析

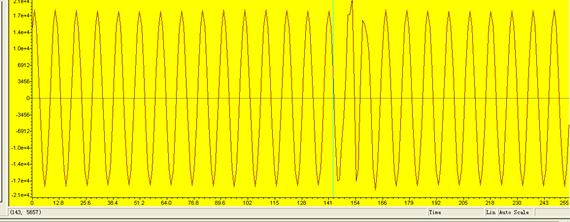

时域波形:

滤波前的时域波形

滤波后的时域波形

由时域图可得:滤波前的时域图是带很多毛刺不规则的正弦波,而滤波后的波形是平滑的等幅正弦波且波形振幅相对滤波前的最大振幅有所减小。

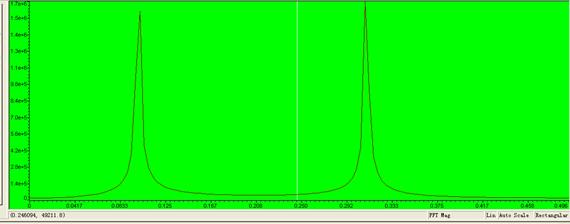

频域波形:

滤波前的频域波形

滤波后的频域波形

由频域图可得:滤波前的频域图会出现两个带尖峰的图像,而滤波后的波形只会出现一个带尖峰图像,而且是出现在低频部分,说明信号经过滤波器后,将信号中的高频成分滤除掉了。

九、设计的收获及体会

通过这次课程设计实现了FIR滤波器的设计并学会了CCS软件的应用,使我对DSP芯片有了更深一步的了解,巩固了以前在《数字信号处理》中学的滤波器设计的理论知识使我们建立了滤波器设计的整体概念,通过仿真使得学的一些抽象的理论形象化,强化了自己的基础知识。

在用CCS软件仿真作图的过程中,由于程序文件在书写过程中出现格的错误,导致在仿真中出现错误,影响仿真的效率,在同学和老师的帮助下我更正了错误问题,最终得到正确的仿真波形图,这使我意识到在进行实验的过程中哪怕一个细节的错误也会导致实验的失败,也警示我在以后的学习生活中要养成细心的习惯。

在这次的课程设计中学会了如何和老师、同学一起交流、探讨问题,在学习的过程中同时培养了和同学之间的合作能力,增进了彼此之间的友谊,感谢在这次设计中给予我帮助的老师还有各位同学。