华东交通大学理工学院课程设计报告

华东交通大学理工学院

课 程 设 计 报 告 书

所属课程名称 实用EDA技术与VHDL教程

题 目 8位16进制频率计设计 分 院

专业班级

学 号 学生姓名 指导教师 谭尾琴

20xx年6月24日

2

1 华东交通大学理工学院课程设计报告

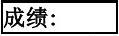

课程设计(论文)评阅意见

评阅人 谭尾琴 20xx年 月 日

第 1 页

2 华东交通大学理工学院课程设计报告

目 录

一、任务设计与要求 ··················· 3

二、设计方案介绍 ···················· 4

三、 VHDL设计部分 ··················· 5

3.1 测频控制电路FTCTRL ···············

3.2锁存器REG32B ···················

3.3计数器COUNTER32B ·················

3.4顶层文件 ·····················

四、 模拟调试部分 ···················

五、 设计仿真运行过程中遇到的问题及解决措施 ······

六、设计心得 ·····················

七、参考文献 ·····················

第 2 页 5 7 8 9 11 14 15 16

3 华东交通大学理工学院课程设计报告

一、任务设计与要求

1、用EDA技术设计并实现8位十六进制频率计,及设计一个基于VHDL的八位十六进制频率计,学习较复杂的数字系统设计方法。书面报告包括工作原理,工作模块图,仿真波形图和问题分析。

2、分别仿真测试模块1,、2和3,在结合模块4完成频率计的完整设计和硬件实现,并给出其测频时序波形及其分析。

3、将频率计改为8位10进制频率计,注意此设计电路的计数器必须是8个4位的10进制计数器。此外注意在测频速度上给予优化。

第 3 页

4 华东交通大学理工学院课程设计报告

二、设计方案介绍

用VHDL语言,完成8位16进制频率计的设计。

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的输入信号脉冲计数允许的信号;1秒计数结束后,计数值被锁入锁存器,计数器清0,为下一测频计数周期作好准备。测频控制信号可以由一个独立的发生器来产生。

数字频率计的关键组成部分包括一个测频控制信号发生器FTCTRL、计数器COUNTER32B和一个锁存器REG32B,另外包含外电路的信号整形电路、脉冲发生器、译码驱动电路和显示电路。其工作原理如下:FTCTRL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计中的32位二进制计数器COUNTER32B的ENABL使能端进行同步控制。当CNT_EN高电平时允许计数;低电平时停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进锁存器REG32B中,并由外部的16进制7段译码器译出,显示计数值。设置锁存器的好处是数据显示稳定,不会由于周期性的清0信号而不断闪烁。锁存信号后,必须有一清0信号RST_CNT对计数器进行清零,为下1秒的计数操作作准备。

该实验组要有四个模块组成:测频信号发生器、32位锁存器 、32位计数器以及顶层文件。

第 4 页

5 华东交通大学理工学院课程设计报告

三、 VHDL设计部分

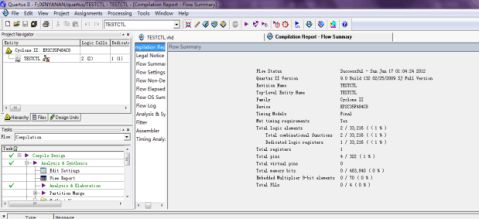

3.1 测频控制电路FTCTRL

设计频率计的关键是设计一个测频率控制信号发生器,产生测量频率的控制时序。控制时钟信号clk取为1Hz,2分频后即可产生一个脉冲宽为1秒的时钟cnt-en,以此作为计数闸门信号。当cnt-en为高电平时,允许计数;当cnt-en由高电平变为低电平(下降沿到来)时,应产生一个锁存信号,将计数值保存起来;锁存数据后,还要在下次cnt-en上升沿到来之前产生零信号ret-en,将计数器清零,为下次计数做准备。

程序代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TESTCTL IS

PORT (CLK : IN STD_LOGIC; TSTEN : OUT STD_LOGIC; CLR_CNT : OUT STD_LOGIC; Load : OUT STD_LOGIC ); END TESTCTL;

ARCHITECTURE behav OF TESTCTL IS

SIGNAL Div2CLK : STD_LOGIC;

BEGIN

PROCESS( CLK )

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

Div2CLK <= NOT Div2CLK;END IF;

END PROCESS;

PROCESS (CLK, Div2CLK)

BEGIN

IF CLK = '0' AND Div2CLK = '0' THEN

CLR_CNT <= '1';

ELSE

CLR_CNT <= '0';

END IF;

END PROCESS;

Load <= NOT Div2CLK; TSTEN <= Div2CLK;

END behav;

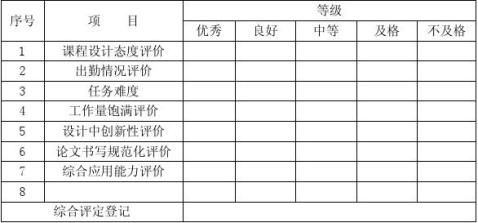

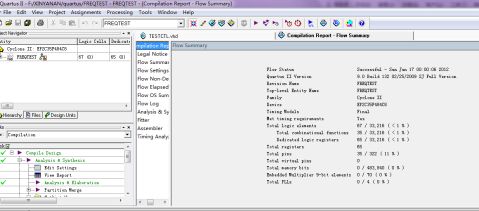

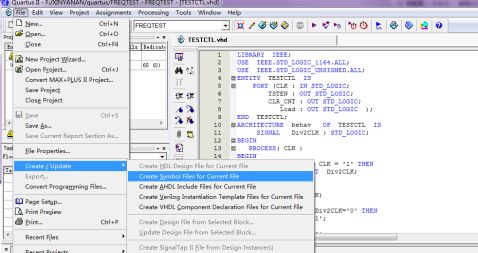

生成LPM模块的流程:选择File→Creat/_Update→Creat symbol files for current file,再选择Tools→Netlist viewers→RET viewer则可以看到生成的元件模块图。

第 5 页

6 华东交通大学理工学院课程设计报告

第 6 页

7 华东交通大学理工学院课程设计报告

3.2锁存器REG32B

当cnt-en下降沿到来时,将计数器的计数值锁存,这样可由外部的

七段译码器译码并在数码管显示。设置锁存器的好处是显示的数据稳定,不会由于周期性的清零信号而不断闪烁。锁存器的位数应跟计数器完全一样。 程序代码如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY REG IS

PORT

(

clock : IN STD_LOGIC ;

data : IN STD_LOGIC_VECTOR (31 DOWNTO 0); q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0)

);

END REG;

ARCHITECTURE SYN OF REG IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (31 DOWNTO 0); COMPONENT lpm_ff GENERIC (

lpm_width : NATURAL;

lpm_fftype : STRING );

PORT (

clock : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0); data : IN STD_LOGIC_VECTOR (31 DOWNTO 0) ); END COMPONENT;

BEGIN

q <= sub_wire0(31 DOWNTO 0);

lpm_ff_component : lpm_ff

GENERIC MAP (

LPM_WIDTH => 32,

LPM_FFTYPE => "DFF" )

PORT MAP (

clock => clock,

data => data,

第 7 页

8 华东交通大学理工学院课程设计报告

q => sub_wire0 );

END SYN;

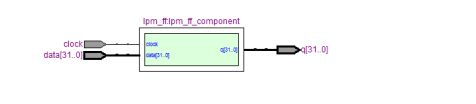

生成LPM模块的流程同上,这里不再赘述。观察到的元件模块图如下

3.3计数器COUNTER32B

计数器以待测信号作为时钟,清零信号rst到来时,异步清零;cnt-en为高电平时开始计数。计数是以十进制数显示,本文设计了一个简单的频率计,如果要测比较高的频率信号,则将cout的输出位数增加,当然锁存器的位数也要增加。 程序代码如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY CNT IS

PORT

(

clock : IN STD_LOGIC ;

clk_en : IN STD_LOGIC ;

aclr : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0); cout : OUT STD_LOGIC

);

END CNT;

ARCHITECTURE SYN OF CNT IS

SIGNAL sub_wire0 : STD_LOGIC ;

SIGNAL sub_wire1 : STD_LOGIC_VECTOR (31 DOWNTO 0);

COMPONENT lpm_counter

GENERIC (

lpm_width : NATURAL;

lpm_direction : STRING );

PORT (

clk_en : IN STD_LOGIC ;

aclr : IN STD_LOGIC ;

clock : IN STD_LOGIC ;

cout : OUT STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0) ); END COMPONENT;

BEGIN

cout <= sub_wire0;

q <= sub_wire1(31 DOWNTO 0);

lpm_counter_component : lpm_counter

GENERIC MAP (

第 8 页

9 华东交通大学理工学院课程设计报告

LPM_WIDTH => 32,

LPM_DIRECTION => "UP" )

PORT MAP (

clk_en => clk_en,

aclr => aclr,

clock => clock,

cout => sub_wire0,

q => sub_wire1);

END SYN;

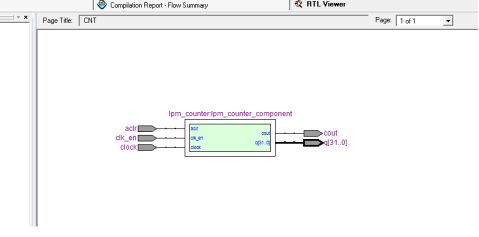

同样在这里不再赘述模块生成流程,最后观察到的元件模块图如下:

3.4顶层文件

程序代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FREQTEST IS

PORT ( CLK : IN STD_LOGIC;

FSIN : IN STD_LOGIC;

CCOUT: OUT STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END FREQTEST;

ARCHITECTURE struc OF FREQTEST IS

COMPONENT TESTCTL

PORT ( CLK : IN STD_LOGIC; TSTEN : OUT STD_LOGIC; CLR_CNT : OUT STD_LOGIC; Load : OUTSTD_LOGIC );

END COMPONENT;

COMPONENT CNT

PORT ( CLOCK : IN STD_LOGIC;

ACLR : IN STD_LOGIC;

CLK_EN : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(31 DOWNTO 0); COUT : OUT STD_LOGIC ); END COMPONENT;

COMPONENT REG

PORT ( CLOCK : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(31 DOWNTO 0); Q : OUT STD_LOGIC_VECTOR(31

第 9 页

10 华东交通大学理工学院课程设计报告

DOWNTO 0) ); END COMPONENT;

SIGNAL TSTEN1 : STD_LOGIC;

SIGNAL CLR_CNT1 : STD_LOGIC;

SIGNAL Load1 : STD_LOGIC;

SIGNAL DTO1 : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL CARRY_OUT1 : STD_LOGIC_VECTOR(6 DOWNTO 0); BEGIN

U1 : TESTCTL PORT MAP( CLK =>CLK, TSTEN => TSTEN1, CLR_CNT => CLR_CNT1, Load => Load1 );

U2 : REG PORT MAP( CLOCK => Load1, DATA => DTO1,Q => DOUT);

U3 : CNT PORT MAP(CLOCK => FSIN,ACLR =>

CLR_CNT1,CLK_EN => TSTEN1, Q => DTO1,COUT => CCOUT );

END struc;

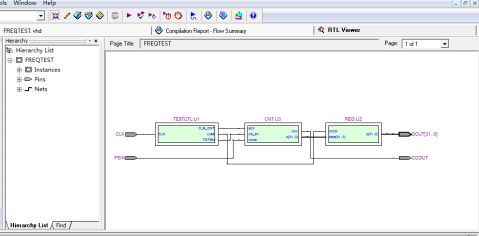

将上述3个程序的.vhd文件和生成的.bsf文件复制到顶层文件工程所在的文件夹,再通过上述同样的流程生成元件模块图,如下:

第 10

11 华东交通大学理工学院课程设计报告

四、 模拟调试部分

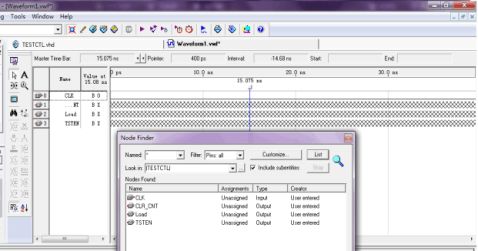

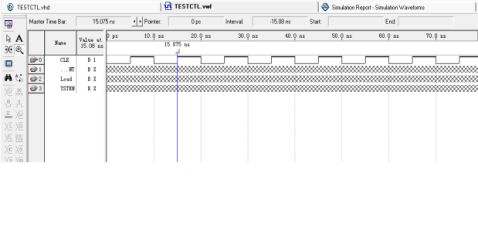

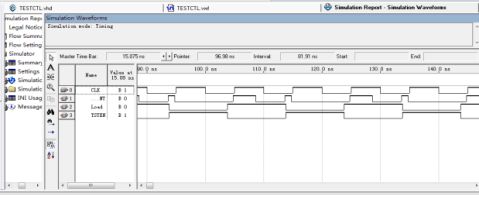

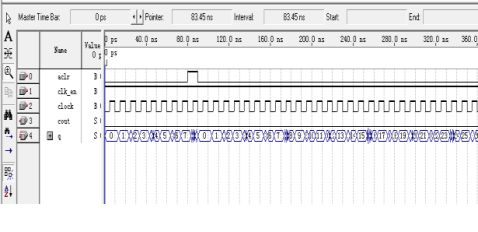

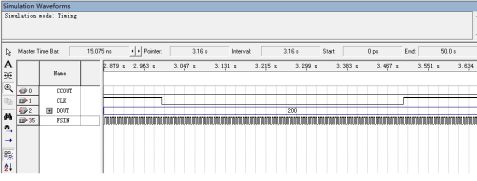

对测频信号发生器文件进行仿真

选择File→new→Vector Wavefor→file→OK;再选择Edit→End Time,设定仿真域的时间为50μs;然后选择View→Utility Window→Node Finder,在Filter框中选中Pins:all,单击list,将出现的所有端口引脚名拉入到波形编辑器的左栏,保存,选择Processing下的Start Simulation,即可得到仿真波形图。

对锁存器文件仿真步骤同上述一样,得到仿真波形图如下:

第 11

12 华东交通大学理工学院课程设计报告

对计数器文件仿真,得到如下波形:

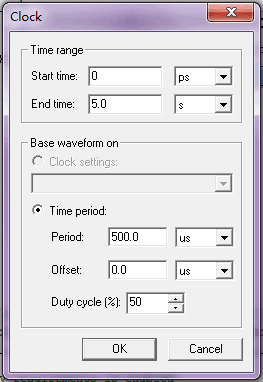

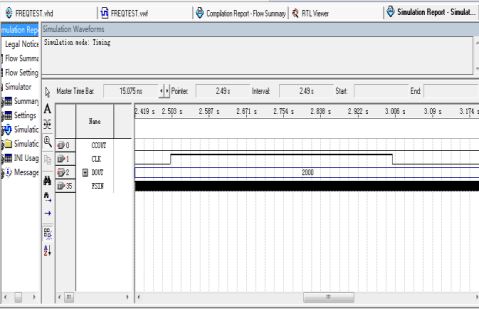

对顶层文件进行仿真,得到波形如下: a 待测信号频率为2kHz 由:T=1/f,所以T=1/2000=0.0005s=500μs

所设置待测信号周期为500μs,如图:

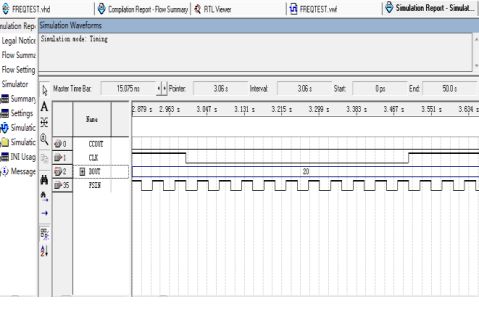

b 待测信号频率为500ms200Hz,待测信号周期为

第 12

13 华东交通大学理工学院课程设计报告

c待测信号频率为20Hz,待测信号周期为

第 13

14 华东交通大学理工学院课程设计报告

五、 设计仿真运行过程中遇到的问题及解决措施

在对顶层文件进行元件模块生成时,没有出现模块图。

解决方案:将以上3个程序的.vhd文件和生成的.bsf文件复制到顶层文件工程所在的文件夹,然后再进行模块生成操作,就能顺利进行。 在对顶层文件进行仿真时,在设置FSIN的信号周期为500ms时,无法进行设定?

解决方案:需要将本模块Edit菜单中的End Time时间改为5s。

提高部分如果被测频率降低,则可以通过采用周期测频法,即在待测信号的一个周期内,记录标准频率信号变化的次数,即上升沿的次数N。只需要修改顶层文件程序当中的例化即可

第 14

15 华东交通大学理工学院课程设计报告

六、设计心得

本次课程设计主要用到了多种芯片,程序也比较长比较麻烦,同时也遇到了不少困难,尤其是关于校时模块的设计实现。

通过本次设计,我系统的了解了实时时钟的设计流程,尤其是硬、软件的设计方法,掌握了键盘显示电路的基本功能及编程方法,掌握了键盘电路和显示电路的一般原理,也进一步掌握了32位锁存器的使用和中断处理器程序的编程方法。开拓了思路,锻炼了实践动手能力,提高了分工协作能力和分析问题,解决问题的能力,达到了本次课程设计的目的。

第 15

16 华东交通大学理工学院课程设计报告

七、参考文献

[1] 巴里.威尔金森 编著, 《数字设计基础》(双语教学版)

[2] 潘松 编著,《EDA技术实用教程》 科学出版设

[3] 徐雯娟 编著 《基于VHDL语音的数字电路设计实验指导》

[4] 高振斌等

编著 《EDA实用技术及应用》

第 16

17 华东交通大学理工学院课程设计报告

第 17