数字电路与逻辑设计综合课题实验报告

北京邮电大学信息与通信工程学院

一、 设计课题的任务要求

题目三 掷骰子游戏的电路的设计与实现

基本要求

1、电路可供甲乙二人游戏,游戏者甲使用的按键为BTN0,游戏者乙使用的按键为

BTN1。

2、每按一次按键,代表掷一次骰子,可随机得到 1~6 范围内的两个数字。

3、甲乙按键产生的随机数字分别用数码管DISP0-DISP1、DISP2-DISP3 显示,并用

DISP7 显示比赛局数,比赛结束用8×8 点阵显示获胜方,并伴有声音效果。

4、具体游戏规则如下:

(1) 第一局比赛,甲乙依次各按一次按键,按键所得两数之和为7 或11 者胜;若无

人取胜,则进行第二局比赛;

(2) 第二局比赛,甲乙每人各按一次按键,按键所得二数之和与第一局比赛相同者获

胜,若无人获胜,则进行第三局比赛,重复进行步骤(2),直到出现胜者为止。

(3) 游戏局数最多进行六局。在第六局比赛时,若重复进行步骤(2)仍未出现胜者,

以按键所得两数之和最大者为获胜方。

提高要求

1、增加多人游戏的功能,数码管可分时记录显示每个游戏者的骰子点数。

2、点阵显示增加游戏开机动画、结束动画,并伴有乐曲播放。

3、自拟其它功能。

二、 系统设计

设计思路

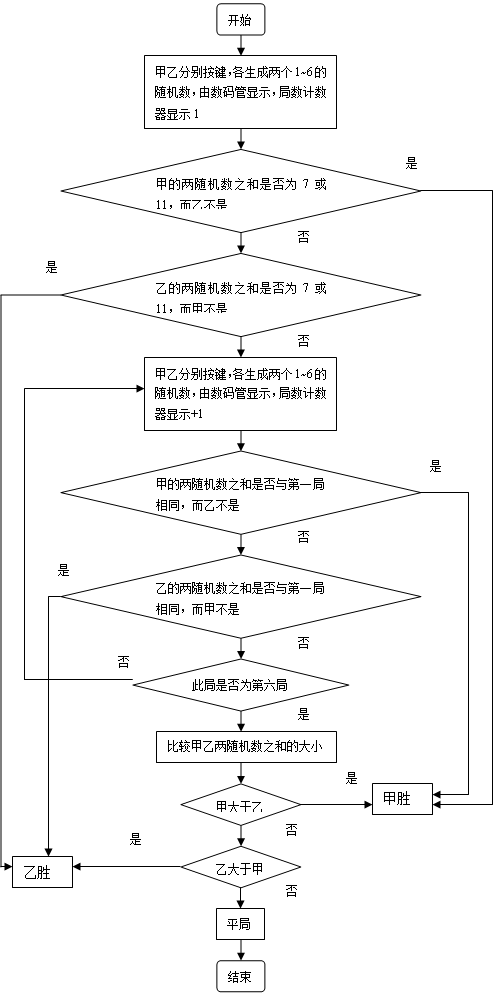

首先根据实验的基本要求,可以知道掷骰子游戏至少有四种状态,分别是游戏状态(S0)、甲胜状态(S1)、乙胜状态(S2)和平局状态(S3),其中游戏状态可能到达其余三种状态中任意一种。若是到达平局状态,就返回游戏状态,游戏继续;而一旦到达甲胜或者乙胜状态,游戏过程结束。

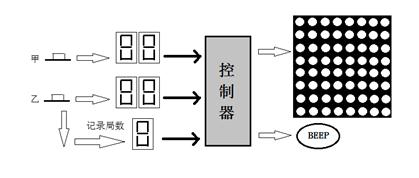

游戏状态中,由两个按键作为输入,每个按键控制两位数码管,共有四位数码管分别显示四个1~6的随机数,还有一位数码管显示当前局数。离开游戏状态后,点阵显示甲胜、乙胜或平局,而且有胜者的状态中,蜂鸣器发声。

掷骰子游戏电路设计的结构图如下:

但我们还要在上述基本思想下注意几个问题:

1. 由于按键输入不稳定,数字变化太快,所以需加入按键防抖模块。

2. 数码管、点阵、蜂鸣器都需要特殊的分频,因此还需要多级的分频器。

3. 局数会影响控制器的逻辑判断,因此在循环判断时,要将第一局,第六局与第二到五局分开考虑。

4. 第一局的甲、乙两随机数之和需要单独记录,好跟后面产生的随机数的和比较。

5. 该实验的一大难点在于随机数的产生,随机数发生器需要单独拿出来研究

因此,该实验程序大致分为:随机数发生器、多级分频器、存储器、数码管显示译码、点阵显示、蜂鸣器控制、控制器和防抖模块。

分块设计

1. 随机数发生器

由于VHDL语言不能直接调用随机数,因此需要通过代码实现伪随机数的生成。查阅资料发现,生成伪随机数的方法一般有两种,一种是应用m序列发生器,将一段既定的人为书写的随机数列顺序输出,还有一种是通过时钟控制顺序计数,应用按键时刻的随机性输出随机数。经各方面比较,我选择了后者。两随机数中,低位的是按照时钟脉冲从一至六顺序输出计数,逢六进一位到高位,而高位的同理,从而使两随机数建立联系,实现一个按键随机按下,同时得出两随机数。由于时钟变化很快,两随机数之间的时间差可忽略不计。

2. 多级分频器

已知时钟的频率是50MHz,而输入到数码管和点阵的频率是1k~5kHz,输入到蜂鸣器的频率则希望控制在100Hz以下。因此需要一个多级分频器,第一级分到100kHz,第二级再分到5kHz给数码管,1kHz给点阵,第三级从1kHz分到2Hz给蜂鸣器。

3. 存储器

由于后几局的两个甲乙各自随机数之和要跟第一局的作比较,所以需要存储器来记录第一局产生的四个随机数。

4. 数码管显示译码

5. 点阵显示

6. 蜂鸣器控制

7. 控制器

8. 防抖模块

由于防抖模块需要加入到所有按键输入,因此单独拿到主程序外。加入防抖模块后,每次有按键输入,即电平发生改变,都能持续一个时钟脉冲,从而确保每次按键都能被控制器接收。此次实验由按键输入的信号有甲(a),乙(b)和clear。

总体框图

掷骰子游戏电路的逻辑流程图如下:

掷骰子游戏的状态转移图如下:

三、 仿真波形及波形分析

该实验的难点在于甲乙掷骰子时分别产生两个随机数,因此在实验开始之初,就对产生随机数的模块进行仿真。仿真波形见下图:

四、 源程序

总程序

library ieee;

use ieee. std_logic_1164. all;

use ieee. std_logic_unsigned. all;

use ieee. std_logic_arith. all;

entity s2012210709 is

port (

clk: in std_logic;

a_in,b_in, clear_in, switch_open: in std_logic;

led: out std_logic_vector( 6 downto 0);

light: out std_logic_vector( 5 downto 0);

row, colr, colg: out std_logic_vector( 7 downto 0);

beep: out std_logic);

end s2012210709;

architecture youxi of s2012210709 is

signal a, b, clear: std_logic;

signal winner: integer range 0 to 2;

signal tmpal,tmpah,tmpbl,tmpbh: integer range 1 to 6; -- 计数器模值为6

signal jushu: integer range 0 to 6:=0;

signal num0, num1, num2, num3, num5: std_logic_vector( 2 downto 0); -- 取得随机数

signal tmp0, tmp1, tmp2, tmp3: integer range 1 to 6; -- 记录随机数

signal tmpnum0, tmpnum1, tmpnum2, tmpnum3: integer range 1 to 6; -- 记录第一局的随机数

signal dianzhen: integer range 0 to 7;

signal tmpfp: integer range 0 to 249; --/100,000

signal tmpled: integer range 0 to 9; --/5000

signal tmpdianzhen: integer range 0 to 49; --/1000

signal tmpfeng: integer range 0 to 249; --/2

signal clkfp, clkled, clkdianzhen, clkfeng: std_logic;

component fangdou is --防抖程序(见总程序结束后)

port(

clk_in: in std_logic;

ai, bi, ci: in std_logic;

ao, bo, clearo: out std_logic);

end component;

begin

f0: fangdou port map( clk_in=>clk, ai=>a_in, bi=>b_in, ci=>clear_in, ao=>a, bo=>b, clearo=>clear);

p1: process( clk) -- 输出两个1~6的随机数

begin

if clk'event and clk='1' then

if clear='1' then

tmpal<=1; tmpah<=1;

elsif tmpal=6 then

tmpal<=1; tmpah<=tmpah+1;

elsif tmpah=6 then

tmpah<=1;

elsif tmpbl=6 then

tmpbl<=1; tmpbh<=tmpbh+1;

elsif tmpbh=6 then

tmpbh<=6;

else tmpal<=tmpal+1; tmpbl<=tmpbl+1;

end if;

end if;

end process p1;

p2: process( clear, clk)

begin

if clear='1' then

tmpfp<=0;

elsif clk'event and clk='1' then

if tmpfp=249 then

tmpfp<=0; clkfp<= not clkfp;

else tmpfp<=tmpfp+1;

end if;

end if;

end process p2;

p3: process( clear, clkfp)

begin

if clear='1' then

tmpdianzhen<=0;

elsif clkfp'event and clkfp='1' then

if tmpdianzhen=49 then

tmpdianzhen<=0; clkdianzhen<= not clkdianzhen;

else tmpdianzhen<=tmpdianzhen+1;

end if;

end if;

end process p3;

p4: process( clkdianzhen)

begin

if clkdianzhen'event and clkdianzhen='1' then

if dianzhen=7 then

dianzhen<=0;

else

dianzhen<=dianzhen+1;

end if;

end if;

end process p4;

p9: process( a, b)

begin

num5<=conv_std_logic_vector( jushu, 3); -- num5记录 数

if a'event and a='1' then -- num0,num1,num2,num3 分别记录4个随机数

tmp0<= tmpal; tmp1<= tmpah;

num0<=conv_std_logic_vector( tmpal, 3);

num1<=conv_std_logic_vector( tmpah, 3);

end if;

if b'event and b='1' then

tmp2<= tmpbl; tmp3<= tmpbh;

num2<=conv_std_logic_vector( tmpbl, 3);

num3<=conv_std_logic_vector( tmpbh, 3);

jushu<=jushu+1;

if jushu=1 then

tmpnum0<=tmp0; tmpnum1<=tmp1; tmpnum2<=tmp2; tmpnum3<=tmp3;

if (tmp0+tmp1=7 or tmp0+tmp1=11) and (tmp2+tmp3/=7 or tmp2+tmp3/=11) then

winner<=0;

elsif (tmp2+tmp3=7 or tmp2+tmp3=11) and (tmp0+tmp1/=7 or tmp0+tmp1/=11) then

winner<=1;

else jushu<=jushu+1;

end if;

elsif jushu=6 then

if (tmp0+tmp1)>(tmp2+tmp3) then

winner<=0;

elsif (tmp0+tmp1)<(tmp2+tmp3) then

winner<=1;

else winner<=2;

end if;

else

if (tmp0+tmp1)=(tmpnum0+tmpnum1) and (tmp2+tmp3)/=(tmpnum2+tmpnum3) then

winner<=0;

elsif (tmp2+tmp3)=(tmpnum2+tmpnum3) and (tmp0+tmp1)/=(tmpnum0+tmpnum1) then

winner<=1;

else jushu<=jushu+1;

end if;

end if;

end if;

end process p9;

p10: process( clear, clk) --数码管显示

begin

if clear='1' then

tmpled<=0;

elsif clkfp'event and clkfp='1' then

if tmpled=9 then

tmpled<=0; clkled<= not clkled;

else tmpled<=tmpled+1;

end if;

end if;

end process p10;

p11: process( num0, num1, num2, num3, num5)

begin

light<="111110";

case num0 is

when"001"=> led<="0110000";

when"010"=> led<="1101101";

when"011"=> led<="1111001";

when"100"=> led<="0110011";

when"101"=> led<="1011011";

when"110"=> led<="1011111";

when others=> led<="0000000";

end case;

light<="111100";

case num1 is

when"001"=> led<="0110000";

when"010"=> led<="1101101";

when"011"=> led<="1111001";

when"100"=> led<="0110011";

when"101"=> led<="1011011";

when"110"=> led<="1011111";

when others=> led<="0000000";

end case;

light<="111000";

case num2 is

when"001"=> led<="0110000";

when"010"=> led<="1101101";

when"011"=> led<="1111001";

when"100"=> led<="0110011";

when"101"=> led<="1011011";

when"110"=> led<="1011111";

when others=> led<="0000000";

end case;

light<="110000";

case num3 is

when"001"=> led<="0110000";

when"010"=> led<="1101101";

when"011"=> led<="1111001";

when"100"=> led<="0110011";

when"101"=> led<="1011011";

when"110"=> led<="1011111";

when others=> led<="0000000";

end case;

light<="010000";

case num5 is

when"001"=> led<="0110000";

when"010"=> led<="1101101";

when"011"=> led<="1111001";

when"100"=> led<="0110011";

when"101"=> led<="1011011";

when"110"=> led<="1011111";

when others=> led<="0000000";

end case;

end process p11;

p12: process( winner)

begin

if winner=0 then

case dianzhen is

when 0=>row<="01111111"; colr<="00111110"; colg<="00000000";

when 1=>row<="10111111"; colr<="00101010"; colg<="00000000";

when 2=>row<="11011111"; colr<="00111110"; colg<="00000000";

when 3=>row<="11101111"; colr<="00101010"; colg<="00000000";

when 4=>row<="11110111"; colr<="00111110"; colg<="00000000";

when 5=>row<="11111011"; colr<="00001000"; colg<="00000000";

when 6=>row<="11111101"; colr<="00001000"; colg<="00000000";

when 7=>row<="01111110"; colr<="00001000"; colg<="00000000";

end case;

elsif winner=1 then

case dianzhen is

when 0=>row<="01111111"; colr<="01111110"; colg<="01111110";

when 1=>row<="10111111"; colr<="01111110"; colg<="01111110";

when 2=>row<="11011111"; colr<="00001100"; colg<="00001100";

when 3=>row<="11101111"; colr<="00011000"; colg<="00011000";

when 4=>row<="11110111"; colr<="00110010"; colg<="00110010";

when 5=>row<="11111011"; colr<="01111110"; colg<="01111110";

when 6=>row<="11111101"; colr<="01111110"; colg<="01111110";

when 7=>row<="11111110"; colr<="00000000"; colg<="00000000";

end case;

else

case dianzhen is

when 0=>row<="01111111"; colr<="00000000"; colg<="01111111";

when 1=>row<="10111111"; colr<="00000000"; colg<="00101010";

when 2=>row<="11011111"; colr<="00000000"; colg<="00101010";

when 3=>row<="11101111"; colr<="00000000"; colg<="00011100";

when 4=>row<="11110111"; colr<="00000000"; colg<="01111111";

when 5=>row<="11111011"; colr<="00000000"; colg<="00001000";

when 6=>row<="11111101"; colr<="00000000"; colg<="00001000";

when 7=>row<="11111110"; colr<="00000000"; colg<="00001000";

end case;

end if;

end process p12;

p13: process( clkdianzhen)

begin

if clear='1' then

tmpfeng<=0;

elsif clkdianzhen'event and clkdianzhen='1' then

if tmpfeng=249 then

tmpfeng<=0; clkfeng<= not clkfeng;

else tmpfeng<=tmpfeng+1;

end if;

end if;

end process p13;

p14: process( winner)

begin

if winner=0 or winner=1 then

beep<='1';

else beep<='0';

end if;

end process p14;

end youxi;

防抖程序模块

library ieee;

use ieee.std_logic_1164.all;

entity fangdou is

port( clk_in: in std_logic;

ai, bi, ci: in std_logic;

ao, bo, clearo: out std_logic);

end fangdou;

architecture a of fangdou is

signal aitmp1, aitmp2: std_logic;

signal bitmp1, bitmp2: std_logic;

signal citmp1, citmp2: std_logic;

begin

process( clk_in)

begin

if clk_in'event and clk_in='0' then

aitmp2<= aitmp1;

aitmp1<= ai;

bitmp2<= bitmp1;

bitmp1<= bi;

citmp2<= citmp1;

citmp1<= ci;

end if;

end process;

ao<=clk_in and aitmp1 and (not aitmp2);

bo<=clk_in and bitmp1 and (not bitmp2);

clearo<=clk_in and citmp1 and (not citmp2);

end a;

五、 功能说明及资源利用情况

功能说明

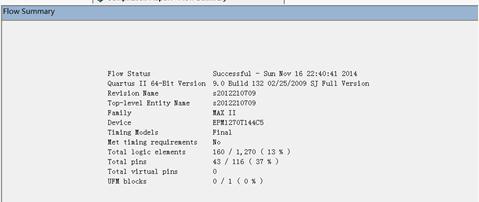

资源利用情况

由编译结果可知,本程序一共使用逻辑单元160个,占用率为13%,使用逻辑管脚43个,占用率为37%。

六、 故障及问题分析

点阵显示

蜂鸣器

七、 总结和结论