课程设计的要求与说明

目的:掌握电子商务网站的系统配置要求和安装、设置方法;

掌握前台页面的布局结构设计及交互性的实现;

掌握后台数据库处理过程及程序设计方法。

开发环境:WinXP+IIS+ASP.NET+Access+IE+网页编辑工具+图像处理工具

总体要求:完成电子商务网站的购物过程

前台实现用户注册、商品浏览/查询、购物车

后台注册用户、商品、订单管理

选题及分组:建议每组2人,鼓励1人一题,题目自定,尽量选用小题目、做到主题明确(如**产品销售网站),请在课程设计周开始前将选题及分组名单报给各班班长,课程设计开始的前二天内各班班长将分组名单用EXCEL电子表格方式报给我(HLX@guet.edu.cn),要有学号、姓名、选题名称。(题目确定后一般不得更改,否则会影响成绩)

结束验收方式:设计周最后两天为验收时间,以组为单位逐个进行验收,同时提交课程设计说明书。

对设计说明书的要求:统一使用A4纸打印,封面格式为

内容包括(但不限于)以下几点:

①概述

②系统分析—可行性、要解决的问题、已有基础、使用的开发工具等

③系统设计—数据库表结构、功能模块划分、前台页面结构等

④具体实现方法与主要技术

⑤测试、使用与评价

⑥简单的使用说明书

成绩评定:前台页面元素、布局结构、导航、色彩搭配与主题相符

后台功能、易操作

自己设计、工作量是考虑的一个主要因素,对页面元素中自己设计部分请留下“证据”。

最终成绩按“五级”计分制给出,2人同组时,成绩会有差别,请实事求是列出各人在设计过程中所承担的任务,否则按排名定成绩。

设计资料及范例:ftp://202.193.72.102/教学区/五系/黄立新/Ec_design

第二篇:桂林电子科技大学系统实验报告

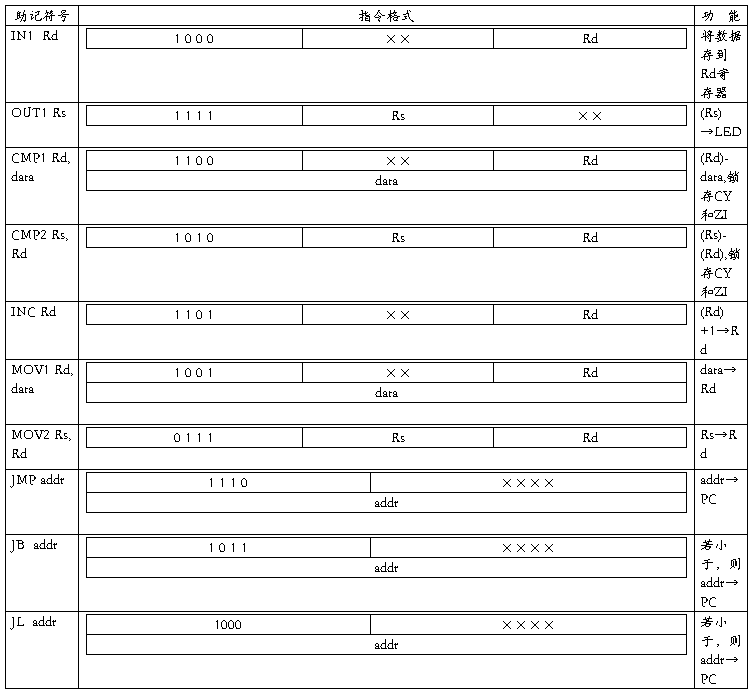

表1 指令格式,符号和功能

7 汇编语言源程序

算法思想为:采用R0寄存器存输入整数的个数,R1存放输入的整数,R2存放最小负数,用下面的程序实现如下上述功能:

MOV1 R0,0 功能:将立即数0→R0(R0用于存放记录输入数的个数)

MOV1 R2,FFH 将立即数FFH→R2(R2用于存放最小的负数)

L1: CMP1 RO,0A 将输入的整数的个数与0A相比较, 锁存SF\FS

JL L2 小于,则转到L2处执行

JMP L4 跳转到L4结束执行

L2: IN1 R1 输入一个整数存放于R1当中

INC R0 将R0中的数加1

CMP2 R1,R2 将输入的数与寄存器里的数相比较,锁存SF\FS

JL L3 小于,则跳转到L3

JMP L1 跳转到L1

L3: MOV2 R1,R2 将寄存器R1的数转移到R2当中

JMP L1 跳转到L1

L4: OUT1 R2 输出最小负数

助记符 地址(十六进制) 机器代码 功能

MOV1 R0,0 00 10010000 0→R0

01 00000000

MOV1 R2,FFH 02 10010010 FFH→R2

03 11111111

L1: CMP1 RO,0A 04 11000000 (R0)-9

05 00001010

JL L2 06 00110000 L2→PC

07 00001010

JMP L4 08 11100000 L4→PC

09 00010100

L2: IN1 R1 0A 00000001 (input)→R1

INC R0 0B 11010000 (R0)+1→R0

CMP2 R1,R2 0C 10100110 (R2)-(R1)

JL L3 0D 10000000 L3→PC

0E 00010001

JMP L1 0F 11100000 L1→PC

10 00000100

L3: MOV2 R1,R2 11 01110110 (R1)→(R2)

JMP L1 12 11100000 L1→PC

13 00000100

L4: OUT1 R2 14 11111000 (R2) →LED

12软件清单(用VHDL描述)

(1) 地址转移逻辑电路(AADR)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADDR IS

PORT(

I7,I6,I5,I4:IN STD_LOGIC;

FZ,FC,FS,T4,P1,P2,P3:IN STD_LOGIC;

SE6,SE5,SE4,SE3,SE2,SE1:OUT STD_LOGIC

);

END ADDR;

ARCHITECTURE A OF ADDR IS

BEGIN

SE6<= NOT( NOT FS AND P3 AND T4);

SE5<=NOT((NOT FC AND FZ )AND P2 AND T4);-- FZ=0,跳转

SE4<=NOT(I7 AND P1 AND T4);

SE3<=NOT(I6 AND P1 AND T4);

SE2<=NOT(I5 AND P1 AND T4);

SE1<=NOT(I4 AND P1 AND T4);

END A;

(2) 算术逻辑运算单元ALU

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ALU IS

PORT(

A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

S1,S0:IN STD_LOGIC;

BCDOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

CY,ZI,SF:OUT STD_LOGIC

);

END ALU;

ARCHITECTURE A OF ALU IS

SIGNAL AA,BB,TEMP:STD_LOGIC_VECTOR(8 DOWNTO 0);

BEGIN

PROCESS(S1,S0)

BEGIN

IF(S1='0' AND S0='0')THEN

AA<='0'&A;

BB<='0'&B;

TEMP<=AA+BB;

BCDOUT<=TEMP(7 DOWNTO 0);

CY<=TEMP(8);

IF(TEMP="100000000" OR TEMP="000000000")THEN

ZI<='1';

ELSE

ZI<='0';

END IF;

ELSIF(S1='0' AND S0='1')THEN

BCDOUT<=A-B;

IF((A(7)='0' AND B(7)='0') OR (A(7)='1' AND B(7)='1'))THEN

IF(A<B)THEN

CY<='1';

ZI<='0';

SF<='1';

ELSIF(A=B)THEN

CY<='0';

ZI<='1';

SF<='0';

ELSE

CY<='0';

ZI<='0';

SF<='0';

END IF;

ELSIF((A(7)='0') AND (B(7)='1'))THEN

CY<='1';

ZI<='0';

SF<='0';

ELSIF((A(7)='1') AND (B(7)='0'))THEN

CY<='0';

ZI<='0';

SF<='1';

END IF;

ELSIF(S1='1' AND S0='0')THEN

AA<='0'&A;

TEMP<=AA+1;

BCDOUT<=TEMP(7 DOWNTO 0);

CY<=TEMP(8);

IF(TEMP="100000000")THEN

ZI<='1';

ELSE

ZI<='0';

END IF;

ELSE

BCDOUT<="00000000";

CY<='0';

ZI<='0';

END IF;

END PROCESS;

END A;

(3)控制存储器(CONTROM)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CONTROM IS

PORT(

ADDR:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

UA:OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

D:OUT STD_LOGIC_VECTOR(19 DOWNTO 0)

);

END CONTROM;

ARCHITECTURE A OF CONTROM IS

SIGNAL DATAOUT:STD_LOGIC_VECTOR(25 DOWNTO 0);

BEGIN

PROCESS(ADDR)

BEGIN

CASE ADDR IS

WHEN"000000"=>DATAOUT<="11100110010011110000000010";

WHEN"000010"=>DATAOUT<="10010110010010110100010000";

WHEN"010101"=>DATAOUT<="10000110010110110000000100";

WHEN"000100"=>DATAOUT<="10000010011011110000000101";

WHEN"000101"=>DATAOUT<="10000110110011111000000000";

WHEN"000110"=>DATAOUT<="10001110010010110000000000";

WHEN"010111"=>DATAOUT<="10001100010011110000000000";

WHEN"010000"=>DATAOUT<="10001110010011010000000000";

WHEN"011001"=>DATAOUT<="11100110010011110000000110";

WHEN"011010"=>DATAOUT<="10000100011011110000010100";

WHEN"001011"=>DATAOUT<="11100110010011110010100000";

WHEN"011100"=>DATAOUT<="11100110010011110000010101";

WHEN"011101"=>DATAOUT<="10000010011011110000010010";

WHEN"011110"=>DATAOUT<="11100110010011110000010011";

WHEN"011111"=>DATAOUT<="10000100010001100000000000";

WHEN"010010"=>DATAOUT<="10001111000011110000000000";

WHEN"010011"=>DATAOUT<="01000110010010110000000000";

WHEN"010100"=>DATAOUT<="10000010010111110000000111";

WHEN"000111"=>DATAOUT<="10000110110011111000000000";

WHEN"100000"=>DATAOUT<="01000110010010110000000000";

WHEN"110000"=>DATAOUT<="10000110010011110000000000";

WHEN"011000"=>DATAOUT<="11100110010011110011010001";

WHEN"010001"=>DATAOUT<="01000110010010110000000000";

WHEN"110001"=>DATAOUT<="10000110010011110000000000";

WHEN OTHERS=>DATAOUT<="10000110010011110000000000";

END CASE;

UA(5 DOWNTO 0)<=DATAOUT(5 DOWNTO 0);

D(19 DOWNTO 0)<=DATAOUT(25 DOWNTO 6);

END PROCESS;

END A;

(3) 微地址转换器F1

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F1 IS

PORT(

UA5,UA4,UA3,UA2,UA1,UA0:IN STD_LOGIC;

D:OUT STD_LOGIC_VECTOR(5 DOWNTO 0)

);

END F1;

ARCHITECTURE A OF F1 IS

BEGIN

D(5)<=UA5;

D(4)<=UA4;

D(3)<=UA3;

D(2)<=UA2;

D(1)<=UA1;

D(0)<=UA0;

END A;

(4) 微地址转换器F2

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F2 IS

PORT(

D:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

UA5,UA4,UA3,UA2,UA1,UA0:OUT STD_LOGIC

);

END F2;

ARCHITECTURE A OF F2 IS

BEGIN

UA5<=D(5);

UA4<=D(4);

UA3<=D(3);

UA2<=D(2);

UA1<=D(1);

UA0<=D(0);

END A;

(5) 微地址转换器F3

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F3 IS

PORT(

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

UA7,UA6,UA5,UA4,UA3,UA2,UA1,UA0:OUT STD_LOGIC

);

END F3;

ARCHITECTURE A OF F3 IS

BEGIN

UA7<=D(7);

UA6<=D(6);

UA5<=D(5);

UA4<=D(4);

UA3<=D(3);

UA2<=D(2);

UA1<=D(1);

UA0<=D(0);

END A;

(6) 微地址寄存器(aa)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MMM IS

PORT(

SE:IN STD_LOGIC;

T2:IN STD_LOGIC;

D:IN STD_LOGIC;

CLR:IN STD_LOGIC;

UA:OUT STD_LOGIC

);

END MMM;

ARCHITECTURE A OF MMM IS

BEGIN

PROCESS(CLR,SE,T2)

BEGIN

IF(CLR='0')THEN

UA<='0';

ELSIF(SE='0')THEN

UA<='1';

ELSIF(T2'EVENT AND T2='1')THEN

UA<=D;

END IF;

END PROCESS;

END A;

(7) 时序产生器(COUNTER)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER IS

PORT(

Q,CLR:IN STD_LOGIC;

T2,T3,T4:OUT STD_LOGIC

);

END COUNTER;

ARCHITECTURE A OF COUNTER IS

SIGNAL X:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

PROCESS(Q,CLR)

BEGIN

IF(CLR='0')THEN

T2<='0';

T3<='0';

T4<='0';

X<="00";

ELSIF(Q'EVENT AND Q='1')THEN

X<=X+1;

T2<=(NOT X(1)) AND X(0);

T3<=X(1) AND (NOT X(0));

T4<=X(1) AND X(0);

END IF;

END PROCESS;

END A;

(8) 1:2分配器单元(FEN2)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FEN2 IS

PORT(

WR,LED_B:IN STD_LOGIC;

X:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

W1,W2:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END FEN2;

ARCHITECTURE A OF FEN2 IS

BEGIN

PROCESS(LED_B,WR)

BEGIN

IF(LED_B='0' AND WR='0')THEN

W2<=X;

ELSE

W1<=X;

END IF;

END PROCESS;

END A;

(9) 寄存器单元(LS273)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LS273 IS

PORT(

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK:IN STD_LOGIC;

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END LS273;

ARCHITECTURE A OF LS273 IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

O<=D;

END IF;

END PROCESS;

END A;

(10) 状态条件寄存器单元(LS74)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LS74 IS

PORT(

LDFR:IN STD_LOGIC;

SF,CY,ZI:IN STD_LOGIC;

FS,FC,FZ:OUT STD_LOGIC

);

END LS74;

ARCHITECTURE A OF LS74 IS

BEGIN

PROCESS(LDFR)

BEGIN

IF(LDFR'EVENT AND LDFR='1')THEN

FC<=CY;

FZ<=ZI;

FS<=SF;

END IF;

END PROCESS;

END A;

(11) 微命令寄存器(MCOMMAND)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MCOMMAND IS

PORT(

T2,T3,T4,I3,I2,I1,I0:IN STD_LOGIC;

O:IN STD_LOGIC_VECTOR(19 DOWNTO 0);

P3,P1,P2,LOAD,LDPC,LDAR,LDIR,LDR0,LDR1,LDR2,R0_B,R1_B,R2_B,S1,S0,ALU_B,LDAC,LDDR,WR,CS,SW_B,LED_B,LDFR:OUT STD_LOGIC

);

END MCOMMAND;

ARCHITECTURE A OF MCOMMAND IS

SIGNAL DATAOUT:STD_LOGIC_VECTOR(19 DOWNTO 0);

BEGIN PROCESS(T2)

BEGIN

IF(T2'EVENT AND T2='1')THEN

DATAOUT(19 DOWNTO 0)<=O(19 DOWNTO 0);

END IF;

P3<=DATAOUT(0)

P2<=DATAOUT(1);

P1<=DATAOUT(2);

LDFR<=DATAOUT(3) AND T4;

LED_B<=DATAOUT(4);

SW_B<=DATAOUT(5);

CS<=DATAOUT(6);

WR<=DATAOUT(7) OR (NOT T3);

LDDR<=DATAOUT(8) AND T4;

LDAC<=DATAOUT(9) AND T4;

ALU_B<=DATAOUT(10);

S0<=DATAOUT(11);

S1<=DATAOUT(12);

--DATAOUT(13)对应RS_B信号,DATAOUT(14)对应RD_B信号

R2_B<=(DATAOUT(14)OR(NOT I1)OR I0)AND(DATAOUT(13)OR(NOT I3)OR I2);

R1_B<=(DATAOUT(14)OR I1 OR (NOT I0))AND(DATAOUT(13)OR I3 OR (NOT I2));

R0_B<=(DATAOUT(14)OR I1 OR I0)AND(DATAOUT(13)OR I3 OR I2);

LDR2<=T4 AND DATAOUT(15)AND I1 AND(NOT I0);

LDR1<=T4 AND DATAOUT(15)AND(NOT I1)AND I0;

LDR0<=T4 AND DATAOUT(15)AND(NOT I1)AND (NOT I0);

LDIR<=DATAOUT(16)AND T3;

LDAR<=DATAOUT(17)AND T3;

LDPC<=DATAOUT(18)AND T4;

LOAD<=DATAOUT(19);

END PROCESS;

END A;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MMM IS

PORT(

SE:IN STD_LOGIC;

T2:IN STD_LOGIC;

D:IN STD_LOGIC;

CLR:IN STD_LOGIC;

UA:OUT STD_LOGIC

);

END MMM;

ARCHITECTURE A OF MMM IS

BEGIN

PROCESS(CLR,SE,T2)

BEGIN

IF(CLR='0')THEN

UA<='0';

ELSIF(SE='0')THEN

UA<='1';

ELSIF(T2'EVENT AND T2='1')THEN

UA<=D;

END IF;

END PROCESS;

END A;

(12) 3选1数据选择器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX3 IS

PORT(

ID:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

SW_B,CS:IN STD_LOGIC;

N1,N2:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

EW:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX3;

ARCHITECTURE A OF MUX3 IS

BEGIN

PROCESS(SW_B,CS)

BEGIN

IF(SW_B='0')THEN

EW<=ID;

ELSIF(CS='0')THEN

EW<=N2;

ELSE

EW<=N1;

END IF;

END PROCESS;

END A;

(13) 4选1数据选择器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX4 IS

PORT(

C,D,E,F:IN STD_LOGIC;

X1,X2,X3,X4:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

W:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX4;

ARCHITECTURE A OF MUX4 IS

SIGNAL SEL:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

SEL<=F&E&D&C;

PROCESS(SEL)

BEGIN

IF(SEL="1110") THEN

W<=X1;

ELSIF(SEL="1101") THEN

W<=X2;

ELSIF(SEL="1011") THEN

W<=X3;

ELSIF(SEL="0111") THEN

W<=X4;

ELSE

NULL;

END IF;

END PROCESS;

END A;

(14) 程序计数器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY PC IS

PORT(

LOAD,LDPC,CLR:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END PC;

ARCHITECTURE A OF PC IS

SIGNAL QOUT:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(LDPC,CLR,LOAD)

BEGIN

IF(CLR='0')THEN

QOUT<="00000000";

ELSIF(LDPC'EVENT AND LDPC='1')THEN

IF(LOAD='0')THEN

QOUT<=D; --BUS->PC

ELSE

QOUT<=QOUT+1;--PC+1

END IF;

END IF;

END PROCESS;

O<=QOUT;

END A;

(15) 主存储器ROM16

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ROM16 IS

PORT(

ADDR:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CS:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ROM16;

ARCHITECTURE A OF ROM16 IS

BEGIN

DOUT<="10010000"WHEN ADDR="00000000" AND CS='0' ELSE--00 MOV1 R0,0

"00000000"WHEN ADDR="00000001" AND CS='0' ELSE--01

"10010010"WHEN ADDR="00000010" AND CS='0' ELSE--02 MOV1 R2,FFH

"11111111"WHEN ADDR="00000011" AND CS='0' ELSE--03

"11000000"WHEN ADDR="00000100" AND CS='0' ELSE--04 L1: CMP1 RO,9

"00001010"WHEN ADDR="00000101" AND CS='0' ELSE--05

"10000000"WHEN ADDR="00000110" AND CS='0' ELSE--06 JB L2

"00001010"WHEN ADDR="00000111" AND CS='0' ELSE--07

"11100000"WHEN ADDR="00001000" AND CS='0' ELSE--08 JMP L4

"00010100"WHEN ADDR="00001001" AND CS='0' ELSE--09

"00000001"WHEN ADDR="00001010" AND CS='0' ELSE--0A L2: IN1 R1

"11010000"WHEN ADDR="00001011" AND CS='0' ELSE--0B INC R0

"10100110"WHEN ADDR="00001100" AND CS='0' ELSE--0C CMP2 R1,R2

"10000000"WHEN ADDR="00001101" AND CS='0' ELSE--0D JL L3

"00010001"WHEN ADDR="00001110" AND CS='0' ELSE--0E

"11100000"WHEN ADDR="00001111" AND CS='0' ELSE--0F JMP L1

"00000100"WHEN ADDR="00010000" AND CS='0' ELSE--10

"01110110"WHEN ADDR="00010001" AND CS='0' ELSE--11 L3: MOV2 R1,R2

"11100000"WHEN ADDR="00010010" AND CS='0' ELSE--12 JMP L1

"00000100"WHEN ADDR="00010011" AND CS='0' ELSE--13

"11111000"WHEN ADDR="00010100" AND CS='0' ELSE--14

"00000000";

END A;