数字系统仿真与VHDL课程设计报告

——循环彩灯控制器

——2人抢答器

学院:

班级:

学号:

姓名:

实习时间:20##年1月4日—1月14日

指导老师:

一、实验设计的目的

本设计的任务是熟悉支持VHDL语言的软件,如Max Plus 2,ISP,FOUNDATION等,利用这一类软件使用VHDL语言进行设计编译仿真。本次设计的主要目的:

1、使学生熟练掌握相关软件Max Plus 2的使用操作。能对VHDL语言程序进行编译及调试,以及通过计算机仿真,得到正确的仿真波形图,并根据所得仿真波形图分析判断并改进所设计的电路。

2、在成功掌握软件操作基础上,让学生将所学数字电路的基础课知识与VHDL语言的应用型知识结合起来并与实际设计,操作联系起来,即“理论联系实际”。要求学生自主设计电路,编写程序,鼓励新思路,新方法,新观点。

3、完成可编程器件与VHDL语言课程设计,掌握设计语言技术的综合应用性。通过对以下几个设计:1、设计60进计数器(同步,异步);2、循环彩灯控制器;3、数字显示的秒表;4、2人抢答器;5、交通灯的设计等五个课题的设计、仿真、调试来具体完成。

4、熟悉系统的分析和设计方法,合理掌握选用集成电路的方法,初步接触EDA技术,为以后本专业的学习奠定良好的基础。

二、设计的工具及基本要求

Ⅰ、设计的工具

Ⅱ、设计基本要求

1、熟悉数字电路及相关专业课程的基本知识并能联系具体程序 ,编写出所设计电路的程序。

2、正确操作使用VHDL语言相关软件,能编译,调试,仿真VHDL语言程序得出正确的结果。

3、设计数字电路,编写程序,实现电路功能。通过本次设计应初步认识Max Plus 2 这一类软件的运用。

三、设计内容及操作

Ⅰ、设计的内容

1、设计一个2人抢答器----两人抢答,先抢为有效,用发光二极管显示是否抢到优先答题权。答题结束后,按复位键可重新抢答下一题。

2、循环彩灯控制器-----设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光管循环点亮。要求红发光管亮3秒,绿发光管亮2秒,黄发光管亮1秒。

3、设计60进计数器-----设计一个BCD码60进计数器。要求实现同步,异步两种情况,且规定个位显示0~9,十位显示0~5,均用4位二进制数表示。在此基础上试用VHDL语言描述中小规模集成电路74LS169。

4、数字显示的秒表----设计一块用数码管显示的秒表,能够准确的计时并显示。最大计时为59秒,最小精确到0.01秒。

5、交通灯控制器的程序设计----交通灯控制器:用于十字路口的交通灯控制器。要求:东西方向各有一组红,黄,绿灯用于指挥交通,红,黄,绿的持续时间分别为25s,5s,20s 。当有紧急情况(如消防车)时,两个方向均为红灯亮,计时停止,当特殊情况结束后,控制器恢复原来状态,正常工作。

Ⅱ、Max Plus 2 的基本操作

1、在所指定的保存盘中建立一个文件夹,打开Max Plus 2,点击File选择New再选择Text Eitor File建立新的文件夹,注意文件的命名一定要用英文字母,包括保存所指定的文件夹只能以数字或字母命名。

2、在所打开的窗口编写所设计的程序保存。在Flie中打开Project-name 在Dirctries,找到程序保存的文件,点击.vhd文件,再点击OK。

3、点击界面中Max Plus2中的Compiler,点击Start,发现有错误则返回源程序改正错,直到检测无错误为止。

4、点击Device在Device Family中选择MAX7000,Device中选择AUTO,点击OK。再点击Max Plus中的Wavefrom Editor 点击Node 选择Enter Nodes From...。再点击List导入。

5、根据自己所设计的要求修改图形,再打开Max Plus2仿真(Simulation) ,点击Start,如果没有错,则点击Open SCF可以得到设计结果。定时分析(Timing Analysis)。

四、设计的程序及结果分析

Ⅰ、设计2人抢答器

两人抢答,先抢为有效,用发光二极管显示是否抢到优先答题权。答题结束后,按复位键可重新抢答下一题。

1、设计程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity answer is

port(reset:in std_logic;

player:in std_logic_vector(2 downto 1);

out ,out2, fail 1:out std_logic);

end entity answer;

architecture example of answer is

signal a:std_logic_vector(2 downto 0);

begin

out2<=a(2);

out1<=a(1);

fail<=a(0);

process(reset,player) is

begin

if(reset='0') then

a<="000";

else

case player is

when "00"=>a<="000";

when "01"=>a<="010";

when "10"=>a<="100";

when others=>a<="001";

end case;

end if;

end process;

end architecture example;

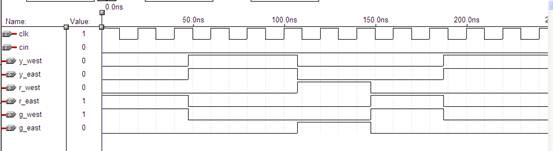

2、设计仿真波形图如下:

3、程序及波形图分析

程序:library ieee到use ieee.std_logic_unsigned.all为库文件的调用,entity answer is到end answer is为实体,其中port括号中为电路设计的各个输入输出端口,architecture example of answer is到end architecture example为构造体,是程序执行部分,process(reset,player) is为进程语句,

Begin

if(reset='0') then

a<="000";

else

case player is

when "00"=>a<="000";

when "01"=>a<="010";

when "10"=>a<="100";

when others=>a<="001";

由上段程序可知当reset为0时,输出为无效,否则执行语句四个when语句,结果赋值如上。

仿真波形图:在仿真时已经设置好开始时间和结束时间,根据以上的波形图可知,当复位信号reset处于高电平有效(高低电平可以根据自己所设计的情况自己定义),当Play2先抢答时有效,则Out2输出有效,Out1输出无效。当Play1先抢答有效,则Out2输出有效,Out输出无效。当两人同时抢答则视为无效,fail输出为高电平。按复位键抢答重新开始。

Ⅱ、循环彩灯控制器

设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光管循环点亮。要求红发光管亮3秒,绿发光管亮2秒,黄发光管亮1秒。

1、设计程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY colorlight IS

PORT(clk,clr:IN STD_LOGIC;

red,green,yellow:OUT STD_LOGIC);

END ENTITY colorlight;

ARCHITECTURE example OF colorlight IS

SIGNAL dout:STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL m:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

red<=dout(2);

green<=dout(1);

yellow<=dout(0);

PROCESS(clk) IS

BEGIN

IF(clr='1') THEN

m<="001";

ELSIF(clk'EVENT AND clk='1') THEN

IF(m="110") THEN

m<="001";

ELSE

m<=m+1;

END IF;

CASE m IS

WHEN "001"=>dout<="100";

WHEN "010"=>dout<="100";

WHEN "011"=>dout<="100";

WHEN "100"=>dout<="010";

WHEN "101"=>dout<="010";

WHEN "110"=>dout<="001";

WHEN OTHERS=>dout<="111";

END CASE;

END IF;

END PROCESS;

END ARCHITECTURE;

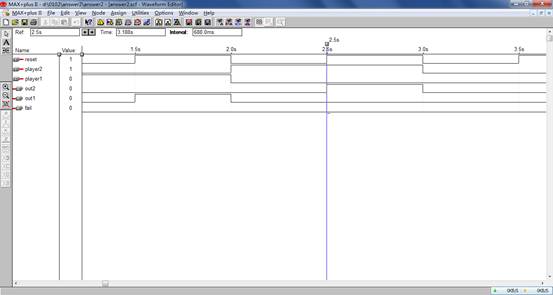

2、程序仿真波形图如下:

3、程序及波形图分析:

程序:LIBRARY IEEE到USE IEEE.STD_LOGIC_UNSIGNED.ALL为库文件调用,ENTITY colorlight IS到END ENTITY colorlight为实体部分,其中PORT为输入输出端口,clk,clr:IN STD_LOGIC中clk为脉冲信号,clr为使能端。ARCHITECTURE example OF colorlight IS到 END ARCHITECTURE为构造体部分,当clk'EVENT AND clk='1'输出为110,clr='1'输出为001

CASE m IS

WHEN "001"=>dout<="100";

WHEN "010"=>dout<="100";

WHEN "011"=>dout<="100";

WHEN "100"=>dout<="010";

WHEN "101"=>dout<="010";

WHEN "110"=>dout<="001";

WHEN OTHERS=>dout<="111";

END CASE;为程序执行执行赋值部分。

波形图分析:在仿真时已经设置好开始时间和结束时间,根据以上的波形图可知,当clk信号处于高电平(高低电平可以根据自己所设计的情况自己定义),红发光管最先亮灯(高电平表示亮灯),时间为3s,3s之后绿发光管开始亮灯2s,2s结束黄发光管亮1s,以此循环亮灯,直到仿真结束时间。

五、总结与心得

本次数字系统仿真与VHDL课程设计的课程设计时间主要是20##年1月4日至14日这两周时间。主要的设计任务是将本学期VHDL硬件描述语言与数字逻辑电路设计和上学期所学的数字电路中所学的知识运用的实践中去,提高自己在理论与实践的相结合能力,进一步掌握本专业的各项知识,为以后的专业学习打下良好的基础。从一些基础掌握一些本专业所学的知识了解一些基础的实验工具如Max Plus2的使用,本次的设计基本达到预期的效果,得出设计的结果。但本次数字系统仿真与VHDL课程设计也存在着一些不足之处,于此将本次设计的收获和不足总结为以下几点:

第一、在程序的编写过程中,通过发现问题再到解决问题,在这过程中,逐渐的掌握了Max Plus2的使用以及在使用过程中的一些注意事项,对更好的学习理论知识起到了一定的帮助。

第二、初步了解对电路的设计的思维和方法,在这方面还有很多不足的地方,理论知识不强,专业的课外知识不充足。在编写程序的过程中遇到了一定的麻烦,感受到了正确的不一定是实用的。

第三、本次的设计得益于网络资源及图书馆资料的帮助,同时我也认识到在未来的学习中我们不仅要从老师那里学习知识,更多的是合理的正确的利用网络资源及图书资源。

本次数字系统仿真与VHDL课程设计的课程设计在老师的精心指导下,我们不仅仅学会里用Max Plus2编写设计的程序并进行编译仿真得出相应的结果,更重要的是让我在这其中学会了很多其他的东西。本专业的学习是很辛苦很需要耐心和意志力的,同时必须保持大脑处于思考状态,在这不多的时间里我们应该更好的利用时间去思考我们所学的知识。在与老师的交流中,我感受到我所设计仅仅只是一部分,奇妙的东西很多,同时深刻的领会到我们不仅会做出东西,更重要的是运用到实际中去。同时我在这期间认识到了求真务实精神的重要性,特别是在老师的教导下,让我感触很多,作为大学生在求学路上不应想着如何去走捷径,而是如何看透问题的本质,真正的做到学以致用。经过此次让我感受颇多,因为我们要有着自己思维和理念去追求知识。

附加:

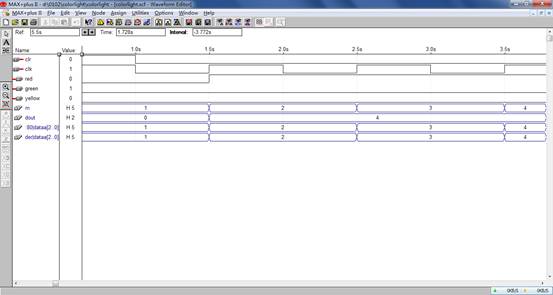

Ⅰ、交通灯控制器

用于十字路口的交通灯控制器。要求:东西方向各有一组红,黄,绿灯用于指挥交通,红,黄,绿的持续时间分别为25s,5s,20s 。当有紧急情况(如消防车)时,两个方向均为红灯亮,计时停止,当特殊情况结束后,控制器恢复原来状态,正常工作。

设计程序如下:

Library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jtd is

port(clk,cin: in std_logic;

r_east,r_west,y_east,y_west,g_east,g_west: out std_logic);

end entity jtd;

architecture behave of jtd is

signal n: std_logic_vector(2 downto 0);

begin k1:process(clk,cin)is

begin

if(cin='1') then

n<="111";

elsif(clk'event and clk='1') then

if(n="110") then

n<="000";

else

n<=n+'1';

end if;

end if;

end process k1;

k2:process(n)is

begin

if(n="000")then

r_east<='1';

r_west<='0';

y_east<='0';

y_west<='0';

g_east<='0';

g_west<='1';

elsif(n="001")then

r_east<='1';

r_west<='0';

y_east<='0';

y_west<='0';

g_east<='0';

g_west<='1';

elsif(n="010")then

r_east<='0';

r_west<='0';

y_east<='1';

y_west<='1';

g_east<='0';

g_west<='0';

elsif(n="011")then

r_east<='0';

r_west<='0';

y_east<='1';

y_west<='1';

g_east<='0';

g_west<='0';

elsif(n="100")then

r_east<='0';

r_west<='0';

y_east<='1';

y_west<='1';

g_east<='0';

g_west<='0';

elsif(n="101")then

r_east<='0';

r_west<='1';

y_east<='0';

y_west<='0';

g_east<='1';

g_west<='0';

elsif(n="110")then

r_east<='0';

r_west<='1';

y_east<='0';

y_west<='0';

g_east<='1';

g_west<='0';

else

r_east<='1';

r_west<='1';

y_east<='0';

y_west<='0';

g_east<='0';

g_west<='0';

end if;

end process k2;

end architecture behave;

仿真波形图如下: