八多路智力竞赛抢答器设计

目录

一前言·························································1

1设计内容及要求·········································1

2实验内容及方法·········································2

3工作过程简介············································2

二、正文·····················································4

1系统概述··················································4

2单元电路设计方案和原理说明·······················4

抢答器电路设计···········································4

定时电路设计··············································6

3电路的安装与调试······································8

4心得与体会···············································9

三、元器件明细表··········································10

四、参考文献················································10

前言

一、设计内容及要求:

设计内容:本课题要求设计一台可供8名选手参加比赛的智力竞赛抢答器。

设计要求:

1.基本功能

(1)抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

(2)设置一个系统清除和抢答控制开关S,该开关由主持人控制。用来控制系统清零(编号显示数码管灭灯)和抢答的开始。

(3)抢答器具有锁存与显示功能。即抢答开始后,选手按动按钮,锁存相应的编号,并在编号显示器上显示该编号。同时封锁输入编码电路,禁止其他选手抢答。优先抢答选手的编号一直保持到主持人将系统清除为止。

2.扩展功能

(1)抢答器具有定时抢答功能。要求定时器开始倒计时,并用定时显示器显示倒计时时间。

(2)参赛选手在设定时间(30秒)内抢答,抢答有效,同时定时器停止倒计时,编号显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止。

(3)如果定时抢答时间已到,却没有选手抢答时,本次抢答无效,系统封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

二、实验内容及方法

1.组装调试抢答器电路。

2.设计可预置时间的定时电路,并进行组装和调试。当输人1Hz的时钟脉冲信号时,要求电路能进行减计时,当减计时到零时,能输出低电平有效的定时时间到信号。

3.完成定时抢答器的联调,注意各部分电路之间的时序配合关系。然后检查电路各部分的功能,使其满足设计要求。

三,工作过程简介

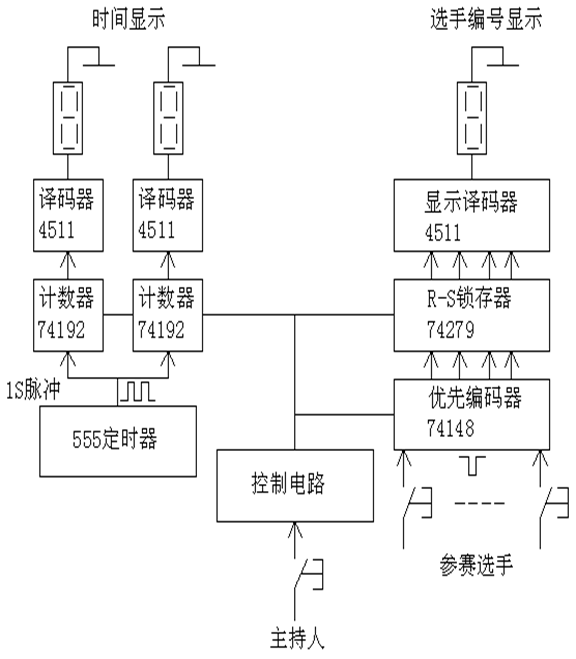

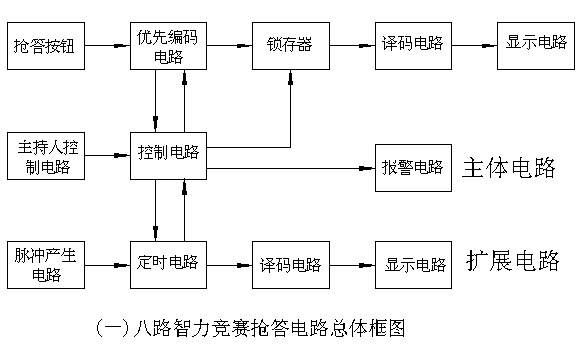

定时抢答器的总体框图(如图1.1)所示,它由主体电路和扩展电路两部分组成。主体电路完成基本的抢答功能,即开始抢答后,当选手按动抢答按钮时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答。扩展电路完成定时抢答的功能。

图1

如图所示为总体方框图。工作原理为:接通电源后,主持人将开关拨到“清零”状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置;开始"状态,宣布“开始”抢答器工作。定时器倒计时,选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示。当一轮抢答之后,定时器停止、禁止二次抢答、定时器显示剩余时间。如果再次抢答必须由主持人再次操作“清除”和“开始”状态开关。

正文

一、 系统概述

如图(一)所示为八路智力竞赛抢答器的总体方框图。其工作原理如下:

抢答器系统原理框图如上所示。它由主体电路和扩展电路两部分组成,主体电路完成基本抢答后,选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答,扩展电路完成定时抢答的功能

抢答器系统原理框图如上所示。它由主体电路和扩展电路两部分组成,主体电路完成基本抢答后,选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答,扩展电路完成定时抢答的功能

二、单元电路设计方案和原理说明

⒈抢答器电路设计

其原理说明:

(1)、抢答电路的功能有两个:一是能分辨出选手按键的先后,并锁存优先抢答者的编号,供译码显示译码电路用;二是要使其它选手按键操作无效。

(2)、选用优先编码器74LS148、RS锁存器、译码器4511组成抢答电路

(3)、抢答电路工作原理:当控制开关置于“清除”位置时,RS触发器的R端为低电平,输出Q4—Q1全为低电平。此时4511的BI=0, 显示器灭灯;74LS148选通输入ST=0,74LS148处于工作状态,而锁存电路不工作。当控制开关置于“开始”位置时,优先编码电路和锁存电路同时处于工作状态,当有选手按键抢答时,如5号选手优先按5号键,则74LS148输出Y2Y1Y0=010,YEX=0,经RS锁存后,Q1=1,BI=1,7448工作,Q4Q3Q2=101,经4511驱动译码后,显示器显示数字5。Q1=1使74LS148为高电平。即74LS148禁止工作,封锁其它按键输入,当按下的按键松开后,74LS148的YEX为高电平,但由于Q1输出仍为高电平不变,所以74LS148仍处于不工作状态,其它按键的输入信号不被接受,这就保证抢答者的优先性及抢答电路的准确性。

如图(二)所示为八路智力竞赛抢答器的抢答电路单元图,

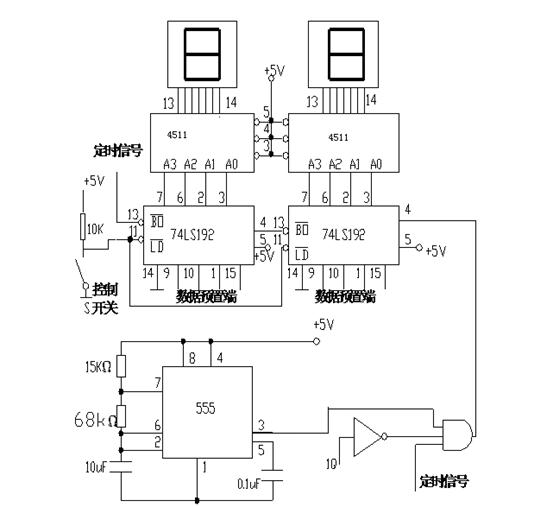

⒉定时电路设计

节目主持人根据抢答器的难易程度,设计一次抢答的时间,通过预置时间电路对计数器进行预置,选用十进制同步加减计数器74LS192进行设计,计数器的时钟脉冲由秒脉冲电路提供。具体电路如图3。

原理及设计:该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、4511译码电路和2个7段数码管即相关电路组成。具体电路如图3所示。两块74LS192实现减法计数,通过译码电路4511显示到数码管上,其时钟信号由时钟产生电路提供。原理及设计:该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、4511译码电路和2个7段数码管即相关电路组成。具体电路如图3所示。两块74LS192实现减法计数,通过译码电路4511显示到数码管上,其时钟信号

由时钟产生电路提供。按键弹起后,计数器开始减法计数工作,并将时间显示在共阴极七段数码显示管4511 上,当有人抢答时,停止计数并显示此时的倒计时时间;如果没有人抢答,且倒计时时间到时, 输出低电平到时序控制电路,控制报警电路报警,同时以后选手抢答无效。结合我们的实际经验及考虑到元器件的成本,我们选择的电阻值为R1=15K,R2=68K,C=10uF,代入到上式中即得 ,即秒脉冲。

具体电路如图3所示。

三、电路的安装与调试

这也过程说起来并不难,但也可以说是比较难的,因为按理说只要把电路图原理弄懂了,按照原理图进行连接电路就行了,而实际上这么多的接口真正的做到每一个都不漏每一个都不会错还是比较难的,而且连起线来也是比较的慢比较的繁琐,第一面包板太小两个人一起连的话感觉相互挡着了,而且连好了彼此也不熟悉对方是怎么连的,到最后检查电路时会很困难,所以我和同组的肖康生就决定我们一个人负责看电路图知道布局和连线,另外一个人就只进行连线,这样以来的话,连起线来就比较的快不会相互挤着,而且还能够避免很多错误,最后实物电路的路线基本上两个人都会比较的熟悉自己是怎么接德鲁,等下检查线路时就会比较的容易。

总的来说,在安装电路的过程中,除了电路的布局要求美观以外,在电路的安装过程中就没有什么难的地方。接下来就是电路的调试了,在电路连接的过程中,我们采取的方法比较的好,连线的速度也比较的快,而且错误也比较的少,所以,在接好先后多电路进行调试时,第一遍我们就已经基本成功了,只是在倒计时环节,倒计时的数据总是无法与设计时的相同,本来设计的是从30到0的倒计时,然而,出现的数字倒计时总是停在39与30两数字之间,而且有的时候甚至还出现的加数计时的现象,数字变到了49,这一步让我们比较的棘手,以为检查连线实在是没有错误,而且对电路进行分块的检查与测试时也并没出现错误,就只是在74LS192这一块芯片上数据输出有问题,地位与高位的Q0有脉冲输出,而Q1、Q2、Q3皆没有脉冲信号出来。想了半天也没结果,我们只能再次对线路进行检查,确认无误后我们决定了暂时放弃检查电路,准备想老师求助,老师帮我们仔细的检查了个芯片的接线与电路工作时各个芯片的管脚的电平,最后也认为我们的电路没连错,但是肯定存在问题,最后经过老师的仔细排查,最终找出了原因,使我们的192号芯片5号端未接高电平,使芯片在4号管脚有减速脉冲输入时5号管脚的加速脉冲要停止工作对其置1。经过改正后我们的电路安装就圆满完成了,而且总体的看来布局和连线方面也做得比较到位,这样电路的安装于调试就基本完成了。

四、心得与体会

通过两周的课程设计,使我对数字电路有了进一步的了解,我的理论知识掌握得更扎实,动手能力明显提高。同时,通过网上搜索等多方面的查询资料,我学到许多在书本上没有的知识,也认识到理论联系实践的重要。在制作当中遇到了许多以前没遇到的困难。我们利用许多的方法去解决所遇到的问题。这次设计,让我感受最深的是在仿真的阶段遇到一些的问题,计时电路不能随抢答而停止,以及在实物连接后,抢答电路不能倒计时等问题。最后我们还是老师的帮助下检查出了错误并进行改正的,我觉得我们自己一定要具备一定的检查、排除电路故障的能力。我深刻认识到了“理论联系实际”的这句话的重要性与真实性。而且通过对此课程的设计,我不但知道了以前不知道的理论知识,而且也巩固了以前知道的知识。最重要的是在实践中理解了书本上的知识,明白了学以致用的真谛。

在此我要感谢老师的谆谆教导和同学们的帮助,我相信这十几天的不懈努力会给我未来的学习带来很多的启发,我会在以后的工作生活中更好的理论联系实际,证明自己的能力。

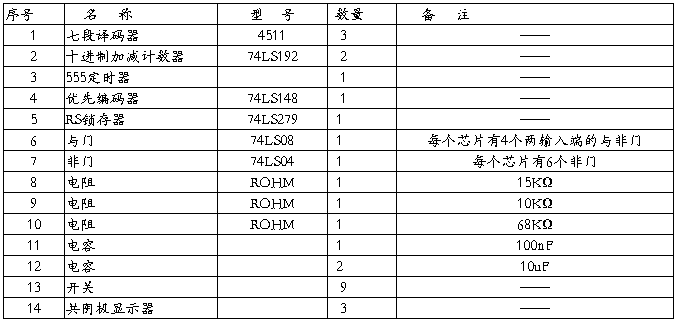

元器件明细表

参考文献

1. 彭介华。电子技术课程设计指导。北京,高等教育出版社,2002。

2. 阎石。数字电子技术基础(第四版)。北京,高等教育出版社,2002。

3. 陈明义。电子技术课程设计实用教程。长沙,中南大学出版社,2002。

4. 杨志中等。电子技术课程设计。北京,机械工业出版社,2008。

第二篇:智力竞赛抢答器的设计

黑龙江科技学院

课程设计任务书

一、设计题目:

二、设计的主要内容:

指导教师:

日 期:

教师评语:

评阅成绩:

评 阅 人:

日 期:

黑龙江科技学院

课程设计任务书

一、设计题目: 智力竞赛抢答器的设计

二、设计的主要内容: 设计一个智力竞赛抢答器要求具有四路抢答输入,能够识别最先抢答的信号,显示该台号;对回答问题所用的时间进行计时、显示、超时报警;可以预置回答问题的时问;同时具有复位功能,倒计时启动功能。

指导教师:郝维来

日 期:

教师评语:

评阅成绩:

评 阅 人:

日 期:

摘 要

本文介绍了一种智力竞赛抢答器的基本原理和功能要求,并采用VHDL语言实现了这种抢答器的程序设计。本文所采用的模块化、逐步细化的设计方法有利于系统的分工合作、并且能够及早发现各子模块及系统中的错误,提高系统设计的效率,特别适用于可编程逻辑器件的应用设计。把要设计的系统划分为五个功能模块:抢答信号判别电路,最先抢答的台号显示控制电路,分频电路,倒计时及计时值显示电路,扬声器控电路.

关键词:VHDL 自顶向下的设计方法 抢答器 可编程逻辑器件

第1章 概述

1.1 简单介绍

20世纪90年代,引起数字系统设计方法发生突破性变革的技术是VHDL(Very High Speed Integrated Circuit Hardware De scription Language,超高速集成电路硬体描述语言)。它是一种以IEEE一1076标准所规范的硬件描述语言,主要用于从算法级、寄存器级到门级的多种抽象设计层次的数字系统建模,已成为电子设计自动化(EDA)的一种重要手段。现代数字系统的设计多采用自顶向下的设计方法,属阶层式设计‘1'。自顶向下设计的各个阶层,可全部用图形也可全部用VHDL语言进行描述,还可采用混合方式,即顶层模块用图形描述,底层元件用VHDL描述等。

1.2 实际应用

工厂、学校和电视台等单位常举办各种智力竞赛, 抢答记分器是必要设备。在我校举行的各种竞赛中我们经常看到有抢答的环节,举办方多数采用让选手通过举答题板的方法判断选手的答题权,这在某种程度上会因为主持人的主观误断造成比赛的不公平性。为解决这个问题,我们小组准备就本次大赛的机会制作一个低成本但又能满足学校需要的四路智力竞赛抢答器。抢答器在竞赛中有很大用处,它能准确、公正、直观地判断出第1抢答者。通过抢答器的指示灯显示、数码显示和警示蜂鸣等手段指示出第1抢答者。

第2章 智力抢答器的设计思想

2.1 智力竞赛抢答器的基本原理

设计一个智力竞赛抢答器要求具有四路抢答输入,能够识别最先抢答的信号,显示该台号;对回答问题所用的时间进行计时、显示、超时报警;可以预置回答问题的时问;同时具有复位功能,倒计时启动功能。

2.2功能模块划分

根据对抢答器的功能要求,把要设计的系统划分为五个功能模块:抢答信号判别电路,最先抢答的台号显示控制电路,分频电路,倒计时及计时值显示电路,扬声器控电路.

2.3 功能分析

抢答信号判别电路在系统复位后,对A、B、c、D四路抢答信号进行判别,输出端G3一G0与A—D一一对应,优胜者对应的G为“1”,其余的G为“0”,且将结果锁存。完成抢答判别的同时,输出端R输出有效信号,对扬声器进行选通。

分频电路用于产生倒计时电路所需的周期为l s的时钟脉冲,分频系数视输入时钟cLK的频率而定。

台号显示控制电路将输入信号G3一G0转换为BCD码,以驱动数码管,显示台号。

倒计时及时间显示控制电路由ti,tset信号预置答题时问;由复位信号INI将答题时间作为初值赋给倒计时计数器;由计数允许信号EN启动计数。输出信号为time,sel与out,其中sel与out为扬声器选通控制信号。

扬声器控制电路使系统只在两种情况下输出驱动扬声器的脉冲信号:一种是倒计时计数器处于禁止计数状态(EN无效),并且完成初始化,开始对抢答信号进行判别,当某参赛组抢先按下按键,系统在输出该组台号信息的同时,输出脉冲信号;一种是确认优先抢答的参赛组后,启动倒计时计数器计数(使EN有效),当计数到“0”时,输出脉冲信号。

根据上述分析得出了各功能模块间的接口关系,见图1

至此,已从设计要求出发生成了抢答器的顶层文件。

2.4 用VHDL自顶向下实现智能抢答器的设计

采用VHDL、以层次化设计的方法对抢答器进行逻辑功能描述。本设计用单个VHDL实体进行逻辑设计,以若干进程分别对各功能模块进行描述。对外部端口在实体中定义,对各模块间的接口信号,作为内部节点,在结构体中用SIGNAL定义。抢答器的VHDL源文件qdq.Vhd见程序清单。仿真结果如下:

第3章 结论

用VHDL设计的智力竞赛抢答器在计算机上仿真通过后,下载到可编程逻辑器件中,整个设计过程相对于传统的设计方法,有较大的突破,重要体现在:

1) VHDL的设计采用自顶向下的设计方法?。这种模块化、逐步细化的方法有利于系统的分工合作、并且能够及早发现各子模块及系统中的错误,提高系统设计的效率。

2) VHDL有非常丰富的数据类型:位、位矢量、整数、实数、数组、结构等,可以非常灵活地描述系统总线和实现算法。

3) VHDL引入工作库,存放各种已编译的资源,使得一个设计的子模块可以被另一设计引用,达到资源共享的目的。

4) VHDL是标准化硬件描述语言,屏蔽了具体工艺及器件的差异,不会因工艺及器件的变化而变化。嵋f同时由于VHDL是国际标准,易于ASIC和EDA领域的国际交流。VHDL作为先进的硬件描述语言,以其灵活、简洁的设计风格在电路设计中发挥着越来越重要的作用。

参考文献

[l] 侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计.西安:西安电子科技大学出版社,1997

[2] 常青,陈辉煌.可变成专用集成电路及其应用与设计实践经验.北京:国防工业出版社,1998

[3] 张千里,陈光英.网络安全新技术[M].北京:人民邮电出版社,2003

[4] 李镇江,戴荚伙,陈越.IDs入侵检测系统研究.计算机工程[J].200l,27(4),7—9

[5] 赵轩,王勇军等.基于状态检测的硬件防火墙实现技术研究,全国网络与信息安全技术研讨会,2004,296—300

程序清单:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY Responder is

PORT (A,B,C,D,test,INI,EN,clk:in std_logic;

tih:in std_logic_vector(5 downto 4);

til:in std_logic_vector(3 downto 0);

bell:out std_logic;

timeh:buffer std_logic_vector(5 downto 4);

timel:buffer std_logic_vector(3 downto 0);

obcd:out std_logic_vector(2 downto 0));

end Responder;

ARCHITECTURE one of Responder is

signal G: std_logic_vector(3 downto 0);

signal R: std_logic;

signal clk1: std_logic;

signal sel,outc: std_logic;

signal tah: std_logic_vector(5 downto 4);

signal tal: std_logic_vector(3 downto 0);

begin

LOCK :PROCESS(A,B,C,D,INI,CLK)

--"描述LOCK模块的进程"

begin

if (INI='1') then R<='0'; G<="0000";

elsif rising_edge(clk) then

if (A='1' OR G(3)='1' )AND NOT( G(0)='1' OR G(1)='1' OR G(2)='1')

THEN G(3)<='1';

END IF;

IF (B='1' OR G(2)='1') AND NOT(G(0)='1'OR G(3)='1' OR G(1)='1')

THEN G(2)<='1';

END IF;

if (C='1' OR G(1)='1' )AND NOT( G(0)='1' OR G(3)='1' OR G(2)='1')

THEN G(1)<='1';

END IF;

if (D='1' OR G(0)='1' )AND NOT( G(1)='1' OR G(3)='1' OR G(2)='1')

THEN G(0)<='1';

END IF;

R<=A OR B OR C OR D;

END IF;

END PROCESS LOCK;

CB :PROCESS(CLK)

variable Q :std_logic_vector(8 downto 0);

BEGIN

IF (CLK'EVENT AND CLK='1')THEN

IF (Q="111111111")THEN Q:="000000000";

ELSE Q:=Q+1;

END IF;

END IF;

CLK1<=Q(8);

END PROCESS CB;

COUNT :PROCESS(tih,til,test,timeh,timel,INI,EN,CLK1)

--"描述COUNT模块的进程"

BEGIN

IF rising_edge(CLK1)THEN

IF(TEST='1')THEN

tah<=tih;

tal<=til;

END IF;

IF (INI='1')THEN

TIMEH<=TIMEH;

TIMEL<=TIMEL;

ELSIF(TIMEH=0 AND TIMEL=0)THEN

TIMEH<=TIMEH;

TIMEL<=TIMEL;

ELSIF(TIMEL=0)THEN

TIMEL<="1001";

TIMEH<=TIMEH-1;

ELSE

TIMEL<=TIMEL-1;

TIMEH<=TIMEH;

END IF;

END IF;

END PROCESS;

OBCD<= "001"WHEN G="1000"ELSE

--"用并行语句描述"

"010"WHEN G="0100"ELSE

--"DECODER模块"

"011"WHEN G="0010"ELSE

"100"WHEN G="0001"ELSE

"000";

bell<=((R AND sel)OR OUTC)AND CLK;

--"用并行语句描述BELL模块"

sel<='1'when (TIMEH=TAH AND TIMEL =TAL) ELSE '0';

OUTC<='1' WHEN ((TIMEH=0)AND (TIMEL=0)AND (EN='0')AND (INI='0'))ELSE '0';

END ONE;