Verilog实验报告

---第四次 交通灯

班级:集电0802班

姓名: 张鹏

学号: 04086057

序号: 16

一、规范

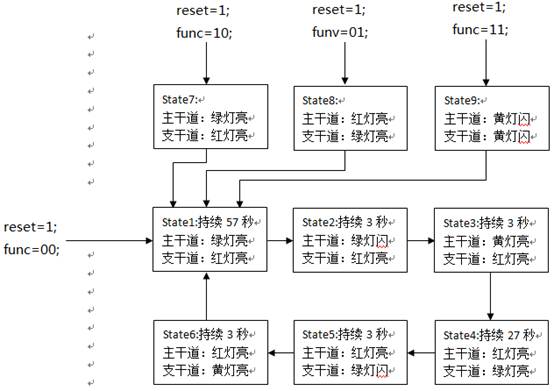

(1) 具有开关功能:当reset=0时 红绿灯关闭,使主支干道六个灯全灭;

(2) 具有四个功能:当reset=1且func=2’b00时,主干道和支路正常计数;

且func=2’b01时,支干道一直绿灯,主干道一直红灯;

且func=2’b10时,主干道一直绿灯,支干道一直红灯;

且func=2’b11时,主干道和支干道一直黄灯闪;

(3) 计数器频率:运行频率2Hz计数器;

(4) 信号灯种类:红、黄、绿;

(5) 信号灯计执行时间关系:主干道:绿灯常亮+绿灯闪+黄灯=支干道:红灯常亮;

此设计中:

主干道:绿灯常亮=57s,T绿灯闪=3s,T黄灯亮=3s

支干道:绿灯常亮=15s,T绿灯闪=3s,T黄灯亮=3s

(6) 信号灯到计时功能:信号灯预置后,开始执行2Hz计数器;

(7) 信号灯跳转功能:当各信号灯计时至T时在下一个时钟信号上升沿到来时自动转为下一状态;

(8) 信号灯各状态跳转关系:绿-黄-红-绿;

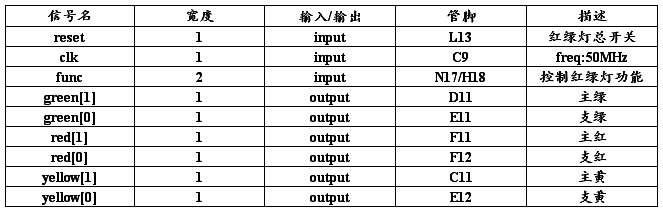

二、输入输出定义

reset,clk, func[1:0] ,green[1:0],red[1:0],yellow[1:0]

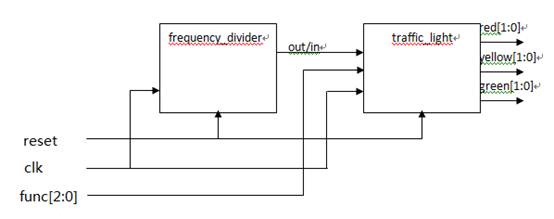

三、模块设计

状态转移图:

四、测试代码

module frequency_divider_small(reset,clk,out); //重写一个小分频模块测试交通灯主模块功能

input reset,clk;

output out;

reg [1:0] temp;

reg out;

always @ (posedge clk or negedge reset)

if (!reset)

temp<=2'b00;

else

temp<=(temp==2'b11)?2'b00:temp+2'b01;

always @ (temp)

out=(temp==2'b11);

endmodule

module test_traffic_light;

reg reset,clk;

reg [1:0] func;

wire [1:0] green;

wire [1:0] red;

wire [1:0] yellow;

traffic_light simulation(.reset(reset),.clk(clk),.func(func),.green(green),.red(red),.yellow(yellow));

always #10 clk=~clk;

initial

begin

reset=0;

clk=1;

func=2'b00;

#20 reset=1;

#21000 func=2'b01;

#10000 func=2'b10;

#10000 func=2'b11;

end

endmodule

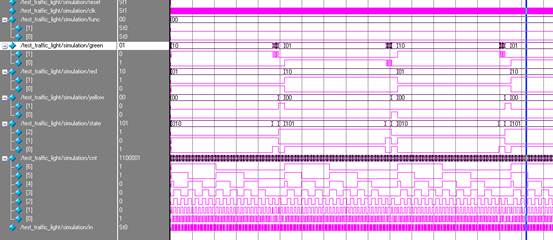

波形:

五、源代码

module frequency_divider(reset,clk,out);//分频模块,把50MHz时钟分成半秒计时器

input reset,clk;

output out;

reg [5:0] mol1,mol2;

reg [6:0] mol3,mol4;

reg out1,out2,out3,out;

always @ (posedge clk or negedge reset)//把25000000分成40*40*125*125

if(!reset)

mol1<=6'd0;

else

mol1<=(mol1==6'd39)?6'd0:mol1+6'd1;

always @ (posedge clk or negedge reset)

if(!reset)

mol2<=6'd0;

else if(out1)

mol2<=(mol2==6'd39)?6'd0:mol2+6'd1;

always @ (posedge clk or negedge reset)

if(!reset)

mol3<=7'd0;

else if(out2)

mol3<=(mol3==7'd124)?7'd0:mol3+7'd1;

always @ (posedge clk or negedge reset)

if(!reset)

mol4<=7'd0;

else if(out3)

mol4<=(mol4==7'd124)?7'd0:mol4+7'd1;

always @ (mol1 or mol2 or mol3 or mol4)

begin

out1=(mol1==6'd39);

out2=((mol2==6'd39)&&out1);

out3=((mol3==7'd124)&&out2);

out=((mol4==7'd124)&&out3);

end

endmodule

module traffic_light(reset,clk,func,green,red,yellow);//交通灯主模块

input reset,clk;

input [1:0] func;

output [1:0] green,red,yellow;

reg [1:0] green,red,yellow;

reg [2:0] state;

reg [6:0] cnt;

wire in;

parameter greentime1=6'd57;//主干道绿灯时间

parameter greentime0=6'd27;//支干道绿灯时间

parameter yellowtime=3'd3;//黄灯时间,绿灯闪时间

frequency_divider fenpin(.reset(reset),.clk(clk),.out(in));//调用分频模块

always @ (posedge clk or negedge reset)

if(!reset)

begin

cnt<=7'd0;

state<=3'd1;

green<=2'b00;

red<=2'b00;

yellow<=2'b00;

end

else

if(in)//分频器结果当主模块始能

if(func==2'b00)//选择不同功能控制开关

if(cnt==7'd0)

case(state)//选择不同状态

3'd1:begin

cnt<=greentime1<<1;

state<=3'd2;

green<=2'b10;

red<=2'b01;

yellow<=2'b00;

end

3'd2:begin

cnt<=yellowtime<<1;

state<=3'd3;

end

3'd3:begin

cnt<=yellowtime<<1;

state<=3'd4;

green<=2'b00;

red<=2'b01;

yellow<=2'b10;

end

3'd4:begin

cnt<=greentime1<<1;

state<=3'd5;

green<=2'b01;

red<=2'b10;

yellow<=2'b00;

end

3'd5:begin

cnt<=yellowtime<<1;

state<=3'd6;

end

3'd6:begin

cnt<=yellowtime<<1;

state<=3'd1;

green<=2'b00;

red<=2'b10;

yellow<=2'b01;

end

endcase

else

begin

cnt<=cnt-7'd1;//倒计数,计数结束进入下一状态

case(state)

3'd3:green[1]<=cnt[0];//主干道绿灯闪

3'd6:green[0]<=cnt[0];//支干道绿灯闪

endcase

end

else if(func==2'b10)//主干道常绿,支干道常红

begin

cnt<=0;

state<=3'd1;

green<=2'b10;

red<=2'b01;

yellow<=2'b00;

end

else if(func==2'b01)//主干道常红,支干道常绿

begin

cnt<=0;

state<=3'd1;

green<=2'b01;

red<=2'b10;

yellow<=2'b00;

end

else if(func==2'b11)//主干道,支干道黄灯一直闪

begin

cnt<=0;

state<=3'd1;

green<=2'b00;

red<=2'b00;

yellow[1]<=~yellow[1];

yellow[0]<=~yellow[1];

end

endmodule

第二篇:交通灯verilog

我写的verilog交通灯代码下载到FPGA实验箱上怎么时间不准确呢? 我写了一个verilog交通灯的代码,然后下载到fpga上面,怎么和设定的时间不一致

? yanhaobeyond

? 中级粉丝

2 当中的不一致,怎么回事呢?? 谢谢!! module trafficlight(clk,sm,sb,mr,my,mg,br,by,bg); input clk,sm,sb; output reg mr,my,mg,br,by,bg; integer count,count1; reg clk_n; reg [2:0] state;

parameter s0=2'b000,

s1=2'b001,

s2=2'b010,

s3=2'b011,

s4=2'b100;

always @(posedge clk)

if (count==25000000)

begin

count<=0;

clk_n<=!clk_n;

end

else count=count+1;

always @(posedge clk_n)

case (state)

s0: begin

if((sm==1)&&(sb==0))

begin

mr<=0;

my<=0;

mg<=1;

br<=1;

by<=0;

bg<=0;

end

else state<=s1;

end

s1: begin

if((sm==1)&&(sb==1)) begin

if(count1==45)

begin

state<=s2;

count1<=0;

end

else

begin

mr<=0;

my<=0;

mg<=1;

br<=1;

by<=0;

bg<=0;

count1<=count1+1; end

end

else if((sm==1)&&(sb==0)) state<=s0;

end

s2: begin

if((sm==1)&&(sb==1)) begin

if(count1==5)

begin

state<=s3;

count1<=0;

end

else

begin

mr<=0;

my<=1;

mg<=0;

br<=1;

by<=0;

bg<=0;

count1<=count1+1; end

end

else if((sm==1)&&(sb==0)) state<=s0;

end

s3: begin

if((sm==1)&&(sb==1)) begin

if(count1==25)

begin

state<=s4;

count1<=0;

end

else

begin

mr<=1;

my<=0;

mg<=0;

br<=0;

by<=0;

bg<=1;

count1<=count1+1; end

end

else if((sm==1)&&(sb==0)) state<=s0;

end

s4: begin

if((sm==1)&&(sb==1)) begin

if(count1==5)

begin

state<=s1;

count1<=0;

end

else

begin

mr<=1;

my<=0;

mg<=0;

br<=0;

by<=1;

bg<=0;

count1<=count1+1; end

end

else if((sm==1)&&(sb==0)) state<=s0;

end

default: state<=s0; endcase

endmodule