第二篇:EDA实验报告

实验报告

实验名称 Verilog数字系统设计实验

学 院 信息工程学院

年级班别

学 号

学生姓名

指导教师

20##年 12 月 1 日

实验一、时序逻辑

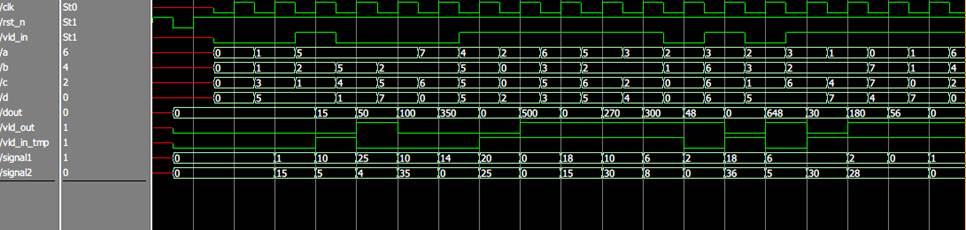

1. 功能:实现一个四输入的乘法器,即 s=a*b*c*d。流水线实现,寄存器之间仅包含一个乘法器 (注:2级流水线。每次输入有效(vld_in=1)后的第2个时钟周期输出有效(vld_out=1),并由dout输出结果)

module flowline2(clk , rst_n , vld_in , a , b , c , d , dout ,vld_out ,);

//参数定义

parameter A_W = 4;

parameter B_W = 4;

parameter C_W = 4;

parameter D_W = 4;

parameter DOUT_W = 16;

//输入信号定义

input clk ;

input rst_n ;

input vld_in ;

input[A_W-1:0] a ;

input[B_W-1:0] b ;

input[C_W-1:0] c ;

input[D_W-1:0] d ;

//输出信号定义

output[DOUT_W-1:0] dout ;

output vld_out;

//输出信号reg定义

reg [DOUT_W-1:0] dout ;

reg vld_out;

reg vld_in_tmp;

//中间信号定义

reg [DOUT_W/2-1:0] signal1;

reg [DOUT_W/2-1:0] signal2;

//时序逻辑,把a*b和c*d的积赋值给中间信号

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

signal1<=0;

end

else begin

signal1<=a*b;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

signal2<=0;

end

else begin

signal2<=c*d;

end

end

//中间信号的积赋值给输出值

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout<=16'd0;

end

else begin

dout<=signal1*signal2;

end

end

//输出有效值延时

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

vld_in_tmp<=0;

end

else begin

vld_in_tmp<=vld_in;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

vld_out<=0;

end

else begin

vld_out<=vld_in_tmp;

end

end

endmodule

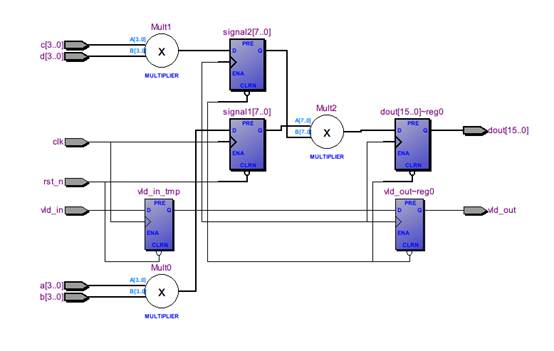

2. 设计思路:

(1) a*b和c*d的值先分别存放在寄存器signal1和signal2中

(2) signal1*signal2的值即a*b*c*d的值通过寄存器输出

(3) 由于是2级流水线,故vld_dout输出有效信号应慢vld_in一拍,故通过延时来实现

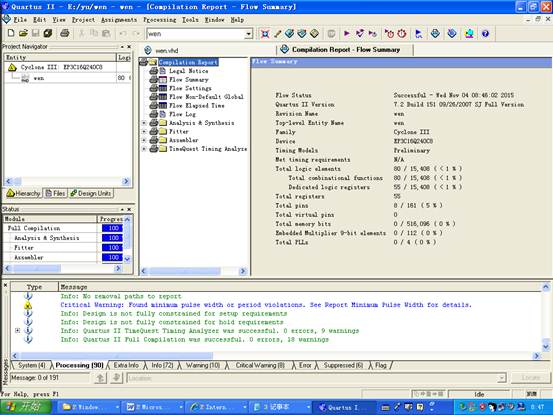

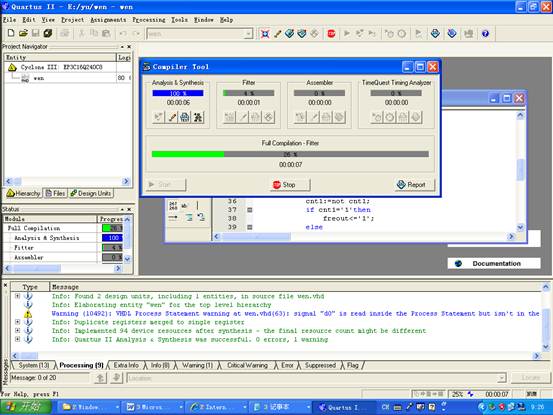

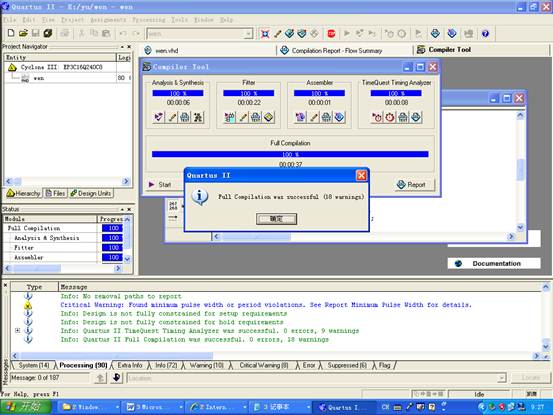

3. 电路模块:

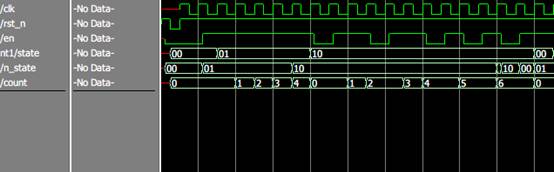

4. 仿真结果(采用Modelsim仿真):

实验二、组合逻辑

1. 功能:实现一个四输入的乘法器,即 s=a*b*c*d。改变电路结构:优化成(a*b)*(c*d) (注:直接出结果,只有输出才用到D触发器)。即1级流水线

module flowline1(clk , rst_n , vld_in , a , b , c , d , dout , vld_out,);

//参数定义

parameter A_W = 4;

parameter B_W = 4;

parameter C_W = 4;

parameter D_W = 4;

parameter DOUT_W = 16;

//输入信号定义

input clk ;

input rst_n ;

input vld_in ;

input[A_W-1:0] a ;

input[B_W-1:0] b ;

input[C_W-1:0] c ;

input[D_W-1:0] d ;

//输出信号定义

output[DOUT_W-1:0] dout ;

output vld_out;

//输出信号reg定义

reg [DOUT_W-1:0] dout ;

reg vld_out;

//中间信号定义

reg [7:0] signal1;

reg [7:0] signal2;

//组合逻辑,a或b的值一改变signal1即改变

always@(*)begin

signal1=a*b;

end

//组合逻辑,c或d的值一改变signal2即改变

always @(*)begin

signal2=c*d;

end

//时序逻辑

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout<=0;

end

else begin

dout<=signal1*signal2;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

vld_out<=0;

end

else begin

vld_out<=vld_in;

end

end

endmodule

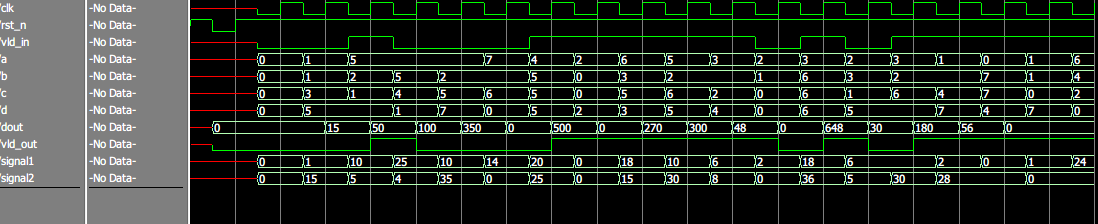

2. 设计思路:

(1) 因为只有输出才用到寄存器,故a*b和c*d都用组合逻辑即可。

(2) 输出有效信号vld_dout需慢输入有效信号vld_in一个时钟周期

3. 模块电路:

4. 仿真结果(采用Modelsim仿真):

实验三、状态机

1. 功能:状态机有三个状态,IDLE,S1和S2。在IDLE状态,如果en=1,则跳到S1状态,否则保持不变;在S1状态时,统计en=1的次数,如果达到5次,则跳到S2状态,否则保持不变;在S2状态,统计en=1的次数,如果达到7次,则跳回到IDLE状态,否则保持不变。

module statemachine3(clk , rst_n , en , state ,);

//三个状态参数定义

parameter IDLE = 2'b00 ;

parameter S1 = 2'b01 ;

parameter S2 = 2'b10 ;

input clk ;

input rst_n ;

input en ;

output [1:0] state ;

reg [1:0] state ;

reg [1:0] n_state ;

reg [3:0] count ;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

state<=IDLE;

end

else begin

state<=n_state;

end

end

//count在不同状态下统计en==1的次数

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

count<=0;

end

else if(state==S1)begin

if(count==4&&en==1)begin

count<=0;

end

else if(en==1)begin

count<=count+1;

end

end

else if(state==S2)begin

if(count==6&&en==1)begin

count<=0;

end

else if(en==1)begin

count<=count+1;

end

end

else begin

count<=0;

end

end

//状态转换

always@(*)begin

case(state)

IDLE :if(en==1)begin

n_state=S1;

end

else begin

n_state=IDLE;

end

S1 :if(count==4&&en==1)begin

n_state=S2;

end

else begin

n_state=S1;

end

S2 :if(count==6&&en==1)begin

n_state=IDLE;

end

else begin

n_state=S2;

end

default :n_state=IDLE;

endcase

end

endmodule

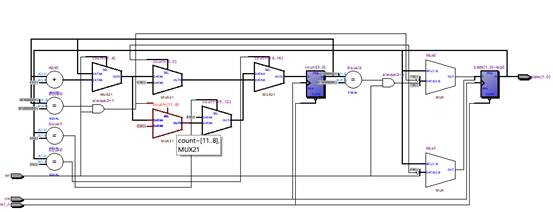

2. 设计思路:

(1) 确定三个状态转换条件,画出状态图

(2) 采用计数器count在不同状态下进行计数

(3) 满足条件进行状态转换,根据当前状态值state转换下一状态值n_state;

(4) 在时钟上升沿来时把n_state赋值给state输出

3. 模块电路:

4. 仿真结果(采用Modelsim仿真):