实验报告

课程名称: 数字电路实验 第 7 次实验

实验名称: 计数器的应用

实验时间: 20## 年 5 月 22 日

实验地点: 组号

学号:

姓名:

指导教师: 评定成绩:

一、实验目的:

1.学习计数器的基本结构。

2.掌握中规模计数器的功能及其应用。

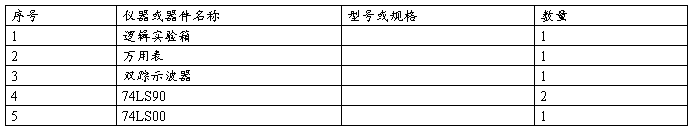

二、实验仪器:

三、实验原理:

计数器是一种能够统计输入脉冲个数的时序电路,计数是日常生活中最常遇见的算术动作,所以计数器应用广泛,种类繁多,按工作方式分,有同步和异步两类;按计数模值分,有二进制、十进制和任意进制;按计数顺序分,有加法、减法和可逆(双向)之分。目前常用的计数器都已有

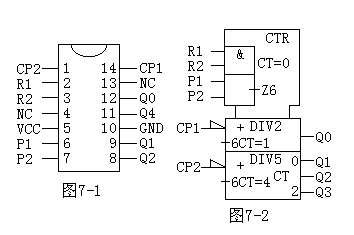

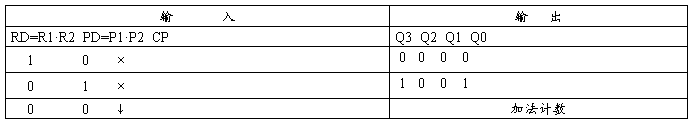

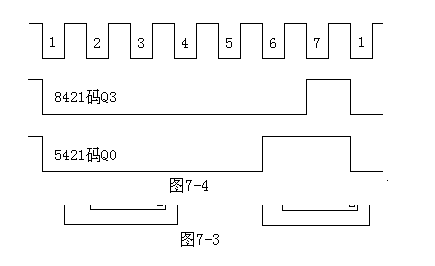

成品,一般来说,它们具备清除或预置功能,本实验采用的计数器为TTL双极型数字集成逻辑门电路74LS90,是一块二-五-十进制异步计数器,外形为双列直插,引脚排列如图7-1所示,图中的NC表示此脚为空脚,不接线,逻辑符号如图7-2所示。其中R1、R2为两个异步清0端,P1、P2为两个异步置9端,CP1、CP2为两个时钟输入端,Q0~Q3为计数输出端, 74LS90的功能表见表7-1,因此可知:当R1=R2=P1=P2=0时,时钟从CP1引入,Q0输出为二进制;时钟从CP2引入,Q3输出为五进制;时钟从CP1引入,而Q0接CP2,即二进制的输出与五进制的输入相连,则Q3、Q2、Q1、Q输出为十进制(8421BCD码);时钟从CP2引入,而Q3接CP1,即五进制的输出与二进制的输入相连,则Q0、Q3、Q2、Q1输出为十进制(5421BCD码)。要构成任意进制计数可利用异步清0端或预置端,如M=7的两种电路,见图7-3,但计数状态不一样,输出波形占空比不同,见图7-4。如果计数模值超过10,就需要多块集成电路构成。

表7-1

按8421BCD码: 按5421BCD码:

Q3 Q2 Q1 Q0 Q0 Q3 Q2 Q1

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 0

…… ……

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

…… ……

1 0 0 1 1 1 0 0

0 0 0 0 0 0 0 0

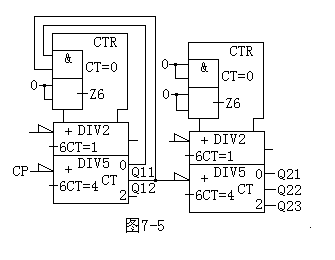

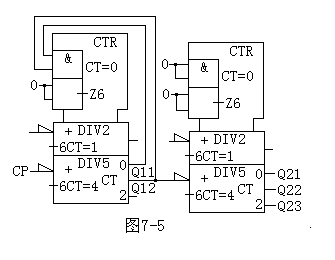

图7-5为可实现M=15的逻辑图之一,它是由一块三进制和一块五进制串联而成,其中Q12、Q11为三进制(00、01、10)输出,Q23、Q22、Q21为五进制(000、001、010、011、100)输出。

四、实验内容:

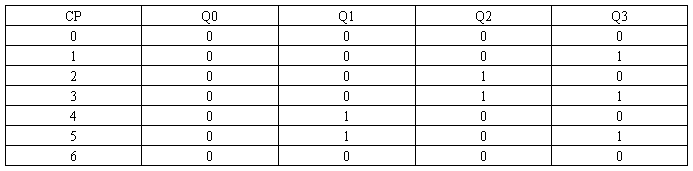

1.用74LS90实现计数

(1)CP1接实验箱上的单脉冲信号,或接f=1~2Hz的连续脉冲,CP2接Q0,RD=PD=0,输出Q3、Q2、Q1、Q0先接指示灯显示,再接实验箱上的数码显示输入D、C、B、A,记录两种显示结果。

(2)CP2接实验箱上的时钟信号,CP1接Q3,RD=PD=0,输出Q0、Q3、Q2、Q1接指示灯显示,记录显示结果。

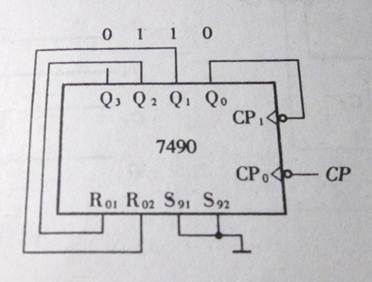

(3)用74LS90实现M=6的计数,记录显示结果。

电路图:

2.用74LS90实现9分频、11分频、15分频

计数器CP接实验箱上的时钟信号,取f=1KHz左右,并接双踪示波器的一个输入端口,计数器输出接双踪示波器的另一个输入端口,观察CP与Q的波形,记录显示的波形。

答:做法:

(1) 9分频,用置零法,一块7490,到9时置零,任选一个输出端接入示波器

(2) 11分频,也用置零法,两块7490,先接成20进制计数器,做法是把第一块的Q3接入第二块的CP1,然后把第二块的Q0输出

(3) 15分频,电路图如下:

五、实验思考:

1.74LS90作为5421码输出时,按Q3、Q2、Q1、Q0排列,则结果怎样?如果输出Q0、Q3、Q2、Q1接数码显示输入D、C、B、A,能否显示1~9,为什么?

答:(1)如果仍按照5421码对结果做解码的话会出错,因为会出现如0110这样的伪码。

(2)不能正确显示,因为数码管内自带的是按8421码解码的译码器,如果按照5421码接入自然得不到正确结果。

第二篇:数字电路实验3 计数器

实验八 计数器

一、实验目的

1. 熟悉由集成触发器构成的计数器电路及其工作原理。

2. 熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路

所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器

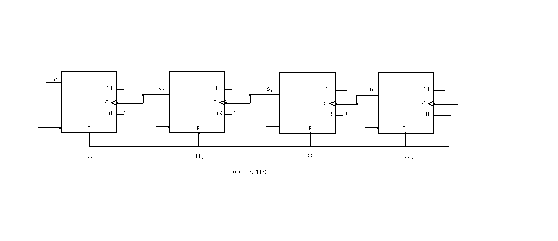

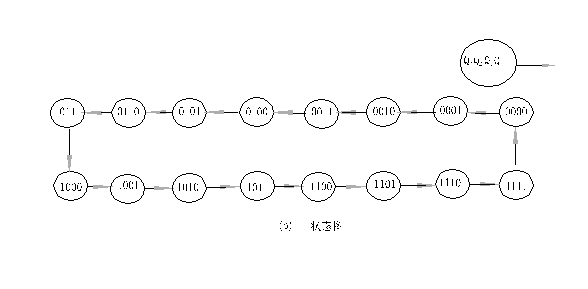

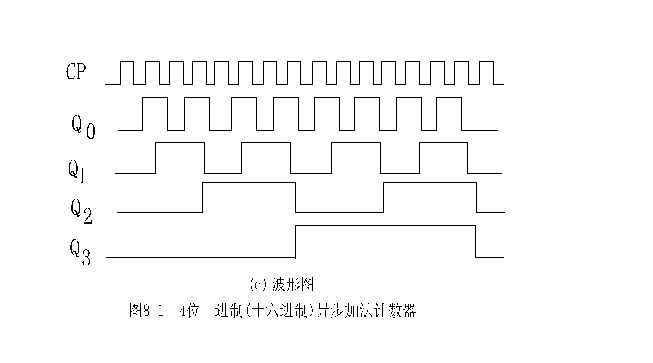

异步二进制加法计数器是比较简单的。图1.8.1(a)是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图1.8.1(b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FFO(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的CP端接FF0的Q0端,因而当FFO(QO)由1→ 0时,FF1翻转。类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1 是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。所以Q0 、Q1、Q2、Q3分别实现了二、四、八、十六分频,这就是计数器的分频作用。

2.异步二进制减法计数器

异步二进制减法计数器原理同加法计数器,只要在图1.8.1(a)所示加法计数器逻辑电路中将低位触发器Q端接高位触发器CP端换成低位触发器Q端接高位触发器CP端即可。

图1.8.2为异步二进制减法计数器。

如果有D触发器,则可把D触发器光转换成T’触发器,然后根据74LS74 D触发器是上升沿触发,画出逻辑电路图。用74LS74构成的4位二进制计数器逻辑电路如图1.8.3所示,

3.其它进制计数器

在很多实际应用中,往往需要不同的计数进制满足各种不同的要求。如电子钟里需要六十进制、二十四进制,日常生活中的十进制,等等。

在图1.8.3中虚线所示,我们只要把Q3和Q1通过与非门接到FF0、FF1、FF2、FF3四个触发器的清零端  ,即可实现从十六进制转换为十进制计数器。如要实现十四进制计数器,可以把Q3、 Q2 、Q1 相“与非”后,接触发器FF3~FF0的清零端

,即可实现从十六进制转换为十进制计数器。如要实现十四进制计数器,可以把Q3、 Q2 、Q1 相“与非”后,接触发器FF3~FF0的清零端  。同理可实现其它进制的异步计数器。

。同理可实现其它进制的异步计数器。

“8421码”十进制计数器是常用的,图1.8.4为下降沿触发的JK触发器构成的异步十进制计数器(8421码)。

要组成100进制(8421码)计数器可以把两个8421计数器级联起来即可实现。

4.集成计数器

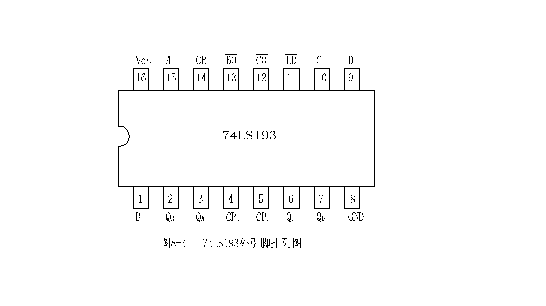

在实际工程应用中,我们一般很少使用小规模的触发器去拼接而成各种计数器,而是直接选用集成计数器产品。例如74LS161是具有异步清零功能的可预置数4位二进制同步计数器。74LS193是具有带清除双时钟功能的可预置数4位二进制同步可逆计数器。图1.8.5为74LS161惯用逻辑符号和外引脚排列图。表1.8.1为74LS161的功能表。

由表1.8.1可知,74LS161具有下列功能:

由表1.8.1可知,74LS161具有下列功能:

①  =0,不管其它输入端为何状态,输出均为0。

=0,不管其它输入端为何状态,输出均为0。

②  =1,

=1, =0,在CP上升沿时,将d0~d3置入Q0~Q3中。

=0,在CP上升沿时,将d0~d3置入Q0~Q3中。

③  =

=  =1,若CTT=CTP=1,对CP脉冲实现同步计数。

=1,若CTT=CTP=1,对CP脉冲实现同步计数。

④  =

=  =1,若CTP. =0,计数器保持。

=1,若CTP. =0,计数器保持。

进位CO在平时状态为0,仅当CTT=1且Q0~Q3全为1时,才输出1(CO= CTT.Q3. Q2. Q1 .Q0)。

体现74LS193功能的波形图如图1.8.6所示,其主要功能如下:

① CR=1为清零,不管其它输入如何,输出均为0。

② CR=0,  =0,置数,将D、C、B、A置入QD、QC、QB、QA中。

=0,置数,将D、C、B、A置入QD、QC、QB、QA中。

③ CR=0, =1,在CPD=1,CPU有上升沿脉冲输入时,实现同步二进制加法计数。在CPU=1,CPD 有上升沿脉冲输入时,实现同步二进制减法计数。

=1,在CPD=1,CPU有上升沿脉冲输入时,实现同步二进制加法计数。在CPU=1,CPD 有上升沿脉冲输入时,实现同步二进制减法计数。

④ 在计数状态下(CR=0, =1时,CPD=1时)CPU输入脉冲,进行加法计数,仅当计数到QD~QA全1时,且CPU为低电平时,进位

=1时,CPD=1时)CPU输入脉冲,进行加法计数,仅当计数到QD~QA全1时,且CPU为低电平时,进位 输出为低电平;减法计数时(CPU=1,CPD为脉冲输入,CR=0,

输出为低电平;减法计数时(CPU=1,CPD为脉冲输入,CR=0, =1),仅当QD~QA全0时,且CPD为低电平时,借位

=1),仅当QD~QA全0时,且CPD为低电平时,借位 输出为低电平。

输出为低电平。

三、实验内容及步骤

1. 异步二进制加法计数器

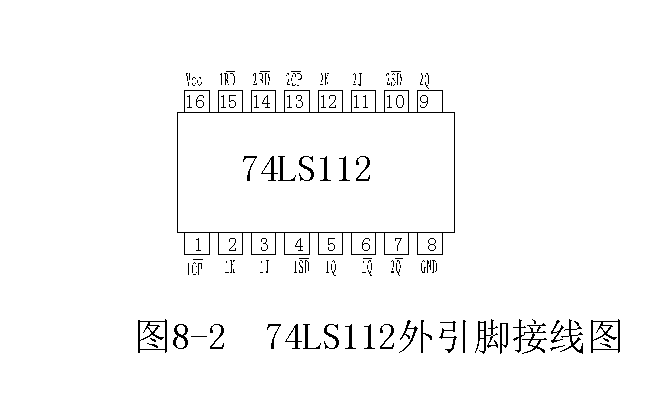

a. 在实验箱中选四个JK触发器,(也可自行插入二片74LS112双JK触发器)按图

1.8.1(a)接线。74LS112管脚排列如实验七图1.7.14所示。

b. 其中CP接单次脉冲(或连续脉冲),R端接实验箱上的复位开关K5。

c. 接通实验系统(箱)电源,先按复位开关K5(复位开关平时处于1,LED灯亮,按下为0,LED灯灭,再松开开关,恢复至原位处于1,LED灯亮),计数器清零。

d. 按动单次脉冲(即输入CP脉冲),计数器按二进制工作方式工作。这时 Q3、Q2、Q1、Q0的状态应和图1.8.1(b)一致。如不一致,则说明电路有问题或接线有误,需重新排除错误后,再进行实验论证。

2. 异步二进制减法计数器

a. 按图1.8.2(a)接线。实际上,只要把异步二进制加法计数器的输出脉冲引线由Q端换成  端,即为异步二进制减法计数器。

端,即为异步二进制减法计数器。

b. 输入单次脉冲CP,观察输出Q3、 Q2、 Q1、 Q0的状态是否和图(b)一致。

c. 将CP脉冲连线接至接续脉冲输出(注意,必须先断开与单次脉冲连线,再接到连续脉冲输出上),调节连续脉冲旋钮,观察计数器的输出。

3. 用D触发器构成计数器

a. 按图1.8.3接线,即为4位二进制(十六进制)异步加法计数器,验证方法同上,从本实验不难发现,用D触发器构成的二进制计数器与JK触发器构成的二进制计数器的接线(即电路连接)不一样,原因是74LS74双D触发器为上升沿触发,而74LS112双JK触发器为下降沿触发。

b. 构成十进制异步计数器

在图1.8.3中,将Q3和Q1两输出端,接至与非门的输入端,输出端接计数器的四个清零端  。图中虚线所示(原来

。图中虚线所示(原来 接复位按钮K5的异线应断开)。按动单次脉冲输入,就开发现其逻辑功能为十进制(8421码)计数器。

接复位按钮K5的异线应断开)。按动单次脉冲输入,就开发现其逻辑功能为十进制(8421码)计数器。

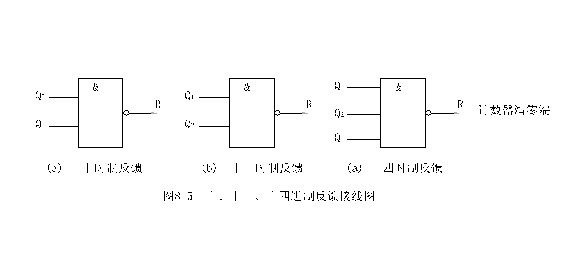

若要构成十二进制或十四进制计数器,则只需将Q3、Q2、Q1进行不同组合即可。如图1.1.8所示分别为十进制、 十二进制、十四进制计数器反馈接线图。

十二进制、十四进制计数器反馈接线图。

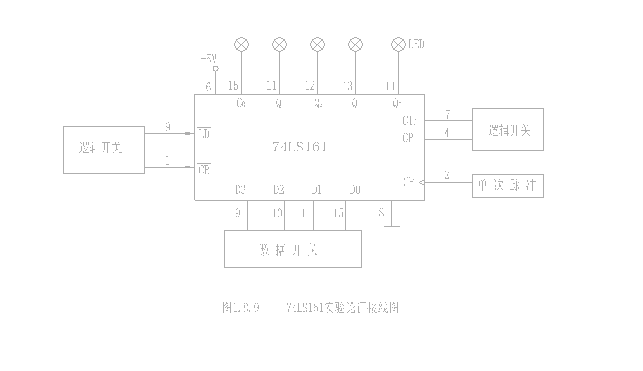

4. 集成计数器74LS161的功能验证和应用

a. 将74LS161芯片插入实验箱IC空插座中,按图1.8.9接线。16脚接电源+5V,8脚接地,D0、D1、D2、D3接四位数据开关,Q0、Q1、Q2、Q3、CO接五只LED发光二极管,置数控制端 ,清零端

,清零端 ,分别接逻辑开关K1、K2,CTP、CTT分别接另二只逻辑开关K3、K4,CP接单次脉冲。

,分别接逻辑开关K1、K2,CTP、CTT分别接另二只逻辑开关K3、K4,CP接单次脉冲。

接线完毕,接通电源,进行74LS161功能验证。

①清零:拨动逻辑开关K2=O(

①清零:拨动逻辑开关K2=O( =0),则输出Q0~Q3全为0,即LED全灭。

=0),则输出Q0~Q3全为0,即LED全灭。

②置数:设数据开关D3 D2 D1D0=1010,再拨动逻辑开关K1=0,

K2=1(即 =0,

=0, =1),按动单次脉冲(应在上升沿时),输出Q3 Q2 Q1Q0=1010,即D3~D0数据并行置入计数中,若数据正确,再设置D3~D0为0111,输入单次脉冲,观察输出正确否(Q3~Q0=0111)。如不正确,则找出原因。

=1),按动单次脉冲(应在上升沿时),输出Q3 Q2 Q1Q0=1010,即D3~D0数据并行置入计数中,若数据正确,再设置D3~D0为0111,输入单次脉冲,观察输出正确否(Q3~Q0=0111)。如不正确,则找出原因。

③保持功能:置K4=K2=1( =

= =1),K3或K4=0(即CTP=0或CTP=0),则计数器保持,此时若按动单次脉冲输入CP,计数器输出Q3~Q0不变(即LED状态不变)。

=1),K3或K4=0(即CTP=0或CTP=0),则计数器保持,此时若按动单次脉冲输入CP,计数器输出Q3~Q0不变(即LED状态不变)。

④计数:置K1=K2=1( =

= =1),K3=K4=1(CTP=CTT=1),则74LS16处于加法计数器状态。这时,可按动单次脉冲输入CP,LED显示十六进制计数状态,即从000→0001→…111进行顺序计数,当计到计数器全为1111时,进位输出LED发光二极管亮(即CO=1,CO=G .Q3.Q2 .Q1.Q0)。

=1),K3=K4=1(CTP=CTT=1),则74LS16处于加法计数器状态。这时,可按动单次脉冲输入CP,LED显示十六进制计数状态,即从000→0001→…111进行顺序计数,当计到计数器全为1111时,进位输出LED发光二极管亮(即CO=1,CO=G .Q3.Q2 .Q1.Q0)。

将CP接到单次脉冲的导线切断,连至连续脉冲输出端,这时可看到二进制计数器连续翻转的情况.

b. 十进制计数也可用74LS161方便地实现.将Q3和Q4通过与非门反馈后接到 端,见图1.8.10(a)所示.利用此法,74LS16可以构成小于模16的任意进制计数器.

端,见图1.8.10(a)所示.利用此法,74LS16可以构成小于模16的任意进制计数器.

此外,还可利用另一控制端 把74LS16设计成十进制计数器,如图1.8.10(b)所示。

把74LS16设计成十进制计数器,如图1.8.10(b)所示。  同步置数法,就是利用

同步置数法,就是利用 这一端给一个零信号,使=D3 D2 D1D0"0110"6这个数并行置入计数器中,然后以6为基值向上计数直至15(共十个状态),即0110→0111→1000→1001→1010→1011→1100→1101→1110→1111。所以利用15="1111"状态CO为1的特点,反相后接到

这一端给一个零信号,使=D3 D2 D1D0"0110"6这个数并行置入计数器中,然后以6为基值向上计数直至15(共十个状态),即0110→0111→1000→1001→1010→1011→1100→1101→1110→1111。所以利用15="1111"状态CO为1的特点,反相后接到 ,而完成十进制计数器这一功能.同样道理,也可以从0、1、2等数值开始,再取中间十个状态为计数状态,取最终状态的“1”信号相与非后,作为

,而完成十进制计数器这一功能.同样道理,也可以从0、1、2等数值开始,再取中间十个状态为计数状态,取最终状态的“1”信号相与非后,作为 的控制信号,就可完成十进制计数器。例如若D3D2D1D0=“0000”=0则计到9;D3D2D1D0=“0001”=1则计到10,等等。

的控制信号,就可完成十进制计数器。例如若D3D2D1D0=“0000”=0则计到9;D3D2D1D0=“0001”=1则计到10,等等。

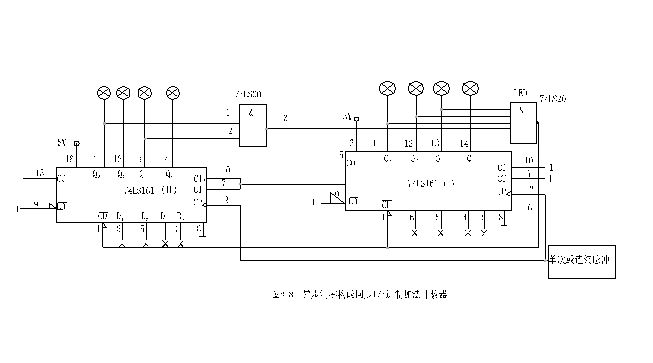

c. 用两片或三片74LS161完成更多位数的计数器,实验电路见图1.8.11和图1.8.12。其中图1.8.11为两片74LS161构成174进制计数器的两种接法。图1.8.12为三片构成4096进制计数器的两种接法。按图1.8.11和图1.8.12分别进行实验论证。

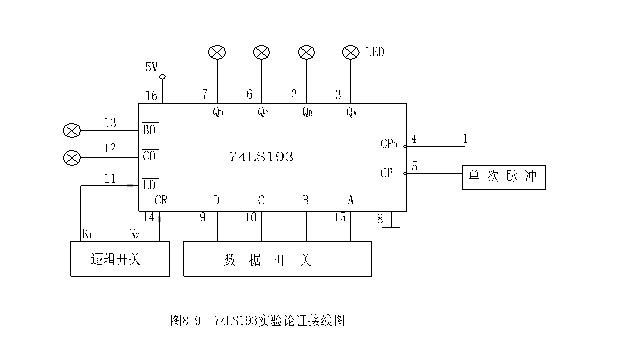

5. 集成计数器74LS193的功能验证

74LS193计数器的使用方法和74LS161很相似。图1.8.13为其实验接线图。按图1.8.13接线,进行74LS193的功能验证。 a.清零:74LS193的CR端与74LS161不同,它是“1”信号起作用,即CR=1时,74LS193清零.实验时,将CR置1,观察输出QD、Qc、QB、QA的状态,并和逻辑功能;图1、8、6、比较。

a.清零:74LS193的CR端与74LS161不同,它是“1”信号起作用,即CR=1时,74LS193清零.实验时,将CR置1,观察输出QD、Qc、QB、QA的状态,并和逻辑功能;图1、8、6、比较。

b. 计算;74LS193可以加、减计数,在计数状态时,即CR=0,

=1,CPD=1时,CPU输入脉冲,为加法计数器;CPU=1,CPD输入脉冲,计数器为减法计数器。

=1,CPD=1时,CPU输入脉冲,为加法计数器;CPU=1,CPD输入脉冲,计数器为减法计数器。

c. 置数:CR=0,置数据并关为任一二进数(如0111),拨动逻辑开关K1=O( =O)则数据D、C、B、A已送入QD~QA中。

=O)则数据D、C、B、A已送入QD~QA中。

d. 用74LS193也可实现任意进制计数器,这里不一一实验了。读者可以试做一下其它几个任意进制的计数器。

四、实验器材

1. THDM-1系列数字电子技术实验系统 1台

2. 直流稳压电源 SG1731 2台

3. 集成电路:74LS74,74LS112,74LS193 各2片

74LS161 3片

74LS04,74LS08,74LS20 各1片

五、预习要求

1. 复习计数器电路的工作原理和电路组成结构。

2. 熟悉中规模集成计数器电路74LS161,74LS193的逻辑功能、外引脚排列和使用方法。

六、实验报告要求

1. 整理实验电路,画出时序状态图和波形图。

2. 若用74LS193构成60进制计数器,电路如何?

3. 总结74LS161二进制计算器的功能的特点。