本科生毕业论文(设计)开题报告表

说明:1、论文(设计)类型:A—理论研究;B—应用研究;C—设计等;

2、论文(设计)来源:指来源于科研项目、生产/社会实际、教师选题或其他(学生自拟)等;

3、各项栏目空格不够,可自行扩大。

第二篇:多功能数字钟设计

多功能数字钟设计

一、设计任务:

(一)主体功能

用HDL设计一个多功能数字钟,包含以下主要功能:

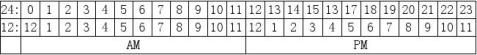

1.计时及校时,时间可以24小时制或12小时制显示

2.日历:显示年月日星期,及设定设定功能

3.跑表:启动/停止/保持显示/清除

4.闹钟:设定闹钟时间,整点提示

(二)输入输出界面

输入:时钟输入,三个按键

输出:8位7段码,2个LED,一个蜂鸣器

三个按键从左到右为:Key3、key2、Key1,功能在不同模式下定义不同: Key3:模式键ModeKey,

Key2:日历显示/设置选择键SetSelKey/启动与停止键StartPause, Key1:闹钟时间显示/设置键SetKey/显示保持键HoldReset

8位7

两个LED分别指示闹钟与整点提示的开关状态。

时钟输入后文再详细描述。

(三)仿真实验条件要求

试验板为EDA Pro2K实验开发系统,仿真芯片用

Altera FLEX10K系列的EPF10K10LC84-4。

由于实验板有限,大部分仿真在计算机上用maxplus

或其它软件完成。当认为运行比较理想时,要按照后文

的管脚定义,分配好管脚,编译成可下载的文件,到实

验室申请做下载试验。要求能够实现主体功能,实验结

果存在的问题,要在报告中分板其原因。

二、详细功能及状态描述:

总体分四种模式,由Key3(ModeKey)切换

(一)时间显示模式:

初始状态为24小时制显示当前时间:小时(8-7)/分(6-5)/秒(4-3),2-1位不显。设置为12小时制时,第1位数码管显示上午/下午,上午显示A(AM),下午显示b(如果自己控制七段码也可以令其显示P)

按Key2显示当前日历:年(8-7)/月(6-5) /日(4-3) /星期(1),第2位不显。释放Key2还原显示;

按Key1显示闹钟所定时间:24小时制下显示:小时(8-7)/分(6-5),4-1位不显。12小时制下第1位数码管显示A/B。

按Key3(ModeKey)进入下一模式:跑表模式

(二)跑表模式

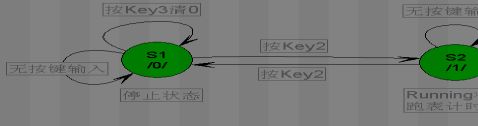

状态机如下图所示:

显示:小时(9-7)分钟(6-5)/秒(4-3)/百分秒(2-1)

按Key3(ModeKey)进入下一模式:校时/校日历

(三)校时模式

按Key2进行调节对像选择

Key2 Key2 Key2 24/12Key2 Key2 Key2 Key2 Key2 秒 小时 ---> 分 ---> ---> 小时---> 年 ---> 月 ---> 日 ---> 星期 --┐ 清0 切换 <-┘ 按Key1一下,所调对像加1(或秒清0),长按Key1一秒钟以上,进入快调模式,所调对像每秒跳变8-10次。设置某一部分时,要断开相关的进位链,如:正在调分时,应忽略秒的进位脉冲,并且满60的进位也不能影响到后面的小时。

按Key3(ModeKey)进入下一模式:闹钟设定

(四)闹钟设定

按Key2进行调节对像选择

Key2 Key2 Key2 Key2

调小时---->调分---->闹钟开关----->整点提示开关----->调小时

调节方式同上。

按Key3(ModeKey)回到时间显示模式。

三、参考模块设计:

1.按键接口模块

功能:1)消除按键的抖动,输出平稳的电平

2)跟据不同模块的需要输出不同宽度的电平。

如:输入到跑表的按键电平宽度应与状态机所用时钟的宽度相同。在设定时间

和闹钟时,长按Key3需要输出快速调节脉冲。

2.分频模块:由输入的时钟得到需要的各种基准频率,详细讨论见设计提示。

3.模式切换模块:通过按键切换当前模式及设置选择。

输入:ModeKey,SetSelKey

输出:当前显示模式Mode,设置对像选择SetSel

注意一点的是:当Mode变化时,SetSel应自动清0。

4.计时/校时模块

根据Mode、SetSel的不同,对各时间部分进行计数及设置

输入:1Hz脉冲,Mode,SetSel,设置脉冲等

输出:秒、分、小时、日、月、年和星期,并且小时需要24/12小时制两种输出

5.设定闹钟模块:

输入:Mode,SetSel,设置脉冲、当前时间等

输出:所定时间,小时也需要24/12小时制两种输出

6.秒表模块:

输入:Mode,StartPauseKey,HoldResetKey

输出:当前计时,Holding状态所保持的时间

7.闹钟控制及波形产生模块

到了设定时间,输出闹铃波形至蜂鸣器

闹铃:1秒四个节拍:嘀-嘀-----(-表示无声,长度1/8秒)声音频率:1kHz左右

整点提示音:四低一高,低音500Hz左右,高音1kHz左右,59分钟最后十秒声音为:—低—低—低—低—高,(—表示无声,长度1秒)

8.显示控制模块

控制不同模式下显示不同的内容,以及调节时闪烁显示。

四、设计提示

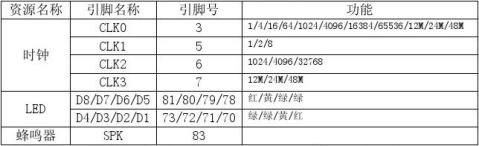

1.关于输入时钟

试验板上可以输入4路时钟,并有多钟频率可以选择(详见后文实验板资源),问题:输入几路时钟?各多少赫兹?如何分频得到所需频率?

提示:选择时钟源的原则是:输入的时钟源尽量少,内部分频器也要尽量少。先查看一下需要哪些时钟。

计时的基准时钟:1Hz

跑表的基准时钟:100Hz

数字闪烁显示:2Hz

闹铃/整点提示音:节拍控制4Hz/1Hz,及声音频率1kHz/500Hz左右

快速调节:每秒8-10次

七段码扫描显示:>=200Hz(每位数字至少25Hz,8位扫描至少要200Hz的扫描频率)

参考一:输入两路时钟源:8Hz和4096Hz

8Hz经分频得到:4Hz,2Hz,1Hz

4096Hz经分频得到音频与数码管的扫描脉冲:1024Hz,512Hz

4096Hz经41分频得到:100Hz(误差小于0.1%)

参考二:输入一路时钟源,由4096Hz分频得到全部所需时钟。

2.关于星期

星期的设定可以有自动和手动两种方案,自动是指根据当前年、月、日自动确定星期几;手动方案是需要自己设定好星期,然后星期与日历同步走。手动设计相对简单一些,自动则需要利用Altera芯片提供的EAB来实现ROM型的查找表。做查找表时要考虑EAB的资源有限,EPF10K10共3个EAB,每个2048字节。

问题:一个EAB能放下几年的星期查找表?如果用一个表查找2000-20xx年的星期,需要多大的查找表?太大怎么办?

提示:可以试试用两个表分步查找。

3.关于24/12小时制

设计中时间与闹钟定时都需要小时在两钟模式下显示,设计不好就会增加很多资源的开销。有三种设计方案:

1)两套计数器分别计24/12小时制的时间。

2)只计数24制小时,用组合逻辑来转换24->12

3)用查找表来转换。注意的是两个地方都要转换,如何同享同一个查找表?

4.关于跑表的状态机设计

问题:这是个什么类型的状态机?如何设计?

提示:所需输出的变量Runing,Holding与状态有关,与输入无关,但需要控制的清0、刷新保持显示的值不仅与状态有关,与输入也有关。但是可以设计三个状态下状态变量S的值分别为:00/01/11(格雷码),则Runing对应S的低位,Holding对应S的高位,这样需要改变的只有清0与刷新保持值的信号,可以当作Merly状态机来设计。

5.关于按键除抖动及固定宽度脉冲输出

按键除抖动的原理是:当检测到一个高电平时,延时一段时间(如10ms)再检测,如果仍是高电平就表明按键确实按下了。释放按键也是同样的检测方法。

固定宽度脉冲生成的原理是:在去除抖动的基础上,判断两个经过不同延时的按键信号,如果前一时钟检测到的是低电平,这一时钟检测到高电平,说明按键按下,输出一个时钟周期宽度的高电平。

6.关于试验板的资源与仿真模式

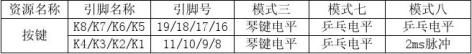

本实验中需要利用到的有时钟源、按键、数码管、LED和蜂鸣器。实验板上可以选择不同的模式来选择不同的输入输出方式,按使用说明书,本实验可选择模式三、

七、八。后两种控制显示效果的能力强一些,做起来也相对复杂。

先介绍一下几种模式下的引脚定义,比较优缺点,并给出相关设计提示。

乒乓电平是指按一次变成高电平,再按一次变成低电平,如此反复

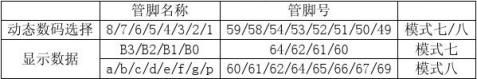

数码管的输出在三钟模式下完全不同:

在模式三,每个数码管有4个引脚作为8421码输入,经内部译码,显示0-F十六进制数;

模式七:8个数码管并联成动态扫描显示器,共12个引脚,其中4个作为公用的显示数值输入端,8个为输出的选择端。也就是说,每一时刻8个选择端只有一个高电平,其余为低电平,输入的数值显示在高电平对应的数码管上。

模式八:也是动态扫描显示,不同的有16个引脚,除8个为输出的选择端外,另八个对应七段码的每一段及小数点。

几种模式相比较,模式三输出最简单,但不能控制数码管的亮与灭。模式七的显示比较实用一些,可以控制亮与灭,但不能点亮数码管的点号,缺少各时间部分的分隔号。模式八功能最强,除了可以点亮点号作为分隔符外,还可以显示非标准的字符,比如可以显示P来指示下午。

虽然模式七、八能控制数码管的亮与灭,但不足之处是按键都没有符合需要的琴键电平,使用起来不太方便。只能选择乒乓电平,每次需要按两次来完成实际需要的一次按键。

各人可以选做其中一种模式,建议使用模式七。各种模式参考设计如下:

模式三:如果想控制某个数码管灭或闪烁,输出F与正常显示的数字相区别。(输出Z是无效的,默认输出是0)

模式七/八:需要三组8位的状态码来控制分别控制扫描输出、亮与灭、闪烁。 扫描码:ScanCode,由8位循环移位计数器还控制,扫描时钟频率>200Hz。 使能位:LEDEnable,为1的位对应用数码管才亮。

闪烁位:Blink,为0的位闪动

三组状态码与闪烁用的2Hz脉冲组合起来控制相应数码管的显示。

三种模式下的数码管管脚定义: