电子科技大学

实 验 报 告

一、实验一:ALU设计实验

二、实验室名称:主楼A2-411 实验学时:4

三、实验目的:

1.熟悉ALU的工作原理。

2.掌握多个ALU的扩展方法。

3.掌握用硬件描述语言设计ALU的方法。

4.掌握数据的暂存和分时传送的方法。

四、实验内容

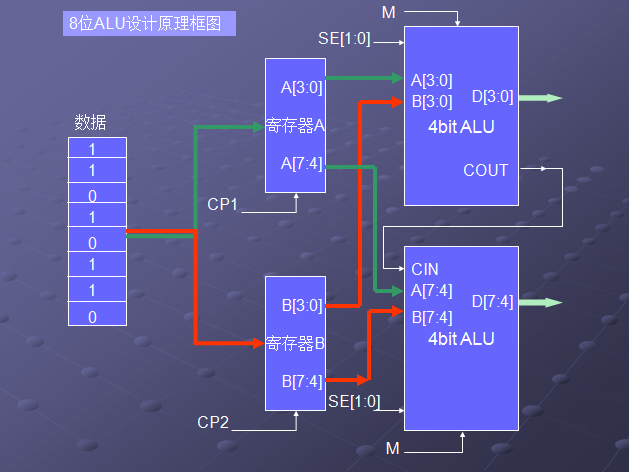

设计一个8bit ALU,实现两个8bit二进制数的算术运算和逻辑运算,

★算术运算(加、减);

★逻辑运算(与、或、置1、清0);

实验要求:

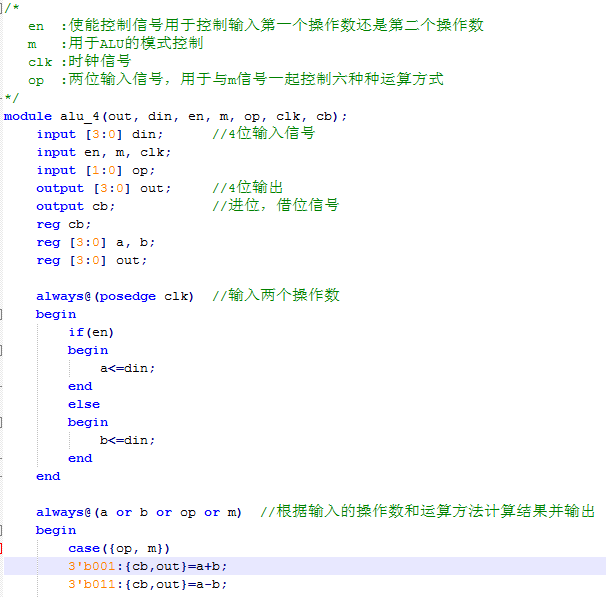

1.设计一个4bitALU模块;

2.如何用4bitALU实现8bitALU的功能?

3.数据的输入/输出

输入: 只有8个开关,如何分时输入数据?

输出: 8个指示灯(数据),1个指示灯(进位/借位)

4.控制端输入

模式控制: (算术 / 逻辑)

运算方式控制: (+、- / and、or 、set、clr)

分时控制位: (输入数据的使能端)

数据输入控制脉冲:

五、实验原理:

verilog硬件描述语言的硬件描述设计仿真功能。

FPGA现场可编程逻辑门阵列的开发原理。

设计图如下:

六、实验器材:

PC机、Xilinx ise7.1 集成开发坏境、pq208

七、实验步骤:

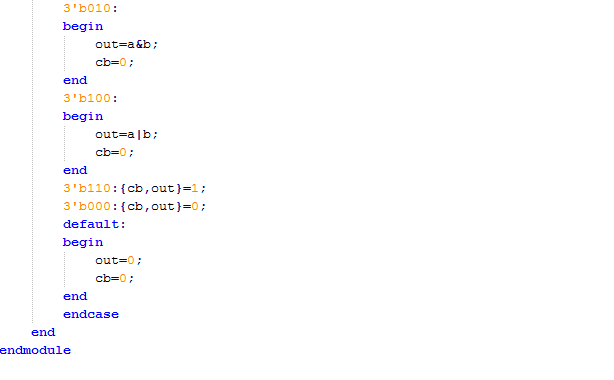

实验代码:

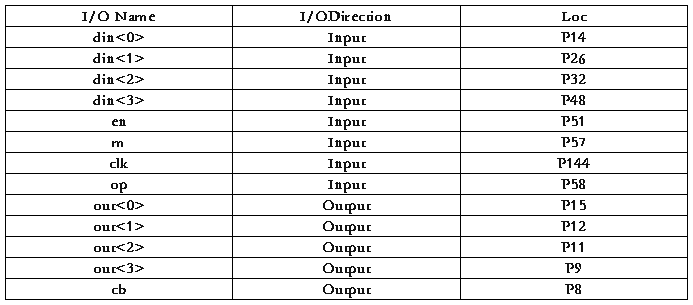

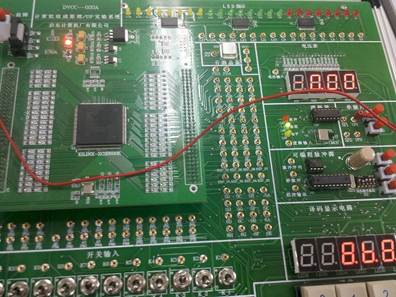

I/O 端口连接,与指示灯连接方式如图:

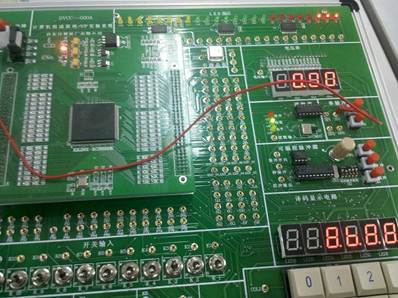

八、实验数据及结果分析:

3|4结果,111,进位0,{op,m}运算控制符为 100

3-4结果,1111(-1),借位1,{op,m}运算控制符为 011

3+4结果,111,进位0,{op,m}运算控制符为001

置1结果,除进位外置1,{op,m}运算控制符为110

清零结果,{op,m}运算控制符为000

如图显示3&4结果,输出全0,{op,m}运算控制符为010

九、总结、改进建议及心得体会:

本次实验完成了一个ALU模块的设计,并在FPGA模块上进行了仿真设计实现验证。完成了在不同使能控制信号下的第一个与第二个操作数的读取,并且在模式控制信号和op操作信号作用下完成对六种运算方式的模拟(模式控制信号控制+ 、-/ and or set reser)。

本次实验将我们在课本上的知识从了解层面向理解层面迈进了一大步,增进了对所学知识的认识,实验收获很大。在此谢谢指导老师的辛勤工作!

电子科技大学

实 验 报 告

一、实验二:存贮器设计实验

二、实验室名称:主楼A2-411 实验学时:4

三、实验目的:

1.掌握存贮器的读写控制方法,(读信号、写信号、片选信号)。

2.掌握存储器的字扩展和位扩展方法。

3.掌握用硬件描述语言设计存贮器的方法。

4.了解存储器种类、工作原理和特点。

四、实验原理:

verilog硬件描述语言的硬件描述设计仿真功能。

FPGA现场可编程逻辑门阵列的开发原理。

存储器位扩展与字扩展的原理。

五、实验内容:

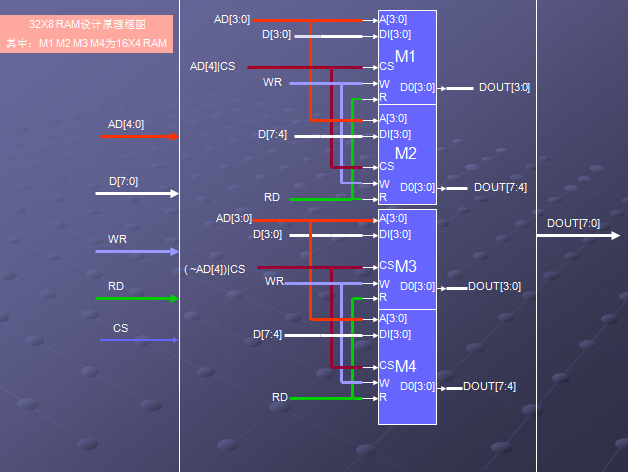

用字扩展和位扩展的方式,设计一个32X8的静态存储器,能够对其随机的读写。其中:32表示地址的寻址空间大小,8表示数据单元的位数。

要求:

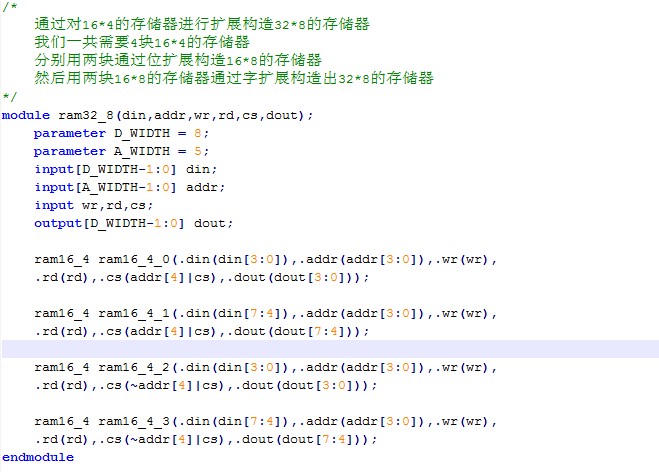

1.设计一个16X4的可随机读写的存储器模块。

2.利用16X4存储器模块,如何通过级连实现32X8的存储器的功能。

3.数据、地址的输入/输出

数据/地址的输入:开关控制。

数据的输出:指示灯显示。

4.控制信号

片选:低有效。

读:低有效。

写:上升沿有效。

实验器材:

PC机、Xilinx ise7.1 集成开发坏境

七、实验步骤:

实验代码:

16*4存储器设计模块

32*8存储器设计模块

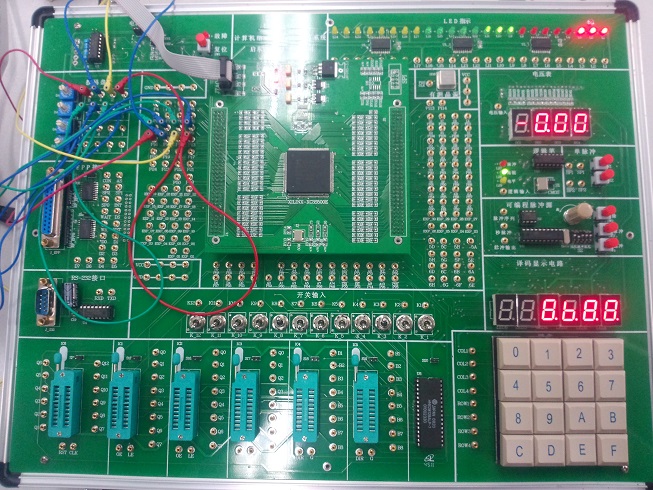

七、实验数据及结果分析:

实现了在写信号上升沿及片选信号低电平时的写入存储器功能

实现了在读信号和片选信号都是低电平时读出存储器数据的功能

八、总结、改进建议及心得体会:

本实验完成了对存储器进行读写,并在给定目标和条件下进行位扩展和字扩展的实践设计以完成目标任务。在布线的时候发现由于输入端口不够使用,我们就可以使用左上角的转盘输入增大输入端口数。我们首先向存储器当中写入一个数值,然后再操作读取改地址信号,测试程序设计正确性。

本次实验将我们在课本上的知识从了解层面向理解层面迈进了一大步,增进了对所学知识的认识,实验收获很大。在此谢谢指导老师的辛勤工作!

第二篇:《计算机组成原理》课程设计

华 北 科 技 学 院

课程设计说明书

设计名称:__ 计算机组成原理课程设计 ___

班 级: 计科B12-1 第_ _7 _组

小组成员:_ ___、_ _ ___、_ __

设计内容:_扩展4条指令MBMC、NOTD、SHTD、SUBN

设计时间:__ 20##-1-12 __至__ 20##-1-23 _

指导教师:_ 席振元、梁生科、顾涛、邵铁君、于咏霞

小组总体情况:

1、工作量: 大( ), 较大( ), 一般( ), 较小( )

2、难易度: 难( ), 较难( ), 一般( ), 简单( )

3、报告规范度: 规范( ), 较规范( ), 一般( ), 不规范( )

评阅教师:__ _ __

课题组成员及分工

成绩评定

小组成员 :

1、工作量: 大( ),较 大( ),一般( ),较 小( )

2、难易度: 难( ),较 难( ),一般( ),简 单( )

3、答辩情况:

基本操作: 熟练( ),较熟练( ),一般( ),不熟练( )

基本原理: 清楚( ),较清楚( ),基本清楚( ),不清楚( )

4、学习态度: 优秀( ),良 好( ),中等( ),一 般( )

总评成绩:_________

小组成员 :

1、工作量: 大( ),较 大( ),一般( ),较 小( )

2、难易度: 难( ),较 难( ),一般( ),简 单( )

3、答辩情况:

基本操作: 熟练( ),较熟练( ),一般( ),不熟练( )

基本原理: 清楚( ),较清楚( ),基本清楚( ),不清楚( )

4、学习态度: 优秀( ),良 好( ),中等( ),一 般( )

总评成绩:_________

小组成员 :

1、工作量: 大( ),较 大( ),一般( ),较 小( )

2、难易度: 难( ),较 难( ),一般( ),简 单( )

3、答辩情况:

基本操作: 熟练( ),较熟练( ),一般( ),不熟练( )

基本原理: 清楚( ),较清楚( ),基本清楚( ),不清楚( )

4、学习态度: 优秀( ),良 好( ),中等( ),一 般( )

总评成绩:_________

1.课程设计目的

通过计算机组成原理课程设计,进一步熟练掌握计算机各功能部件的内部构造和相互之间的联系(部件配置、相互连接和作用)、各功能部件的性能参数的相互匹配、机器指令级的各种功能和特性。进一步将所学知识融会贯通、达到知识的系统化,进一步提高硬件系统设计的能力,为以后的更高一级的硬件设计打下坚实基础。

2.课程设计任务

在现有的TEC-XP+教学机指令系统上扩展4条指令。

要求:(1)4条指令至少要用到4种寻址方式;

(2)4条指令分别由1步、2步、3步、4步完成;

(3)监控命令A、U必须能够支持这4条指令。

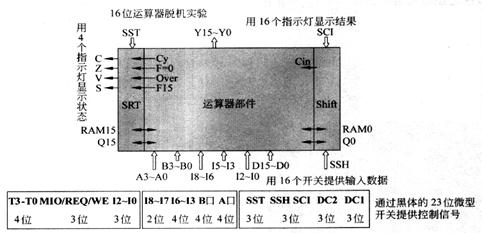

3.系统组成原理及实现

对用到的原理进行简要说明。

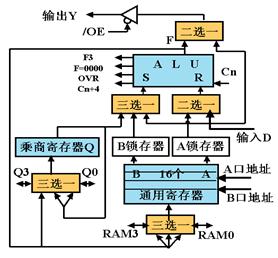

(1)运算器

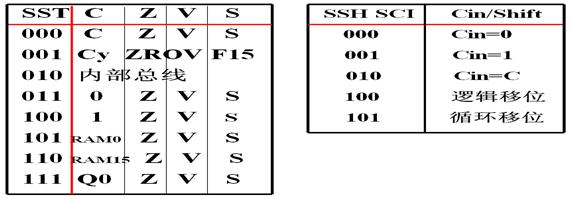

TEC-XP系统机上的运算器,选 8 或 16 位字长,分别由 2 或 4 片 4 位的位片结构的器件组成,作为讲解运算器的实例和教学实验的对象,有很强的典型性。运算器部件主要包括两组独立的8位字长的运算器,各自由2片位片结构的运算器AM2901组成;还有状态标志(CZVS)寄存器和教学实验所需的相关逻辑部件。AM2901的结构如下图所示:

4位运算器芯片Am2901内部结构框图

第一个组成部分是算逻运算部件ALU,完成 3 种算术运算 和 5 种逻辑运算,共计 8 种功能。其输出为 F,两路输入为 S、R,最低位进位Cn,四个状态输出信号如图所示。

第二个组成部分是通用寄存器组,由16个寄存器构成,并通过B口与A口地址选择被读的寄存器,B口地址还用于指定写入寄存器。通过B口地址、A口地址读出的数据将送到B、A锁存器,要写入寄存器的数据由一个多路选择器送来。

第三个组成部分是乘商寄存器Q,它能对自己的内容完成左右移位功能,其输出可以送往ALU,并可接收ALU的输出结果。一组三选一门和另一组二选一门用来选择送向ALU的 R、S输入端的数据来源,包括Q寄存器、A口、 B口、外部输入D数据的8 种不同组合。

第四个组成部分是 5 组多路选通门,包括一组三选一门完成把ALU的输出、或左移一位、或右移一位的值送往通用寄存器组,最高、最低位移位信号有双向入/出问题。一组三选一门完成Q寄存器的左移一位、或右移一位、或接收ALU输出值的功能,最高、最低位移位信号有双向入/出问题。

一组二选一门,选择把A口数据或ALU结果送出芯片,以给出输出Y的数据,Y输出的有无还受输出使能 /OE信号的控制,仅当 /OE为低时才有Y输出 ,/OE为高,Y输出为高阻态。

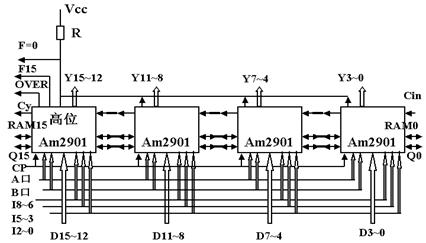

TEC-XP计原l 6系统的运算器部件主体部分由4片长度为4位的位片结构运算器芯片Am2901组成。4 片Am2901之间的连接如图所示。

4片Am2901连接图

16位运算器结构框图

(2)微程序控制器

微程序控制器的组成与实现,以及微指令格式及各字段意义。

入口地址:指令的微程序入口地址;

下址:微程序执行完后下一条微程序的地址;00表示需要进行地址转移逻辑,30表示微程序结束。

CI3-0:判别测试字段,其主要编码及功能如表1。

SCC3-0:地址转移逻辑字符,仅当CI3-0为0011时有效。其主要编码及功能如表2。

MRW:控制对内存和I/O接口的读写,其主要功能如下:

000,写内存;001读内存;010写串口;011读串口;1XX无内存和串口的读写操作。

I2-0:控制数据来源,其编码及功能见表3。

I8-6:控制对运算结果的处理,其编码及功能见表3。

I5-3:运算功能的选择,其编码及功能见表3。

表3 Am2901的9位控制码编码及功能

SST:对CZVS的控制。

SSHSCI:设置进位输入。

B口:1000表示IR的DR字段,0000表示不用B口。

A口:1000表示IR的SR字段,0000表示不用A口。

(3)内部总线和特定寄存器的控制

DC2:专用寄存器接收控制,其主要编码及功能见表4-1。

DC1:送内部总线的数据,其主要编码及功能见表4-2。

4.扩展4条指令

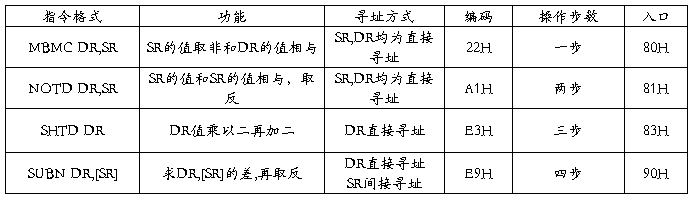

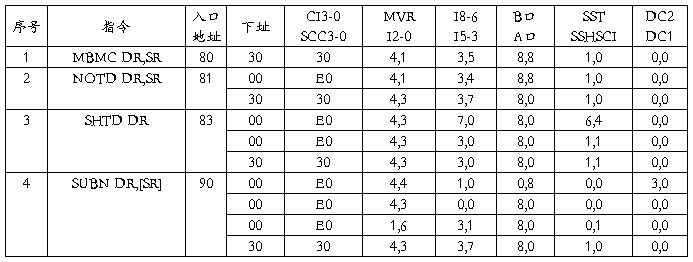

(1)4条指令的格式及功能

4条扩展指令的格式、功能、寻址方式、操作码编码、微程序步数、微程序入口地址如下表。

(2)指令所对应的微程序

每条机器指令对应的微程序、每条微指令的功能及各字段值的意义如下表:

(3)ABEL语言源程序编辑以及JED文件生成

MBMC = (IR==[0,0,1,0,0,0,1,0]);

NOTD = (IR==[1,0,1,0,0,0,0,1]);

SHTD = (IR==[1,1,1,0,0,0,1,1]);

SUBN = (IR==[1,1,1,0,1,0,0,1]);

MA80 = (Y==[1,0,0,0,0,0,0,0]);

MA81 = (Y==[1,0,0,0,0,0,0,1]);

MA82 = (Y==[1,0,0,0,0,0,1,0]);

MA83 = (Y==[1,0,0,0,0,0,1,1]);

MA84 = (Y==[1,0,0,0,0,1,0,0]);

MA85 = (Y==[1,0,0,0,0,1,0,1]);

MA90 = (Y==[1,0,0,1,0,0,0,0]);

MA91 = (Y==[1,0,0,1,0,0,0,1]);

MA92 = (Y==[1,0,0,1,0,0,1,0]);

MA93 = (Y==[1,0,0,1,0,0,1,1]);

//入口地址:

D0=!C_M&(!_MAP&(NOTD#SHTD#SUB#OR#CMP#MVRR#DEC#SHR#JR#PSHF#PUSH#POP#POPF#STRR#LDRR#LDPC#MVRD#CALA#RET#IRET#DI#ASR#RCR#STC#LDRA#LDRX#STRA#STRX#SBB#JRS#JRNS)#NXTADDR0&!_PL)&!Bit8;

D1=!C_M&(!_MAP&(SHTD#AND#OR#TEST#MVRR#SHL#SHR#IN_#OUT#POP#POPF#LDRR#LDPC#JMPA#CALA#RET#IRET#NOT#ASR#CLC#STC#JMPR#LDRA#STRA)#NXTADDR1&!_PL)&!Bit8;

D2=!C_M&(!_MAP&(ADD#SUB#AND#OR#INC#DEC#SHL#SHR#PSHF#PUSH#POP#POPF#MVRD#JMPA#CALA#IRET#RCL#RCR#CLC#STC#LDRX#STRA#CALR)#NXTADDR2&!_PL)&!Bit8

D3=!C_M&(!_MAP&(XOR_#CMP#TEST#MVRR#INC#DEC#SHR#SHL#STRR#LDRR#LDPC#MVRD#JMPA#CALA#EI#DI#JMPR#JRS#JRNS#LDRA#LDRX#STRA)#NXTADDR3&!_PL)&!Bit8;D4= !C_M&(!_MAP&(SUBN#JRC#JRNC#JRZ#JRNZ#JR#IN_#OUT#PSHF#PUSH#POP#POPF#STRR#LDRR#LDPC#MVRD#JMPA#CALA#EI#DI#ADC#SBB#NOT#ASR#RCL#RCR#CLC#STC#JMPR#LDRA#LDRX#STRA)#NXTADDR4&!_PL)&!Bit8;

D5=!C_M&(!_MAP&(RET#IRET#JRS#JRNS#CALR#STRX)#NXTADDR5&!_PL)&!Bit8;

D6=!C_M&(!_MAP&(EI#DI#IRET#ADC#SBB#NOT#ASR#RCL#RCR#CLC#STC#JMPR#JRS#JRNS#LDRA#LDRX#STRA#STRX#CALR) #NXTADDR6&!_PL)&!Bit8;

D7=!C_M&(!_MAP&(MBMC#NOTD#SHTD#SUBN)#NXTADDR7&!_PL)&!Bit8;

//下址:

NXTADDR7:= 0;

NXTADDR6:= 0;

NXTADDR5:=!C_M&(MA80#MA82#MA85#MA93#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA10#MA11#MA13#MA14#MA16#MA18#MA1A #MA1C#MA1E#MA22#MA24#MA30#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA56#MA57#MA58#MA59#MA5A#MA63#MA66#MA68#MA69#MA6A)&!Bit8;

NXTADDR4:=!C_M&(MA80#MA82#MA85#MA93#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA10#MA11#MA12#MA13#MA14#MA15#MA16#MA17 #MA18#MA1A#MA1C#MA1D#MA22#MA24#MA30#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA56#MA57#MA58#MA59#MA5A#MA5C#MA5E#MA60#MA63#MA66#MA69#MA6A)&!Bit8;

NXTADDR3:= !C_M&(MA15#MA17#MA1D#MA30#MA5C#MA5E#MA60)&!Bit8;

NXTADDR2:= !C_M&(MA12#MA17#MA1D#MA1E#MA5C#MA5E)&!Bit8;

NXTADDR1:= !C_M&(MA15#MA30#MA31#MA60#MA68)&!Bit8;

NXTADDR0:= !C_M&(MA3F#MA68)&!Bit8;

//CI3-0,SCC3-0定义:

CI3:=!C_M&(MA81#MA83#MA84#MA90#MA91#MA92#MA00#MA01#MA02#MA19#MA1B#MA89#MA1F#MA20#MA21#MA23#MA3A#MA3B#MA3C#MA3D#MA3E#MA5B#MA5D#MA5F#MA61#MA62#MA64#MA65#MA67#MA89)&NRST&!Bit8;

CI2:=!C_M&(MA81#MA83#MA84#MA90#MA91#MA92#MA00#MA01#MA02#MA19#MA1B#MA89#MA1F#MA20#MA21#MA23#MA3A#MA3B#MA3C#MA3D#MA3E#MA5B#MA5D#MA5F#MA61#MA62#MA64#MA65#MA67)&NRST&!Bit8;

CI1:=!C_M&1&NRST&!Bit8;

CI0:=!C_M&(MA80#MA82#MA85#MA93#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA10#MA11#MA12#MA13#MA14#MA15#MA16#MA17#MA18#MA1A#MA1C#MA1D#MA1E#MA22#MA24#MA30#MA31#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA56#MA57#MA58#MA59#MA5A#MA5C#MA5E#MA60#MA63#MA66#MA68#MA69#MA6A)&NRST&!Bit8;

SCC3:= !C_M&0&NRST&!Bit8;

SCC2:= !C_M&(MA10#MA12#MA15#MA17#MA69)&NRST&!Bit8;

SCC1:= !C_M&(MA12#MA15#MA17#MA30)&NRST&!Bit8;

SCC0:= !C_M&(MA15#MA17#MA69)&NRST&!Bit8;

//MVR,I2-I0定义:

!_MIO00:=!(MA80#MA81#MA82#MA83#MA84#MA85#MA90#MA91#MA93#MA00#MA01#MA03#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA10#MA11#MA12#MA15#MA17#MA19#MA1B#MA89#MA1D#MA1E#MA1F#MA21#MA23#MA30#MA31#MA3A#MA3B#MA3D#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA56#MA57#MA58#MA59#MA5A#MA5B#MA5D#MA5F#MA61#MA64#MA66#MA67#MA69#MA6A);

REQ00 := (MA13#MA14);

_WE00:=(MA92#MA02#MA14#MA18#MA1C#MA20#MA24#MA5C#MA5E#MA60#MA62#MA68);

I200:=(MA90#MA92#MA0B#MA11#MA12#MA14#MA1A#MA1B#MA89#MA1C#MA20#MA24#MA30#MA3C#MA3F#MA5A#MA5C#MA5E#MA60#MA62#MA65#MA66#MA6A);

I100:=(MA82#MA83#MA84#MA85#MA91#MA92#MA93#MA01#MA0C#MA0D#MA0E#MA0F#MA12#MA13#MA14#MA15#MA17#MA19#MA1C#MA1D#MA1E#MA1F#MA20#MA21#MA22#MA23#MA24#MA30#MA31#MA3B#MA3D#MA3E#MA3F#MA52#MA53#MA54#MA55#MA5B#MA5C#MA5D#MA5F#MA60#MA61#MA63#MA64#MA67);

!I000:=!(MA80#MA81#MA82#MA83#MA84#MA85#MA91#MA93#MA00#MA01#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0C#MA0D#MA0E#MA0F#MA11#MA12#MA13#MA14#MA15#MA17#MA19#MA1C#MA1D#MA1E#MA1F#MA20#MA21#MA23#MA24#MA30#MA31#MA3B#MA3D#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA5B#MA5C#MA5D#MA5E#MA5F#MA60#MA61#MA62#MA63#MA64#MA67#MA6A)

//I8-I6,I5-3定义:

I800:= (MA83#MA0E#MA0F#MA53#MA54#MA55);

I700:=(MA80#MA81#MA82#MA83#MA84#MA85#MA92#MA93#MA00#MA01#MA04#MA05#MA06#MA07#MA08#MA0B#MA0C#MA0D#MA0E#MA11#MA14#MA15#MA17#MA1C#MA1D#MA1E#MA1F#MA21#MA22#MA23#MA24#MA31#MA3B#MA3D#MA3F#MA50#MA51#MA52#MA54#MA5A#MA5B#MA5D#MA5F#MA61#MA64#MA66#MA67#MA6A);

!I600:=!(MA80#MA81#MA82#MA83#MA84#MA85#MA90#MA92#MA93#MA00#MA02#MA03#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA10#MA11#MA12#MA13#MA14#MA15#MA16#MA18#MA19#MA1A#MA1B#MA89#MA1C#MA21#MA24#MA3A#MA3B#MA3C#MA3D#MA3E#MA3F#MA50#MA51#MA52#MA53#MA54#MA55#MA56#MA57#MA58#MA59#MA5A#MA5C#MA5E#MA60#MA62#MA63#MA64#MA65#MA66#MA68#MA69#MA6A)

I500:=(MA80#MA81#MA82#MA93#MA06#MA08#MA0A#MA52);

I400:=(MA82#MA93#MA07#MA08#MA52);

I300:=(MA80#MA82#MA92#MA93#MA00#MA05#MA07#MA09#MA0D#MA15#MA21#MA3B#MA3D#MA51#MA52#MA64);

//B口,A口定义:

B30=(MA80#MA81#MA82#MA83#MA84#MA85#MA91#MA92#MA93#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA0C#MA0D#MA0E#MA0F#MA19#MA1C#MA50#MA51#MA52#MA53#MA54#MA55#MA63);

B300 :=B30&IR7;

B20=(MA00#MA01#MA11#MA15#MA17#MA1D#MA1E#MA1F#MA21#MA22#MA23#MA24#MA31#MA3B#MA3D#MA3F#MA5A#MA5B#MA5D#MA5F#MA61#MA64#MA66#MA67#MA6A);

B200 :=(!B30&B20 # B30&IR6);

B10 = 0;

B100 :=(!B30&B10 # B30&IR5);

B00=(MA00#MA01#MA11#MA1D#MA1E#MA1F#MA22#MA24#MA31#MA3F#MA5A#MA5B#MA5D#MA5F#MA61#MA66#MA6A);

B000 :=(!B30&B00 # B30&IR4);

A30=(MA80#MA81#MA90#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0B#MA1A#MA1B#MA89#MA50#MA51#MA5A#MA5E#MA62#MA66);

A300 :=(A30&IR3);

A20=(MA00#MA01#MA11#MA17#MA1D#MA1E#MA1F#MA22#MA23#MA31#MA3C#MA5B#MA5D#MA5F#MA61#MA65#MA67#MA6A);

A200 :=(!A30&A20 # A30&IR2);

A10 = 0;

A100 :=(!A30&A10 # A30&IR1);

A00=(MA00#MA01#MA11#MA1D#MA1E#MA1F#MA22#MA31#MA3C#MA5B#MA5D#MA5F#MA61#MA65#MA6A);

A000 :=(!A30&A00 # A30&IR0);

//SST ,SSHSCI定义:

SST200:=(MA83#MA0E#MA0F#MA53#MA54#MA55#MA57);

SST100:=(MA83#MA0E#MA18#MA54#MA56#MA68);

SST000:=(MA80#MA81#MA82#MA84#MA85#MA93#MA04#MA05#MA06#MA07#MA08#MA09#MA0A#MA0C#MA0D#MA0F#MA50#MA51#MA52#MA53#MA55#MA56);

SSH00 :=(MA83#MA53#MA54#MA55);

SCI100:=(MA50#MA51#MA53);

SCI000:=(MA84#MA85#MA92#MA00#MA01#MA05#MA09#MA0C#MA17#MA1D#MA1E#MA1F#MA23#MA31#MA53#MA54#MA55#MA5B#MA5D#MA5F#MA61#MA67);

//DC2,DC1定义:

DC2_200:=(MA00#MA3A#MA3C#MA58#MA59#MA68);

DC2_100:=(MA90#MA00#MA01#MA12#MA15#MA17#MA19#MA1B#MA89#MA1D#MA1E#MA1F#MA21#MA23#MA31#MA3A#MA3B#MA3D#MA58#MA59#MA5B#MA5C#MA5D#MA5E#MA5F#MA60#MA61#MA62#MA64#MA67);

DC2_000:=(MA90#MA00#MA01#MA02#MA12#MA15#MA17#MA19#MA1B#MA89#MA1D#MA1E#MA1F#MA21#MA23#MA31#MA3A#MA3B#MA3C#MA3D#MA59#MA5B#MA5C#MA5D#MA5E#MA5F#MA60#MA61#MA62#MA64#MA67);

DC1_200:= (MA01#MA31#MA3F); //(MA3F);//

DC1_100:=(MA01#MA11#MA12#MA16#MA30#MA31#MA6A);//(MA11#MA12#MA16#MA30#MA6A); //

DC1_000:= (MA13#MA16#MA1A#MA22#MA30#MA3C#MA3E#MA3F#MA63#MA65);

(3)MACH编程

将JED文件下载到MACH器件的过程

(1)双击lc4256.syn,启动ispLEVER

(2)双击.abl文件

(3)双击Compile Logic进行编译

(4)双击JEDEC File,生成.jed文件

(5)双击启动ispVM System

(6) SCAN找到器件并双击

(7) Browse找到.jed文件,OK

(8) GO

(4)修改监控制程序

;1 WORD 1 - Follow None

TYPE1 DW 'PSHF', 8400H, 'POPF', 8C00H, 'RET ', 8F00H

DW 'CLC ', 6C00H, 'STC ', 6D00H, 'EI ', 6E00H,'DI ', 6F00H

DW 'IRET', 0EF00H, 0

;1 WORD 2 - Follow By A Register(SR)

TYPE2 DW 'PUSH', 8500H,'JMPR', 6000H,'CALR', 0E000H,'SHTD', 0E300H, 0 ;1 WORD;3 - Follow By Two Registers

TYPE3 DW 'ADD ', 0000H, 'SUB ', 0100H

DW 'CMP ', 0300H, 'AND ', 0200H, 'OR ', 0600H,'XOR ', 0400H

DW 'TEST', 0500H, 'MVRR', 0700H

DW 'ADC ', 2000H, 'SBB ', 2100H, 'MBMC', 2200H,'NOTD',0A100H

DW 'ADDR', 0B200H, 'SBUL',0B300H,0

; 1 WORD - Follow By An Offset

TYPE4 DW 'JR ', 4100H, 'JRZ ', 4600H, 'JRNZ', 4700H, 'JRC ', 4400H

DW 'JRNC', 4500H, 'JRS ', 6400H,'JRNS', 6500H,0

; 2 WORD 5 - Follow By Any Address

TYPE5 DW 'JMPA', 8000H, 'CALA', 0CE00H, 0

; 1 WORD 6 - Follow By A Port <= FFH

TYPE6 DW 'IN ', 8200H, 'OUT ', 8600H, 0

; 2 WORD 7 - Follow By A Register And A Adress

TYPE7 DW 'MVRD', 8800H, 0

; 1 WORD 8 - Follow By A [R] and R

TYPE8 DW 'STRR', 8300H, 0

; 1 WORD 9 - Follow By A R and [R]

TYPE9 DW 'LDRR', 8100H

DW 'ADRM', 0E300H, 'SUBN', 0E900H, 0

; 1 WORD 10 - Follow By A Register(DR)

TYPE10 DW 'POP ', 8700H, 'INC ', 0900H, 'DEC ', 0800H, 'JCFX ', 0C000H

DW 'SHL ', 0A00H, 'SHR ', 0B00H

DW 'NOT ', 2D00H, 'ASR ', 2C00H, 'RCL ', 2A00H

DW 'ACR ', 2B00H

DW 'SHLD', 0B000H, 'DECL',0B500H,'NEG ',0B400H

DW 'INHL',0B100H, 0

监控程序修改完后焼入芯片。

5.对扩展指令进行验证

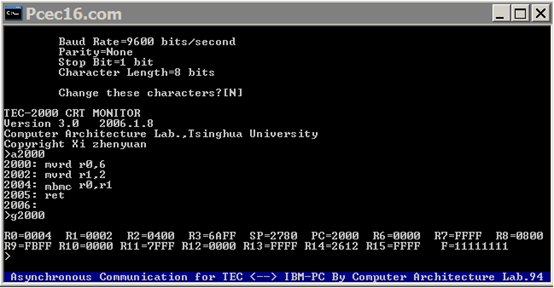

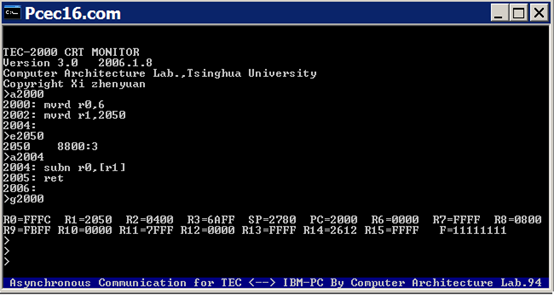

(1)验证指令MBMC DR,SR [/SR∧DR -> DR]

A 2000

MVRD R0,6

MVRD R1,2

MBMC R0,R1

RET

G 20## 执行指令(运行结果图如下图)

G 20## 执行指令(运行结果图如下图)

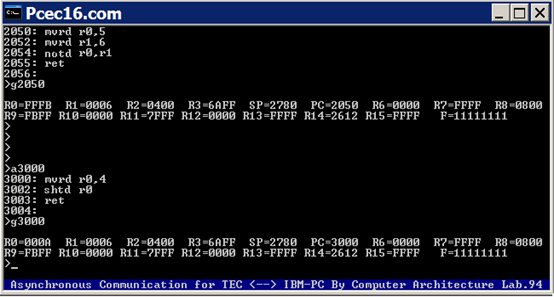

(2)验证指令NOTD DR,SR [/(DR∧SR)-> DR]

A 2050

MVRD R0,5

MVRD R1,6

NOTD R0,R1

RET

G 2050执行指令(运行结果图如下图)

(3)验证指令SHTD DR [(DR*2+1+1)-> DR]

A 3000

MVRD R0,4

SHTD R0

RET

G 3000执行指令(运行结果图如下图)

(4)验证指令 SUBN DR,[SR] [/(DR-[SR])-> DR]

A 2000

MVRD R0,6

MVRD R1,2050

E2050

2050 0002:3

A 2004

SUBN R0,[R1]

RET

G 2000执行指令(运行结果图如下图)

G 2000执行指令(运行结果图如下图)

6.总结与体会

经过两个星期的学习与实践,我和小组同学终于成功完成此次课程设计,扩展出了四条汇编指令,并能够在机器上顺利运行。总结两周学习的内容如下: 首先我们开始准备动手做实验前的预备知识,磨刀不误砍柴功嘛,实验前必须理解的内容是很多的。第一步是复习并深入了解了指令的相关内容,TEC-2000 教学机的指令格式、寻址方式并编写了一些汇编小程序增加对教学机各种指令的理解,另外对于指令的执行过程也有了进一步的理解,并熟悉了微指令的流程。 然后熟悉了微程序控制器的原理和执行过程,尤其是各个芯片和对应的控制信号该如何选择器功能是什么,只有理解了这些才能正确编出指令,否则会遇到重重困难。最后监控程序的10中类型也要了解才能清楚自己编写的指令属于哪种类型,才能正确的修改监控程序。

其次就是动手作业了。在这里要修改监控程序和修改ABEL语言程序,我们要对芯片进行写入,虽然有些繁琐,但正好锻炼了我的耐心和细心。这个过程中也遇到了不少困难,由于硬件的东西容易损坏,特别是芯片,很容易写坏或者插拆时管脚损坏,这样所有的工作就得重新来过,虽然很麻烦但是我们还是重新做了好几次,保持耐性这也是实验教给我们的,最终我们还是成功的写好了芯片,指令也验证正确。

总的来说在动手实践的过程中我们不仅对组成原理这门课程和TEC-2000教学机有了巩固和体会,学到了更多课堂和书本上没有的知识,更重要的是,我们得到了锻炼,磨练了意志力和耐心,细致和严谨,还有培养了团队精神,有了小组人的共同努力才能够顺利地完成了实验,另外还要感谢指导老师们对我们遇到的问题的积极解答。这次课设中学到的一切我相信以后也会对我有用的。