大 学

高级可编程逻辑实验报告

实验课程名称 :串口通信

实验指导老师 :

学 生 姓 名 :(s100103008)

(s100101095)

(s100131047)

20##年12月20日

串口通信

一、实验目的

1、熟练掌握QuartusII的使用

2、学习多层次的设计方法,掌握基本的Verilog语言

3、进一步熟悉和掌握高级可编程逻辑器件FPGA

4、用所学知识制作简单的硬件

5、通过实验箱实现PC机与试验箱的单向通信。

二、实验设计思路

本试验通过在高级可编程逻辑实验课上所学的QuartusII工具,使用Verilog编程,在将程序下载到试验箱中。设计的要求是基于FPGA的LCD显示屏控制系统,系统由一片FPGA芯片、LCD显示及接口驱动电路模块组成。采用Altera公司的EP3C10E144C8 FPGA芯片。PC上位机与FPGA核心板采用RS232串口通信和JTAG下载线。FPGA核心板的输出通过显示驱动模块点亮LCD显示屏。串口通信电路模块采用MAX232芯片实现电平转换及数据的通信。

三、实验原理

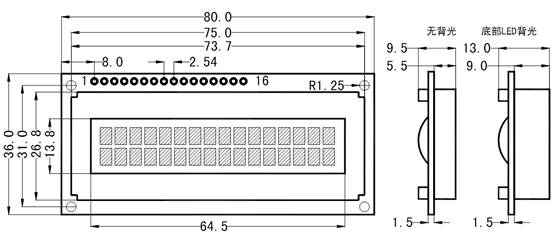

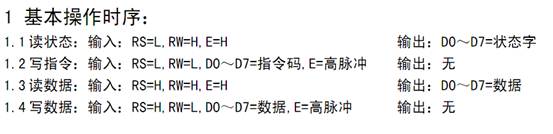

1、关于1602LCD屏的相关信息

2、串行通信的原理

根据同步方式的不同,串行通信又分为两类,异步通信和同步通信。同步通信时除了需要发送数据线,接收数据线和信号地线以外,还需要一根时钟信号线,时钟信号用于同步数据的发送和接收,传送时是先读取同步位,两设备的同步模式一样时数据开始传送,直到送完数据块,发送大的数据块时要周期性的重发同步字符。同步通信主要是应用于高速数据传送场合。异步通信,数据或字符是一帧一帧地传送,帧定义为一个字符完整的通信格式,也称为帧格式。它用占用一位的起始位表示字符的开始,其后是5到8位数据,规定低位在前,高位在后;再是奇偶校验位,通过对数据奇偶性的检查,用于判别字符传输的正确性,可选择三种方式即奇校验、偶校验和无校验;最后用停止位表示字符的结束,可以是1位、1.5位或2位。从起始位开始到停止位结束构成完整的一帧,由于异步通信每传送一帧都有固定的格式,通信双方只要按约定的帧格式来发送和接受数据,所以硬件结构比同步通信方式简单。此外,它还能利用校验位检测错误,所以这种通信方式应用较为广泛。在单片机中主要采用异步通信方式。串行通信的数据传送速率可以用波特率表示,其意义是每秒传送多少位二进制数。

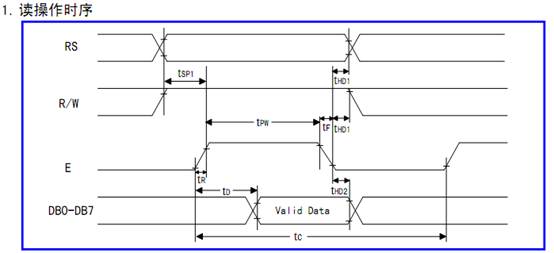

串行通信时,要求通讯双方都采用一个物理接口标准,使不同厂家生产的各种设备可以方便地连接起来进行通讯,目前应用最为广泛的有RS-232和RS-485两种。RS-232是美国电子工业协会EIA(Electronic Industry Association)制定的一种串行物理接口标准,是数据终端设备(DTE)和数据通信设备(DCE)之间的接口标准。该标准规定采用一个9引脚的DB-9接口,对接口的每个引脚的信号内容加以规定,还对各种信号的电平加以规定。在日常应用中,一般使用的只有1到4个引脚,RS-232标准 9个引脚DB-9的引脚定义如下图所示。

DB-9引脚定义图

四、软件设计

1、软件设计的思想

在实现通过串口改变LCD液晶显示的字符的功能,在这里我们用分模块的思想来实现其功能,首先创建RS232接收模块,接着创建一个LCD的显示模块,在液晶显示模块中调用RS232接收模块实时的显示从串口接收过来的数据。

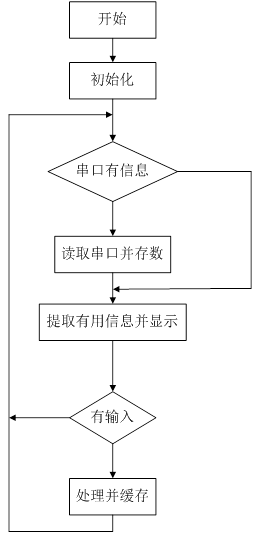

2、设计流程图

五、硬件设计

1、设计所需要的硬件资源

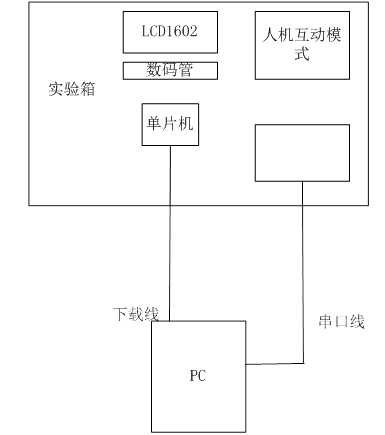

硬件电路总体的设计:硬件电路设计,要结合试验箱上的硬件连接,从而对应连接才可以设计电路。首先确定使用FPGA的哪个I/O口,硬件设计在实验箱上已经固化的,我们只需要根据硬件的连接相应的改变软件的设计即可。其中串口电平转换单元由于实验箱上没有MAX232芯片,故需要设计一个电平转换电路,在实验箱上留有40个扩展接口,可以增加扩展模块,在这里就是利用扩展的接口来实现串行数据的接收。

2、硬件连接框图

3、串口电平转换电路

MAX232的引脚T1IN, T2IN, R1OUT, R2OUT为接TTL/CMOS电平的引脚,引脚T1OUT, T2OUT, R1IN, R2IN为接RS-232电平的引脚。

六、实验步骤

1、先建一个工程,将附录三中程序放在该工程下,再调试该程序;

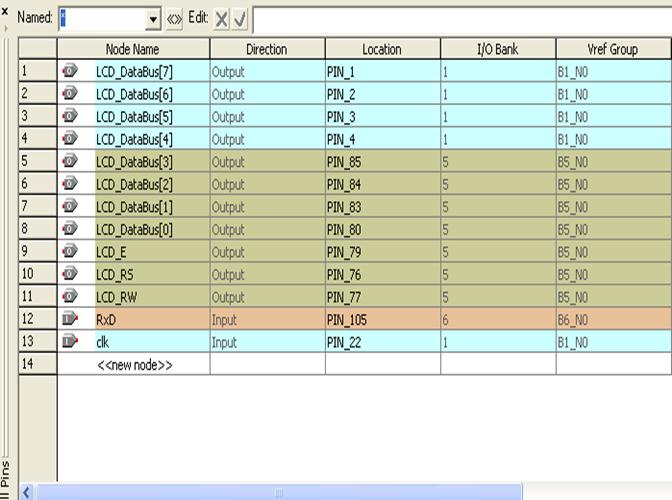

2、编译成功后进行引脚设置,之后再进行全程编译;

3、将程序下载到实验箱中,运行串口调试程序;

4、验证实验结果是否正确。

七、实验结果

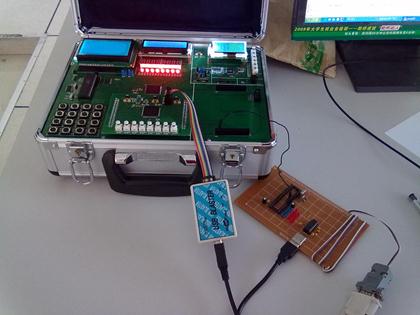

1、实验连接的实物图

2、测试是否有信号输入

3、初始化

4、实现输入显示

八、心得体会

通过本学期实验课的学习,我们获得了不少的知识,为我们后续的研究生学习生活指引了方向。回顾这学期,我从对QuartusII不了解到进一步掌握QuartusII的使用全过程,并进一步懂得了多层次的设计方法,掌握了基本的Verilog语言的设计方法。在这次串口通信实验中,从开始选题到最后完成,期间遇到了好多问题。首先,在选题的过程中,由于对试验箱上芯片所能实现的功能的不了解,以及对实验难度的要求,所以一直没办法定下来。最后通过组员们的商量,以及向学长学姐们的咨询,最终把题目定为了:串口通信。然后是在定题后的资料收集过程中,由于我们对串口通信也不是很熟悉,所以需要对串口通信进行全新的学习。虽然网上资料很多,不过还是都必须要自己能够看得熟悉,理解了之后才能自己拿来用。最后就是在程序的调试阶段,由于对软件的不熟悉,这个也花了很长的时间来弄。不过最终还是得出了满意的结果。由于自身实力的问题,没能实现实验箱到PC机这个方向上的通信,只能简单的通过PC机上的串口调试助手对LCD上的显示做出修改。这个就是本实验需要改进的地方。通过这次实验设计,让我进一步熟悉和掌握了Verilog语言。除了课本上的知识之外,在人际交流沟通协作方面也有一定的提升,增强了团队协作能力。然后感谢在这次实验设计中提供过帮助的老师、学长学姐以及同学们!

附录一

引脚配置

附录二

程序一 串口接收模块

module async_receiver(clk, RxD, RxD_data_ready, RxD_data, RxD_endofpacket, RxD_idle);

input clk, RxD;

output RxD_data_ready; // onc clock pulse when RxD_data is valid

output [7:0] RxD_data;

parameter ClkFrequency = 40000000;

parameter Baud = 9600;

// We also detect if a gap occurs in the received stream of characters

// That can be useful if multiple characters are sent in burst

// so that multiple characters can be treated as a "packet"

output RxD_endofpacket; // one clock pulse, when no more data is received (RxD_idle is going high)

output RxD_idle; // no data is being received

// Baud generator (we use 8 times oversampling)

parameter Baud8 = Baud*8;

parameter Baud8GeneratorAccWidth = 16;

wire [Baud8GeneratorAccWidth:0] Baud8GeneratorInc = ((Baud8<<(Baud8GeneratorAccWidth-7))+(ClkFrequency>>8))/(ClkFrequency>>7);

reg [Baud8GeneratorAccWidth:0] Baud8GeneratorAcc;

always @(posedge clk) Baud8GeneratorAcc <= Baud8GeneratorAcc[Baud8GeneratorAccWidth-1:0] + Baud8GeneratorInc;

wire Baud8Tick = Baud8GeneratorAcc[Baud8GeneratorAccWidth];

////////////////////////////

reg [1:0] RxD_sync_inv;

always @(posedge clk) if(Baud8Tick) RxD_sync_inv <= {RxD_sync_inv[0], ~RxD};

// we invert RxD, so that the idle becomes "0", to prevent a phantom character to be received at startup

reg [1:0] RxD_cnt_inv;

reg RxD_bit_inv;

always @(posedge clk)

if(Baud8Tick)

begin

if( RxD_sync_inv[1] && RxD_cnt_inv!=2'b11) RxD_cnt_inv <= RxD_cnt_inv + 2'h1;

else if(~RxD_sync_inv[1] && RxD_cnt_inv!=2'b00) RxD_cnt_inv <= RxD_cnt_inv - 2'h1;

if(RxD_cnt_inv==2'b00) RxD_bit_inv <= 1'b0;

else

if(RxD_cnt_inv==2'b11) RxD_bit_inv <= 1'b1;

end

reg [3:0] state;

reg [3:0] bit_spacing;

// "next_bit" controls when the data sampling occurs

// depending on how noisy the RxD is, different values might work better

// with a clean connection, values from 8 to 11 work

wire next_bit = (bit_spacing==4'd10);

always @(posedge clk)

if(state==0)

bit_spacing <= 4'b0000;

else

if(Baud8Tick)

bit_spacing <= {bit_spacing[2:0] + 4'b0001} | {bit_spacing[3], 3'b000};

always @(posedge clk)

if(Baud8Tick)

case(state)

4'b0000: if(RxD_bit_inv) state <= 4'b1000; // start bit found?

4'b1000: if(next_bit) state <= 4'b1001; // bit 0

4'b1001: if(next_bit) state <= 4'b1010; // bit 1

4'b1010: if(next_bit) state <= 4'b1011; // bit 2

4'b1011: if(next_bit) state <= 4'b1100; // bit 3

4'b1100: if(next_bit) state <= 4'b1101; // bit 4

4'b1101: if(next_bit) state <= 4'b1110; // bit 5

4'b1110: if(next_bit) state <= 4'b1111; // bit 6

4'b1111: if(next_bit) state <= 4'b0001; // bit 7

4'b0001: if(next_bit) state <= 4'b0000; // stop bit

default: state <= 4'b0000;

endcase

reg [7:0] RxD_data;

always @(posedge clk)

if(Baud8Tick && next_bit && state[3]) RxD_data <= {~RxD_bit_inv, RxD_data[7:1]};

reg RxD_data_ready, RxD_data_error;

always @(posedge clk)

begin

RxD_data_ready <= (Baud8Tick && next_bit && state==4'b0001 && ~RxD_bit_inv); // ready only if the stop bit is received

RxD_data_error <= (Baud8Tick && next_bit && state==4'b0001 && RxD_bit_inv); // error if the stop bit is not received

end

reg [4:0] gap_count;

always @(posedge clk) if (state!=0) gap_count<=5'h00; else if(Baud8Tick & ~gap_count[4]) gap_count <= gap_count + 5'h01;

assign RxD_idle = gap_count[4];

reg RxD_endofpacket; always @(posedge clk) RxD_endofpacket <= Baud8Tick & (gap_count==5'h0F);

endmodule

程序二 LCD显示模块

module lcd(clk, RxD, LCD_RS, LCD_RW, LCD_E, LCD_DataBus);

input clk, RxD;

output LCD_RS, LCD_RW, LCD_E;

output [7:0] LCD_DataBus;

wire RxD_data_ready;

wire [7:0] RxD_data;

async_receiver deserialer(.clk(clk), .RxD(RxD), .RxD_data_ready(RxD_data_ready), .RxD_data(RxD_data));

assign LCD_RW = 0;

assign LCD_DataBus = RxD_data;

wire Received_Escape = RxD_data_ready & (RxD_data==0);

wire Received_Data = RxD_data_ready & (RxD_data!=0);

reg [3:0] count;

always @(posedge clk)

if(Received_Data | (count!=0)) count <= count + 1;

// activate LCD_E for 10 clocks, so at 40MHz, that's 10x25ns=250ns

reg LCD_E;

always @(posedge clk)

if(LCD_E==0)

LCD_E <= Received_Data;

else

LCD_E <= (count!=10);

reg LCD_instruction;

always @(posedge clk)

if(LCD_instruction==0)

LCD_instruction <= Received_Escape;

else

LCD_instruction <= (count!=11);

assign LCD_RS = ~LCD_instruction;

endmodule