长江大学实验报告

姓名 实验日期 月 日 班级 序号 成绩

周次 星期 (上午、下午、晚上) 指导教师

实验名称 章节名称+大体标本及切片观察

切片编号: 观察倍数: 10×10

镜下分析:

病理诊断:

教师: 年 月 日

第二篇:实验报告的撰写格式及样本

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CNT16 is

port( CLK,RST,EN: in std_logic;

CQ: OUT std_logic_vector(3 downto 0);

COUT:OUT std_logic);

end CNT16;

architecture behav of CNT16 is

begin

process(CLK,RST,EN)

VARIABLE CQI:std_logic_vector(3 downto 0);

begin

if RST='1' then CQI:=(others=>'0');

elsif CLK'event and CLK='1' then

if EN='1'then

if CQI<15 THEN CQI:=CQI+1;

else CQI:=(others=>'0');

end if;

end if;

end if;

if CQI=15 THEN COUT<='1';

else COUT<='0';

end if;

CQ<=CQI;

end process;

end architecture behav;

实验报告的格式:

实 验 名 称

一、实验目的

二、实验内容

三、实验条件

(1)、开发软件 Max+Plus II 或者 Quartus II

(2)、实验设备 GW-48系列EDA实验开发系统

(3)、所用芯片 Altera公司ACEX1K系列的EP1K30TC144-3芯片

四、实验设计

(1)、系统的原理框图

(2)、原理图/VHDL源程序

(3)、波形及仿真文件

(4)、管脚锁定文件(管脚锁定情况,在rpt文件里可以看到)

五、实验结果及总结

(1)、系统仿真情况

(2)、硬件验证情况

(3)、实验过程中出现的问题及解决的办法

注意:统一用五号宋体,行间距为1.5倍。

实验报告样本:

姓名: 李某某 学号: 06005

数字频率计设计实验

一、 实验目的

1. 熟悉Max+PlusⅡ和GW-48型EDA开发系统的使用

2. 掌握具有一定复杂程度的综合电路设计

二、 实验内容

设计并调试好4位十进制数字频率计,并用EDA实验开发系统进行硬件验证。

三、 实验条件

(1)、开发软件 Max+Plus II 或者 Quartus II

(2)、实验设备 GW-48系列EDA实验开发系统

(3)、所用芯片 Altera公司ACEX1K系列的EP1K30TC144-3芯片

四、 实验设计

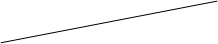

(1)、系统的原理框图

图1 系统的总原理框图

(2)、VHDL源程序及时序仿真

文件一:TEST_CTL.VHD测频控制信号发生器:产生1S脉宽的周期信号和锁存、清零信号

---------------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TEST_CTL IS

PORT(

CLK : IN STD_LOGIC; --1hZ的输入时钟

TEST_EN : OUT STD_LOGIC; --计数时钟使能,脉宽为1S

LOAD : OUT STD_LOGIC; --锁存信号

CLR_CNT : OUT STD_LOGIC); --清零信号

END TEST_CTL;

…………

ELSE CLR_CNT <= '0';

END IF;

END PROCESS;

TEST_EN <= DIV2_CLK;

LOAD <= NOT DIV2_CLK;

END a;

-------------------------------------------------------------------------

图2 TEST_CTL.VHD的时序仿真波形图

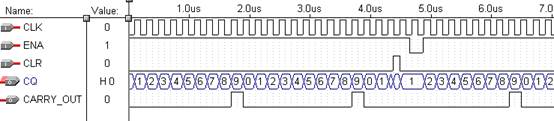

文件二:CNT10.VHD--带有时钟使能异步清零的十进制计数器

-------------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY IS

PORT(

CLK : IN STD_LOGIC; --计数时钟信号

…………

END a;

--------------------------------------------------------------------

图3 cnt10.vhd的时序仿真波形图

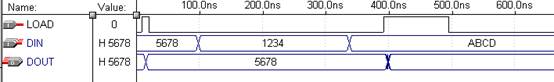

文件三:REG16.VHD--16位锁存器,好处:显示的数据稳定,不会由于周期性的清零信号而不断的闪烁。

------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG16 IS

PORT(

LOAD : IN STD_LOGIC; --锁存允许信号

DIN : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END REG16;

……

END PROCESS ;

END a;

―――――――――――――――――――――――――――

图4 REG16.VHD的时序仿真波形图

图5 顶层设计文件的时序仿真波形图

(CLK=1S,F_IN=175US,END_TIME=5S)

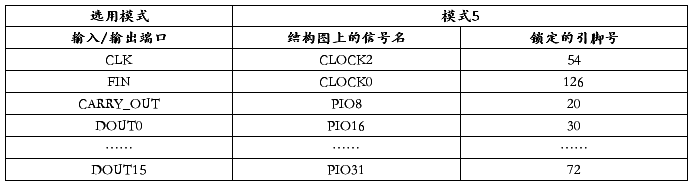

(3)、管脚锁定情况

五、实验结果及总结

1.CLK接CLOCK2中的1Hz。

2.当FIN接CLOCK5中的1024Hz-显示1024Hz;4096Hz-显示4196Hz;

32768Hz-显示2776Hz,并且指示灯D1周期性变化,每周期连续闪动三次。

3.当FIN接CLOCK0中的16384Hz-显示6410Hz,指示灯D1周期性闪动。

4. 当测量四位或四位以下的频率值,数码显示的准确性较高。

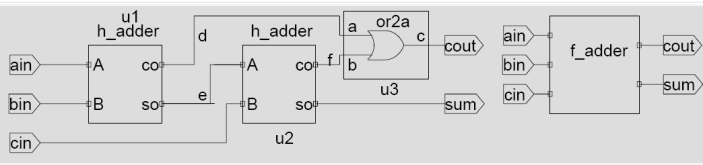

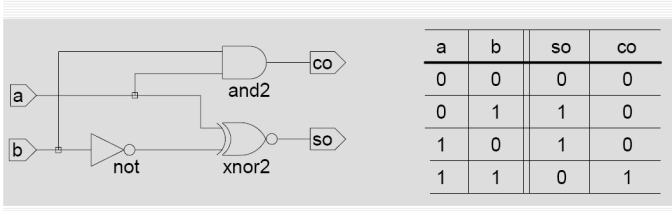

实实验一 用原理图输入法设计一位全加器

一 实验目的

1、熟悉利用QuartusII的原理图输入方法设计简单组合电路

2、掌握层次化设计方法

3、并通过一个一位全加器的设计把握利用EDA软件进行电子线路设计的详细流程

二 实验内容

1、器材用品:

计算机一台

2、步骤

1、建立工作库文件夹;

2、编辑设计一位全加器的原理图;半加器原理图

3、在QuartusII软件上进行原理图仿真;

4、

5、实验结果及总结。

l LIBRARY IEEE; --半加器描述(2):真值表描述方法

l USE IEEE.STD_LOGIC_1164.ALL;

l ENTITY h_adder IS

l PORT (a, b : IN STD_LOGIC;

l co, so : OUT STD_LOGIC);

l END ENTITY h_adder;

l ARCHITECTURE fh1 OF h_adder is

l SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; --定义标准逻辑位矢量数据类型

l BEGIN

l abc <= a & b ; --a相并b,即a与b并置操作

l PROCESS(abc)

l BEGIN

l CASE abc IS --类似于真值表的CASE语句

l WHEN "00" => so<='0'; co<='0' ;

l WHEN "01" => so<='1'; co<='0' ;

l WHEN "10" => so<='1'; co<='0' ;

l WHEN "11" => so<='0'; co<='1' ;

l WHEN OTHERS => NULL ;

l END CASE;

l END PROCESS;

l END ARCHITECTURE fh1 ;

LIBRARY IEEE; --半加器描述(1):布尔方程描述方法

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;