用VHDL设计4位加法计数器的实验报告

一、 实验目的

1.熟悉MAX+plus的VHDL文本设计流程全过程,

2、学习4位硬件加法器的设计;

3、进一步了解使用VHDL表达和设计电路的方法。

二、 实验原理

试验11用图是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,例6-18是其VHDL描述。由图所示,图中间是4位锁存器;rst是异步清信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

三、 实验过程

1.打开Mux+plusII,选菜单 File?New,在 弹出的File Type 窗中选程序编辑输入项,按OK后将打开程序编辑窗。

2、(1)在程序编辑窗中的输入程序后点击选项File ?“Save As”,存在最开始的一个工作库中。

(2)保存时注意保存类型为vhd,文件名字和实体名字一致,不然编译会出错。

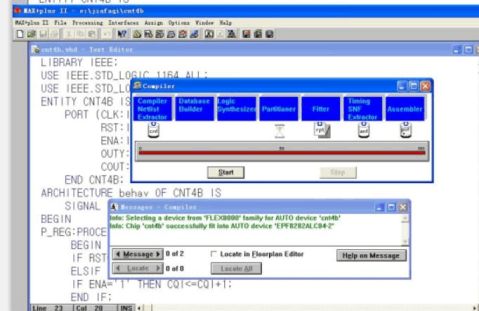

(3)选择File ? Project ? Set Project to Current File,即将当前设计文件设置成Project。最后启动编译器,首先选择左上角的MAX+plusII选项,在其下拉菜单中选择编译器项,点击Start,开始编译!如果发现有错,排除错误后再次编译., (结果见下图1。)

3.接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:

(1)建立波形文件。选择File项及其New,再选择New窗中的Waveform Editer.项,打开波形编辑窗。

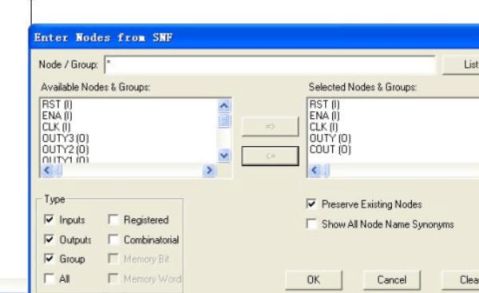

(2)输入信号节点。在波形编辑窗的上方选择Node项,在下拉菜单中选择输入信号节点项Nodes from SNF。在弹出的窗口中首先点击List键,这时左窗口将列出该项设计所以信号节点。由于设计者有时只需要观察其中部分信号的波形,因此要利用中间的“=>”键将需要观察的信号选到右栏中,然后点击OK键即可(结果见下图2)

1

(3)设置波形参量。波形编辑窗中已经调入了所有节点信号,首先设定相关的仿真参数。在Options选项中消去网格对齐Snap to Grid的选择(消去勾),以便能够任意设置输入电平位置,或设置输入时钟信号的周期。

(4)设定仿真时间宽度。选择File项及其End time选项,在End time选择窗中选择适当的仿真时间域20us,以便有足够长的观察时间。

(6)加上输入信号对波形文件存盘。选择File项及其Save as选项,按OK键即

(7)运行仿真器。选择MAX+plusII项及其中的仿真器Simulator选项,点击跳出的仿真器窗口中的Start键。下图是仿真运算完成后的时序波形。

2

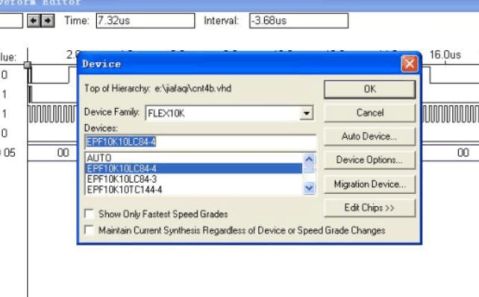

(8)选择目标器件:首先在Assign选项的下拉菜单中选择器件选择项Device, 此窗口的Device Family是器件序列栏,应该首先在此拦中选定目标器件对应的序列名,如EPM7128S对应的是MAX7000S系列;EPF10K10对应的是FLEX10K系列等。为了选择EPF10K10LC84-4器件,应将此栏下方标有Show only Fastest Speed Grades的勾消去,以便显示出所有速度级别的器件。完成器件选择后,按OK键。

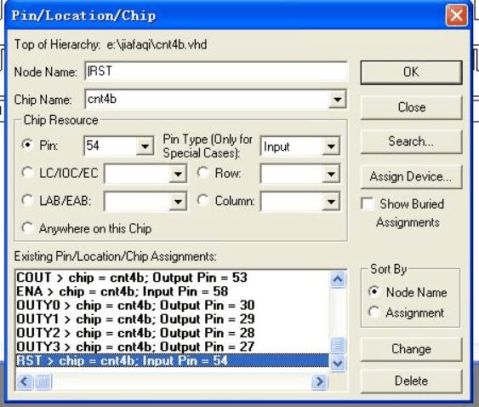

实验内容3:引脚锁定

1.选择Assign项及其中的引脚定位Pin\Location\Chip选项,在跳出的窗口中的Node Name栏中用键盘输入多路选择器的端口名,如果输入的端口名正确,在右侧的Pin Type栏将显示该信号的属性。

2、在左侧的Pin一栏中,用键盘输入该信号对应的引脚编号,然后按下面的Add键。将所有信号锁定在对应的引脚上,按OK键后结束。

3、特别需要注意的是,在锁定引脚后必须再通过MAX+plusII的Compiler选项,

3

对文件从新进行编译一次,以便将引脚信息编如入下载文件中。

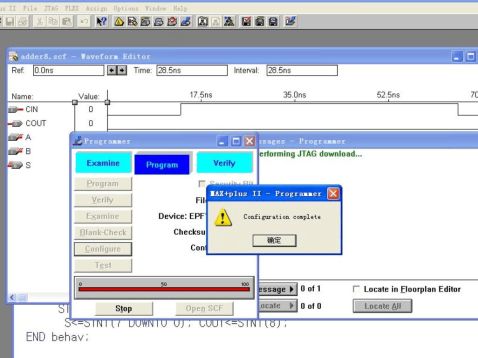

编程下载:

首先将下载线把计算机的打印机口与目标板(如开发板或实验板)连接好,打开电源:

1.下载方式设定。选择MAX+plusII项及其中的编程器Programmer选项,跳出如编程器窗口,然后选择Options项的Hardware Setup硬件设置选项,在其下拉菜单中选ByteBlaster(MV)编程方式。此编程方式对应计算机的并行口下载通道,“MV”是混合电压的意思,主要指对ALTERA的各类芯核电压(如5V、3.3V、

2.5V与1.8V等)的FPGA/CPLD都能由此下载。此项设置只在初次装软件后第一次编程前进行,设置确定后就不必重复此设置了。

2、下载。点击Configure键,向EPF10K10下载配置文件,应出报告配置完成的信息提示。如下图所示 4

四、实验心得

文件编译仿真和调用时经常出现因名字保存错误和没设置工程而出现错误,无法找到文件夹正常工作,还要注意每次修改后注意保存和重新编译,刚开始做的时候进度特别慢,对设计流程和软件不够熟悉,多次操作之后慢慢变得熟练。

5

第二篇:南理工紫金学院eda实验二

EDA技术与应用

实验报告

南京理工大学紫金学院电光系

一、 实验目的(四号+黑体)

1)学习VHDL代码修改。

2)利用when…else… 并行语句描述4位格雷码/二进制码转换电路。

3)利用generate并行语句描述n位格雷码/二进制码转换电路。

4) 利用实验箱验证所设计电路的正确性,要求将输入输出的数据用数码管显示。

二、 实验原理

4位格雷码转换为二进制表达式为:

4位格雷码转换为二进制表达式为:

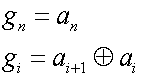

n位格雷码转换为二进制表达式为:

n位格雷码转换为二进制表达式为:

WHEN ELSE 条件信号赋值语句

目标信号<=表达式1 when 条件1 else

表达式2 when 条件2 else

......

表达式n-1 when 条件n-1 else

表达式n;

GENERATE语句

标号:for 循环变量 in 离散范围 generate

并行处理语句;

end generate 标号;

三、 实验内容

实验的代码1::

library ieee;

use ieee.std_logic_1161.all;

entity gtob_1 is

port(g1,g2,g3,g4:in std_logic;

b1,b2,b3,b4:buffer std_logic);

end;

architecture rhi of gtob_1 is

begin

b4<=g4;

b3<=b4 xor g3;

b2<=b3 xor g2;

b1<=b2 xor g1;

end rhi;

实验的代码2

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity gtob_2 is

port(g:in std_logic_vector(3 downto 0);

b:buffer std_logic_vector(3 downto 0));

end gtob_2;

architecture rhg of gtob_2 is

begin

b<="0000"when g<="0000" else

"0001"when g<="0001" else

"0011"when g<="0010" else

"0010"when g<="0011" else

"0111"when g<="0100" else

"0110"when g<="0101" else

"0100"when g<="0110" else

"0101"when g<="0111" else

"1111"when g<="1000" else

"1110"when g<="1001" else

"1100"when g<="1010" else

"1101"when g<="1011" else

"1000"when g<="1100" else

"1001"when g<="1101" else

"1011"when g<="1110" else

"1010";--when g<="0000" else

end rhg;

实验代码3:

library ieee;

use ieee.std_logic_1164.all;

entity gtob_3 is

port(g:in std_logic_vector(3 downto 0);

b:out std_logic_vector(3 downto 0));

end gtob_3;

architecture rhg of gtob_3 is

begin

process (g)

begin

case g is

when "0000"=>b<="0000" ;

when"0001"=>b<="0001" ;

when"0011"=>b<="0010" ;

when"0010"=>b<="0011" ;

when "0111"=>b<="0100" ;

when "0110"=>b<="0101" ;

when "0100"=>b<="0110" ;

when "0101"=>b<="0111" ;

when"1111"=>b<="1000" ;

when"1110"=>b<="1001";

when"1100"=>b<="1010";

when "1101"=>b<="1011" ;

when"1000"=>b<="1100";

when"1001"=>b<="1101" ;

when"1011"=>b<="1110" ;

when "1010"=>b<="1100";--when g<="0000" else

end case;

end process;

end rhg;

实验代码4:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity gtob_4 is

generic(n:integer:=3);

port(g:in std_logic_vector(n downto 0);

b:buffer std_logic_vector(n downto 0));

end gtob_4;

architecture reg of gtob_4 is

begin

b(n)<=g(n);

g1:for i in 0 to n-1 generate

b(i)<=g(i)xor b(i+1);

end generate g1;

end reg;

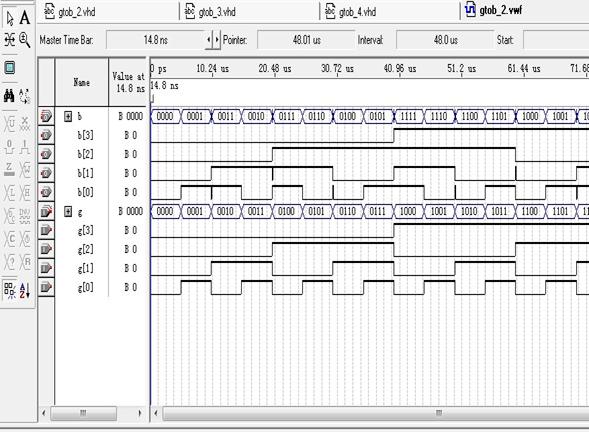

实验波形图:

四、 小结与体会

我学会了when,else的语句用法,复习了格雷码和二进制之间的转化。

学会利用软件来仿真格雷码和二进制码的转化。

代码编写时要认真仔细,编程前要理清思路掌握语法,这样才能快速编出程序。

建立仿真波形,注意要设置初值和end time 。