实验一

实验目的:

熟悉quartus的vhdl文本设计流程全过程,学习简单的组合电路的设计,多层次的电路设计,仿真和硬件测试

二、实验内容

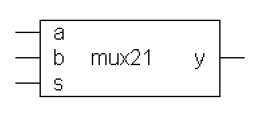

内容(一)用vhdl语言设计2选1多路选择器

参考例3-1程序设计如下:

library ieee;

use ieee.std_logic_1164.all;

entity mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one

全程编译后软件提示0错误,3警告,可以继续下面仿真操作。

程序分析:

这是一个2选1多路选择器,a和b分别为两个数字输入端的端口名,s为通道选择控制信号输入端的端口名,y为输出端的端口名。

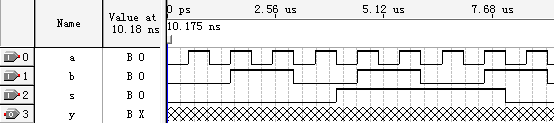

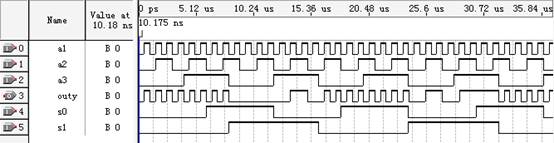

时序仿真及分析:

时序仿真输入图:

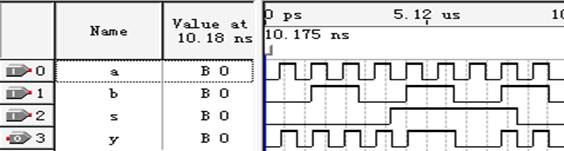

时序仿真输出图:

时序分析:

由上面两图可以得知:当s=0时,y口输出a,当s=1时,y口输出b

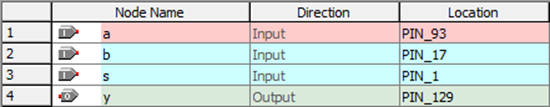

下载和硬件测试:

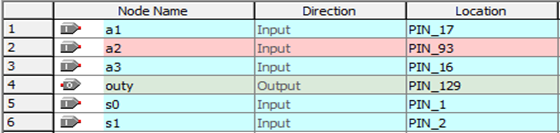

引脚锁定图:

引脚锁定图:

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz信号,clock2接8Hz信号。通过键一控制s,当键一进行切换时,明显能听到扬声器发出两种不同音调的声音。

实验内容(二)双二选一多路选择器设计

程序设计:

library ieee;

use ieee.std_logic_1164.all;

entity mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one;

entity muxk is

port (a1,a2,a3,s0,s1:in bit;

outy:out bit);

end entity muxk;

architecture bhv of muxk is

component mux21a

port (a,b,s:in bit;

y:out bit);

end component;

signal tmp: bit;

begin

u1:mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);

u2:mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);

end architecture bhv;

全程编译后软件提示0错误,2警告

程序分析:

这是一个双2选1多路选择器,a1、a2和a3分别为两个数字输入端的端口名,s0、s1为通道选择控制信号输入端的端口名,outy为输出端的端口名。实体mux21a是一个2选一选通电路,实体muxk是元件的例化,其作用是将两个mux21a组合成一个3选1多路选择器。

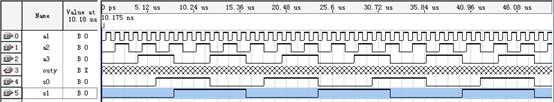

时序仿真及分析:

时序仿真输入图

时序仿真输出图

时序分析:

从仿真出来的结果,我们不难发现,s0和s1做为a1、a2、a3的选通控制信号。当s0=0.、s1=0时,outy输出a1;当s0=0.、s1=1时,outy输出a2;当s0=1.、s1=0时,outy输出a1;当s1=1.、s2=1时,outy输出a3;

下载和硬件测试:

引脚锁定图

引脚锁定图

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz信号,clock2接8Hz信号,clock5接1024Hz。通过键一、键二分别控制s1、s2,当键一、键二进行切换时,明显能听到扬声器发出三种不同音调率的声音。

实验结果:

在实验一中内容一和内容二编译,仿真都没问题,除了有两三个警告以外,并无其他错误,但是在下载过程中,由于设置编程器处出现一点问题,导致下载失败,经过请教,调整后成功运行

四、实验过程所出现的问题及其解决

首先,仿真结果出现延时,应该将a,b,s的周期增大些,且要保证单位为us,刚开始做实验内容(一)时,文件夹名字与程序中所用的实体名不一致,导致程序运行时无法找到文件夹,无法正常工作,经更改后,正常运行,同时文件夹名字不用汉字和数字,以免出错。每次修改过程都应该注意保存,才能将修改的结果反映到所输出的波形中,刚开始常常忘记,经过多次操作后才能够熟练运用。

HDL程序设计

—组合逻辑电路设计

班级:08级通信工程二班

学号:

姓名:

第二篇:2 选1 多路选择器

2 选1 多路选择器

LIBRARY IEEE;

--IEEE 库使用说明

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux21 IS

--器件mux21 的外部接口信号说明

--PORT相当于器件的引脚,这一部分称为实体

PORT ( a b : IN STD_LOGIC;

s : IN STD_LOGIC;

y : OUT STD_LOGIC );

END ENTITY mux21;

--器件mux21 的内部工作逻辑描述即

--为实体描述的器件功能结构称为结构体

ARCHITECTURE one OF mux21 IS

BEGIN

y <= a WHEN s = '0' ELSE

b WHEN s = '1' ;

END ARCHITECTURE one;

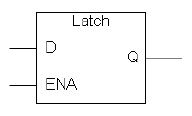

1位锁存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

--锁存器的实体 定义了此器件的

--输入输出引脚及其信号属性

ENTITY Latch IS

PORT(

D : IN STD_LOGIC;

ENA : IN STD_LOGIC;

Q : OUT STD_LOGIC

);

END ENTITY Latch

--结构体

ARCHITECTURE one OF Latch IS

--定义信号

SIGNAL sig_save : STD_LOGIC;

--进程语句结构描述逻辑的时序方式

BEGIN

PROCESS (D, ENA)

BEGIN

IF ENA = '1' THEN

sig_save <= D ;

END IF ;

Q <= sig_save ;

END PROCESS ;

END ARCHITECTURE one;

1位全加器

--或门逻辑描述

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2 IS

PORT (a,b :IN STD_LOGIC; c : OUT STD_LOGIC );

END ENTITY or2

ARCHITECTURE fu1 OF or2 IS

BEGIN

c <= a OR b;

END ARCHITECTURE fu1;

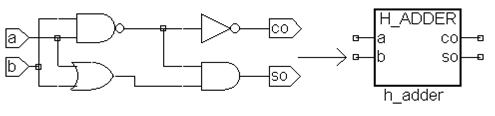

--半加器描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a b : IN STD_LOGIC; co, so : OUT STD_LOGIC);

END ENTITY h_adder

ARCHITECTURE fh1 OF h_adder IS

BEGIN

so <= (a OR b)AND(a NAND b);

co <= NOT( a NAND b);

END ARCHITECTURE fh1;

--1 位二进制全加器顶层设计描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT ( ain bin cin : IN STD_LOGIC;

cout sum : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder

PORT ( a b : IN STD_LOGIC;

co so : OUT STD_LOGIC);

END COMPONENT

COMPONENT or2

PORT (a b : IN STD_LOGIC; c : OUT STD_LOGIC);

END COMPONENT

SIGNAL d e f : STD_LOGIC;

--元件连接

BEGIN

u1 : h_adder PORT MAP( a =>ain b =>bin co=>d so =>e);

u2 : h_adder PORT MAP( a =>e b =>cin co =>f so =>sum);

u3 : or2 PORT MAP(a =>d b =>f c =>cout);

END ARCHITECTURE fd1 ;

1. 实体语句结构

以下是实体说明单元的常用语句结构

ENTITY 实体名 IS

[GENERIC ( 类属表) ]

[PORT ( 端口表 ) ]

END ENTITY 实体名

实体说明单元必须按照这一结构来编写实体应以语句ENTITY 实体名 IS 开始以语句END ENTITY 实体名结束 其中的实体名可以由设计者自己添加。

。。。

COMPONENT h_adder -- 元件调用说明

PORT ( a b : IN STD_LOGIC ;

co so : OUT STD_LOGIC );

END COMPONENT;

。。。。

GENERIC 类属说明语句

GENERIC([ 常数名数据类型 [ : 设定值 ]

{ 常数名 数据类型 [ : 设定值 ] } )

类属参量以关键词GENERIC 引导一个类属参量表,在表中提供时间参数或总线宽度等静态信息。将类属说明放在其中且放在端口说明,语句的前面在一个实体中定义的来自外部赋入。

ENTITY mcu1 IS

GENERIC (addrwidth : INTEGER := 16);

PORT(

add_bus : OUT STD_LOGIC_VECTOR(addrwidth-1 DOWNTO 0) );

...

ENTITY PGAND2 IS

GENERIC ( trise : TIME := 1 ns;

tfall : TIME := 1 ns ) ;

PORT ( a1 : IN STD_LOGIC ;

a0 : IN STD_LOGIC ;

z0 : OUT STD_LOGIC );

END ENTITY PGAND2;

PORT 端口说明

PORT ( 端口名 : 端口模式数据类型

{ 端口名 : 端口模式数据类型} ) ;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY nand2 IS

PORT(a : IN STD_LOGIC ;

b : IN STD_LOGIC ;

c : OUT STD_LOGIC ) ;

END nand2 ;

结构体

结构体的语句格式如下

ARCHITECTURE 结构体名 OF 实体名 IS

[说明语句]

BEGIN

[功能描述语句]

END ARCHITECTURE 结构体名;

结构体中的说明语句,是对结构体的功能描述语句中将要用到的信号(SIGNAL) 数据类型(TYPE) 常数(CONSTANT) 元件(COMPONENT) 函数(FUNCTION) 和过程(PROCEDURE)等加以说明。需要注意的是在一个结构体中,说明和定义的数据类型常数元件函数和过程只能用于这个结构体中。

功能描述语句结构

h块语句是由一系列并行执行语句构成的组合体,它的功能是将结构体中的并行语句组成一个或多个子模块

h进程语句定义顺序语句模块 用以将从外部获得的信号值或内部的运算数据向其它的信号进行赋值

h信号赋值语句将设计实体内的处理结果向定义的信号或界面端口进行赋值

h子程序调用语句用以调用过程或函数 并将获得的结果赋值于信号

h元件例化语句对其它的设计实体作元件调用说明 并将此元件的端与其它的元件信号或高层次实体的界面端口进行连接

块语句结构BLOCK

BLOCK 语句的表达格式如下

块标号BLOCK [ 块保护表达式]

接口说明

类属说明

BEGIN

并行语句

END BLOCK 块标号

接口说明部分有点类似于实体的定义部分,它可包含由关键词PORT GENERIC PORTMAP 和GENERIC MAP 引导的接口说明等语句。对BLOCK 的接口设置以及与外界信号的连接状况加以说明,这类似于原理图间的图示接口说明,块的类属说明部分和接口说明部分的适用范围仅限于当前BLOCK ,所以所有这些在BLOCK 内部的说明对于这个块的外部来说是完全不透明的,即不能适用于外部环境或由外部环境所调用,但对于嵌套于更内层的块却是透明的即可将信息向内部传递块的说明部分可以定义的项目主要有

h 定义 USE 语句

h 定义子程序

h 定义数据类型

h 定义子类型

h 定义常数

h 定义信号

h 定义元件

程序 3-13

a1 : out1 <= '1' after 3 ns ;

blk1 : BLOCK

BEGIN

A2 : out2 <= '1' AFTER 3 ns ;

A3 : out3 <= '0' AFTER 2 ns ;

END BLOCK blk1 ;

程序 3-14

a1 : out1 <= '1' AFTER 3 ns ;

a2 : out2 <= '1' AFTER 3 ns ;

a3 : out3 <= '0' AFTER 2 ns ;

进程PROCESS

PROCESS 语句的表达格式如下

[进程标号] PROCESS [ ( 敏感信号参数表 ) ] [IS]

[进程说明部分]

BEGIN

顺序描述语句

END PROCESS [进程标号]

2. PROCESS 组成

如上所述PROCESS 语句结构是由三个部分组成的即进程说明部分顺序描述语

句部分和敏感信号参数表

(1) 进程说明部分主要定义一些局部量 可包括数据类型常数变量属性子

程序等但需注意在进程说明部分中不允许定义信号和共享变量

(2) 顺序描述语句部分可分为赋值语句 进程启动语句子程序调用语句顺序描

述语句和进程跳出语句等它们包括

h 信号赋值语句 即在进程中将计算或处理的结果向信号SIGNAL 赋值

h 变量赋值语句 即在进程中以变量VARIABLE 的形式存储计算的中间值

h 进程启动语句 当PROCESS 的敏感信号参数表中没有列出任何敏感量时进程

的启动只能通过进程启动语句WAIT 语句这时可以利用WAIT 语句监视信号的变化情况

以便决定是否启动进程WAIT 语句可以看成是一种隐式的敏感信号表

h 子程序调用语句 对已定义的过程和函数进行调用并参与计算

h 顺序描述语句 包括IF 语句CASE 语句LOOP 语句NULL 语句等

h 进程跳出语句 包括NEXT 语句EXIT 语句用于控制进程的运行方向

(3) 敏感信号参数表需列出用于启动本进程可读入的信号名当有WAIT 语句时例

外但VHLD 程序特别是进程结构设计者应当从三个方面去判断它的功能和执行情况

1 基于CPU 的纯软件的行为仿真运行方式

2 基于VHDL 综合器的综合结果所可能实现的运行方式

3 基于最终实现的硬件电路的运行方式

(1) 在同一结构体中的任一进程是一个独立的无限循环程序结构 但进程中却不必

放置诸如软件语言中的返回语句它的返回是自动的进程只有两种运行状态即执行状

态和等待状态

(2) 必须注意 PROCESS 中的顺序语句的执行方式与通常的软件语言中的语句的顺

序执行方式有很大的不同软

(3) 虽然同一结构体中的不同进程是并行运行的但同一进程中的逻辑描述语句则

是顺序运行的因而在进程中只能设置顺序语句

(4) 进程的激活必须由敏感信号表中定义的任一敏感信号的变化来启动否则必须

有一个显式的WAIT 语句来激励

(5) 结构体中多个进程之所以能并行同步运行 一个很重要的原因是进程之间的通

信是通过传递信号和共享变量值来实现的所

(6) 进程是 VHDL 重要的建模工具

(7) 进程有组合进程和时序进程两种类型 组合进程只产生组合电路时序进程产

生时序和相配合的组合电路这两种类型的进程设计必须密切注意VHDL 语句应用的特殊

方面这在多进程的状态机的设计中各进程有明确分工

子程序(SUBPROGRAM)

VHDL 子程序具有可重载性的特点即允许有许多重名的子程序但这些子程序的参

数类型及返回值数据类型是不同的子程序的可重载性是一个非常有用的特性

3.5.1 函数FUNCTION

函数的语言表达格式如下

FUNCTION 函数名参数表RETURN 数据类型--函数首

FUNCTION 函数名参数表RETURN 数据类型 IS -- 函数体

[ 说明部分 ]

BEGIN

顺序语句

END FUNCTION 函数名

1. 函数首

函数首是由函数名参数表和返回值的数据类型三部分组成的

2 函数体

函数体包含一个对数据类型常数变量等的局部说明以及用以完成规定算法或

转换的顺序语句部分一旦函数被调用就将执行这部分语句

在函数体结尾需以关键词END FUNCTION 以及函数名结尾

重载函数 OVERLOADED FUNCTION

VHDL 允许以相同的函数名定义函数但要求函数中定义的操作数具有不同的数据类型以便调用时用以分辨不同功能的同名函数即同样名称的函数可以用不同的数据类型作为此函数的参数定义多次以此定义的函数称为重载函数

过程 PROCEDURE

VHDL 中子程序的另外一种形式是过程PROCEDURE 过程的语句格式是

PROCEDURE 过程名参数表-- 过程首

PROCEDURE 过程名 参数表IS

[说明部分]

BIGIN -- 过程体

顺序语句

END PROCEDURE 过程名

与函数一样过程也由两部分组成即由过程首和过程体构成过程首也不是必需的过程体可以独立存在和使用即在进程或结构体中不必定义过程首而在程序包中必须定义过程首

过程首由过程名和参数表组成参数表可以对常数变量和信号三类数据对象目标作出说明并用关键词IN OUT 和INOUT 定义这些参数的工作模式即信息的流向如

重载过程OVERLOADED PROCEDURE

库LIBRARY

库LIBRARY 的语句格式如下

LIBRARY 库名

IEEE 库是VHDL 设计中最为常见的库它包含有IEEE 标准的程序包和其它一些支

持工业标准的程序

STD_LOGIC_1164NUMERIC_BIT 和NUMERIC_STD 等程序

STD 库

VHDL 语言标准定义了两个标准程序包即STANDARD 和TEXTIO 程序包文件输

入/输出程序包它们都被收入在STD 库中只要在VHDL 应用环境中即可随时调用

这两个程序包中的所有内容即在编译和综合过程中VHDL 的每一项设计都自动地将其

包含进去了由于STD 库符合VHDL 语言标准在应用中不必如IEEE 库那样以显式表

达出来如在程序中以下的库使用语句是不必要的

WORK 库

WORK 库是用户的VHDL 设计的现行工作库用于存放用户设计和定义的一些设计单

元和程序包因而是用户的临时仓库用户设计项目的成品半成品模块以及先期已设

计好的元件都放在其中

VITAL 库

使用VITAL 库可以提高VHDL 门级时序模拟的精度因而只在VHDL 仿真器中使

用

USE 语句的使用将使所说明的程序包对本设计实体部分或全部开放即是可视的USE

语句的使用有两种常用格式

USE 库名.程序包名.项目名

USE 库名.程序包名.ALL

程序包PACKAGE

程序包的内容主要由如下四种基本结构组成因此一个程序包中至少应包含以下结

构中的一种

h 常数说明 在程序包中的常数说明结构主要用于预定义系统的宽度如数据总线

通道的宽度

h VHDL 数据类型说明主要用于在整个设计中通用的数据类型例如通用的地址

总线数据类型定义等第4 章将对数据类型作详细说明

h 元件定义 元件定义主要规定在VHDL 设计中参与文件例化的文件已完成的设

计实体对外的接口界面

h 子程序 并入程序包的子程序有利于在设计中任一处进行方便地调用

定义程序包的一般语句结构如下

PACKAGE 程序包名 IS -- 程序包首

程序包首说明部分

END 程序包名

PACKAGE BODY 程序包名 IS -- 程序包体

程序包体说明部分以及包体内

END 程序包名

程序包的结构由程序

配置CONFIGURATION

配置语句的一般格式如下

CONFIGURATION 配置名 OF 实体名 IS

配置说明

END 配置名