电子科技大学成都学院

实验报告册

课程名称: 电路板设计

姓 名: 金超

学 号: 1440510207

院 系: 微电子技术系

专 业: 电子科学与技术

教 师: 孙科

2015年12月23 日

实验一:电路图绘制

一、 实验目的:

给出电路的原理图,为之后的布局做好准备

二、实验原理和内容:

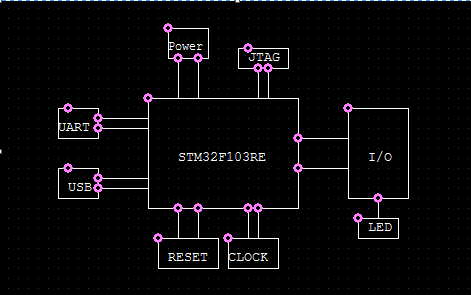

图1

图1是整个电路的大致整体图,每个框代表一个模块,我们需要画出每个模块的原理图(由于整个电路图比较庞大,一个操作页上可能画不下,我们需要用到 这种来表示连接两个分开器件的连接)

这种来表示连接两个分开器件的连接)

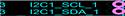

图2

图2是STM32F103RE的处理器的电路图

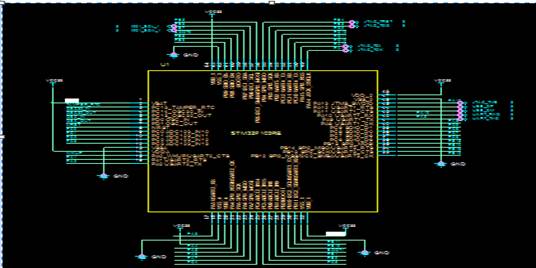

图3

图3所示是con接口电路的原理图,有两个。

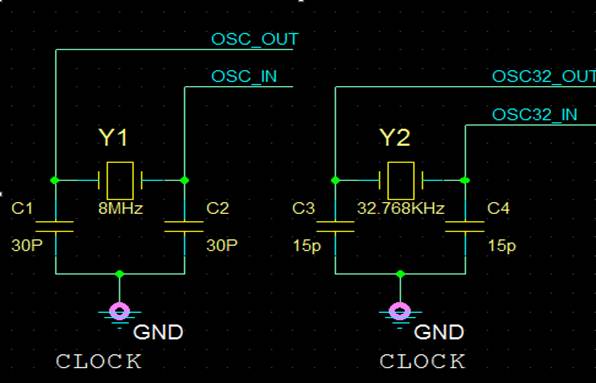

图4

图4为clock时钟电路原理图。

图5

图5 图6

图6

图7

图5为reset复位电路。

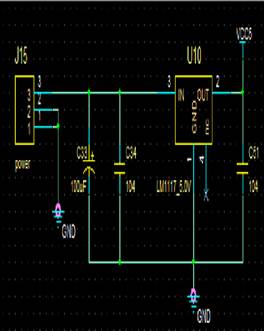

图6为5.0V电源电路图向USB供电。

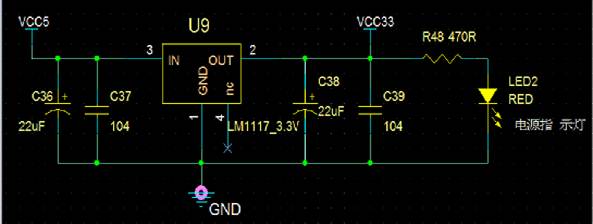

图7为3.3V电源电路图向STM32芯片供电

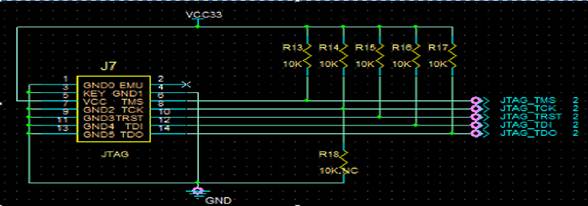

图8

图8为JTAG模块电路。

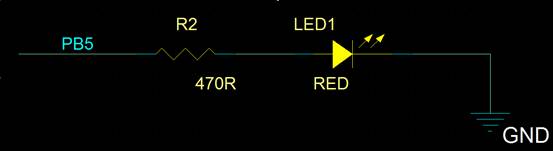

图9

图9为测试LED灯电路。

以上电路图为基本的几个电路模块原理图。这些原理图在接下去的画PCB布局中有着非常重要的作用。

三、 实验步骤:

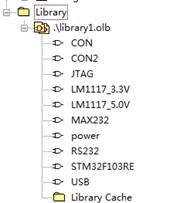

1. 由于有些芯片或者是元器件在cadence的器件库中是没有的,需要我们自己画,所以在library中添加一个文件夹放自定义画的元器件,这里我画了 图中的这些个自定义的元器件。

图中的这些个自定义的元器件。

2. 然后开始画我们的原理图,建立schematic1文件夹来放我们的原理图,这里一共建立了四页原理图。打开其中的一页,首先去调用主要大的器件,比如画第二页stm32f103ret6时,先调用事先画好的stm32的芯片,然后再去调用,标准器件库中有的电阻电容等这些通用元器件。

四、 实验数据和结果:

完成了基本原理图的绘制。

五、实验总结:

通过画原理图,自己画有些元器件,我从中差不多摸到了cadence入门画原理图的门,这里有一些值得注意的地方,首先是在画自定义器件的时候,引脚的编号自己数字计算好,可以省去很多时间去修改引脚的编号,还有一点就是每次元器件画完,一定要记得将虚线变成实线。然后在画原理图的时候,特别注意的是在连接两个期间时,用的是wire来连线,而不是line,如果弄错。后面就十分麻烦修改。还有就是在给每个元器件编号的时候,特别是电阻跟电容,因为数量庞大,一定要注意编号不要编错。这对后面的布局选取元器件的编号很有影响,还有那个每个元器件都有两个可以编辑的框,一个是text框,这是修改元器件的编号的,还有一个是修改参数和它的大小的,千万别搞错,我上面有一个电阻,把修改参数的框我改成了编号。把编号改成了参数。导致后面布局的时候出现了一个33R的编号的电阻。

通过两三周的画原理图,也学会了许多。画原理图是一门注意力集中的精工细活,不能有一点马虎,在以后的工作生活中,也会记得在画原理图的过程中一定会小心小心再小心,细心细心再细心。

实验二: 封装焊盘的制作

一、实验目的:

做出每个器件引脚的焊盘,而后制作器件的封装,后面调用起来进行布局制作PCB。

二、实验原理和内容:

每个直插式的元器件都有引脚,我们需要画出每个引脚的焊盘,然后给他做封装。做出每一个元器件的封装之后,就可以调用,用来布局,制作PCB板了。

三、实验步骤:

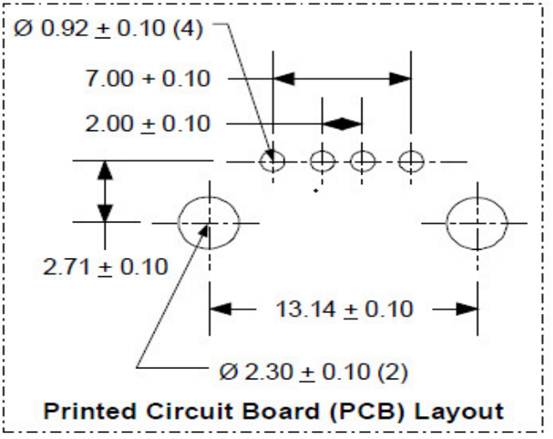

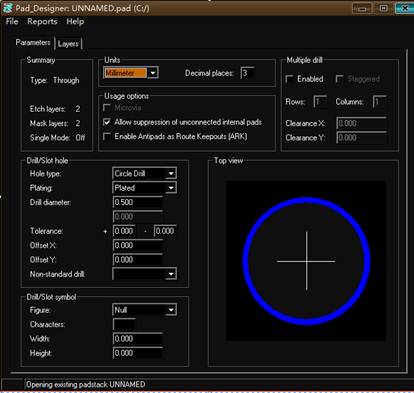

我们以制作USB的封装为例。

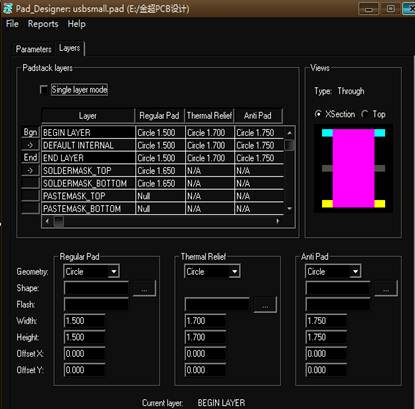

1. 首先找到USB的元器件说明书 2.在软件pad designer的软件中,根据说明说给出的数据设置参数,制作引脚的焊盘

2.在软件pad designer的软件中,根据说明说给出的数据设置参数,制作引脚的焊盘

完了保存之后。

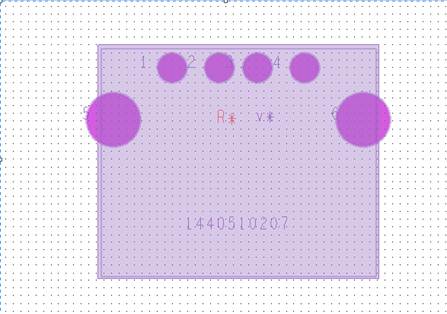

3. 打开PCB editor软件,然后调用焊盘,然后在调用给出的参数

合理的放置几个焊盘的位置,制作USB的封装,最后后的成品图如下所示。

4. 剩下所有的元器件,都按照这个步骤一一做完保存,这样我们的第二个实验大步骤也就完成了。

五、 实验数据和结果:

完成了各个器件引脚焊盘的绘制,并制作成各个器件的封装。

五、实验总结:

一开始在画焊盘,调用焊盘制作封装的时候一点都摸不着头绪,跟着老师手把手的教学,连续画完了两个,自己单独画第三个的时候又不会了。还是相当的恼火,后面自己课后照着书本一边研究一边画,自己完完整整的画了一个,突然就开窍了,一些数据的设置跟调用的方式,都比较清楚了,这里需要注意的是在画焊盘的时候,那些数据的设置,热风焊的参数要比焊盘的参数稍微大个0.2——0.3mm左右,焊盘边距可以适当的比热风焊再大个一些,最好选取整数或者偶数,这样子,你在调用焊盘,画封装的时候计算坐标比较方便。说到封装这一块,坐标绝对是一个脑力活跟精细活,你的坐标原点一定要选好,这样子可以省好多计算量,也能避免错误的发生。算完了每个焊盘的坐标,那么放上去只需要在下面输坐标,直接放上去就好了。省力又美观。

通过画焊盘,做封装,我觉得做什么。都不能完全跟着别人做,自己一味的模仿不去思考。只要自己边思考边做一遍,那印象就会很深刻,后面的事情就游刃有余,如果不思考,别人怎么做。你也怎么做,那让你独立的做第二遍还是没什么用,你还是不会。

实验三: PCB绘制

一、实验目的:

布局封装,画PCB板子。

二、实验原理和内容:

用实验二做完的各个器件的封装,根据电路图,进行布局,然后连线,最后敷铜完成PCB的制作。

三、实验步骤:

1. 先回到原理图给每个器件添加封装。双击原理图中的一个器件。然后在PCB footprint中添加这个器件所属封装的名字。然后点击APPLY应用之后即可。所有的原理图中的器件全部按照这种方法添加封装名字。

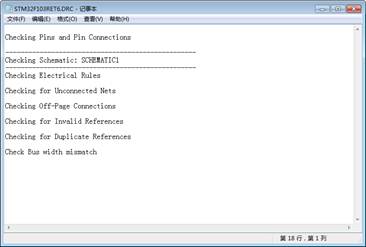

2.回到文件主界面 选中图中的文件夹,在工具栏tools菜单中,找到 design rules check 来进行设计规则检查,相关参数勾选完成后,点击确定之后,会出现一个检查提示信息,如果原理图中哪里有错误,他会在上面显示出来,只需要找到这个器件的坐标去检查修改就好了。等到没有错误为止

选中图中的文件夹,在工具栏tools菜单中,找到 design rules check 来进行设计规则检查,相关参数勾选完成后,点击确定之后,会出现一个检查提示信息,如果原理图中哪里有错误,他会在上面显示出来,只需要找到这个器件的坐标去检查修改就好了。等到没有错误为止 ,开始下一步。

,开始下一步。

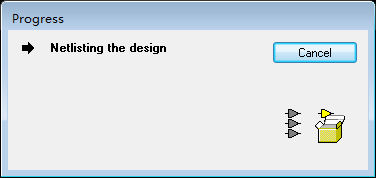

3.开始创建网络表。在tools菜单中选择create netlist 选择好网络表存放的位置,点击确定,将开始创建网络表。 创建完成后,在下面查看是否有错误。

创建完成后,在下面查看是否有错误。

这边已经没有了error,说明错误没了,那么我们可以进行下一步了。如果有错误,就找到那个元器件的位置,自己根据提示去修改,然后重复操作,知道没有error出现为止。

4. 在pcb editor 中打开,创建电路板工程,后缀名为.brd文件,放到自己的工程文件夹中。然后进行各项参数的设置,包括环境参数设置,单位设置,坐标系设置,Grids设置。完成设置后,点击OK。然后进行电路板层数的设置,在右边的二级菜单栏中的Visibility中打开,具体的设置参考教材。

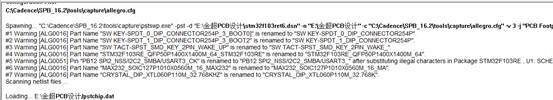

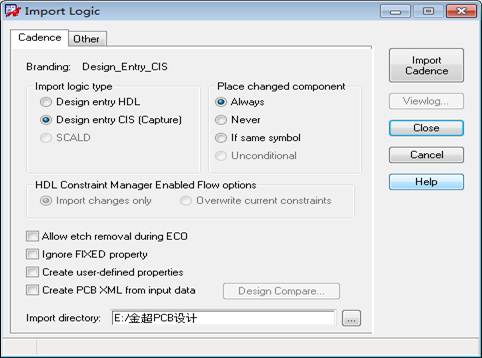

5. 一切准备就绪之后,开始导入网络表。点击file 菜单栏下的import,选择logic出现如下页面。

选择好路径之后,点击右上角的 import cadence 将网表导入其中。

6. 如果成功导入网表之后,找到place菜单,从下拉菜单中找到manually ,你会看到你之前所有做的封装,都在里面。然后又是一大堆的设置操作。详情参考教材。

7. 器件的布局。这里将是比较关键的一步。遵循以CPU为核心,然后依次向外面放器件封装,大的封装先放,然后再找到每一个模块的电路图,根据电路图把小的电容,电阻等这些元器件放到大的封装的旁边,尽量让走线短,而且交错的少。

8. 在布局完之后,接下去就是连线的操作。这里还是先从大的器件开始连,鼠标移动到窗口上方“Route”菜单,从下拉菜单中找到connect的画线命令。或者直接在左边的快捷按钮上找到画线命令操作。找到一个引脚点击之后,会出现与之可以相连的地方成高亮色。点击高亮处,即连接。

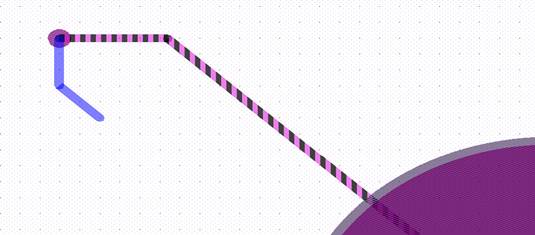

当两条线相交时,不能连接,这个时候需要打孔,在空白处点击一下,然后左键add via,打孔后再连接。如下图。

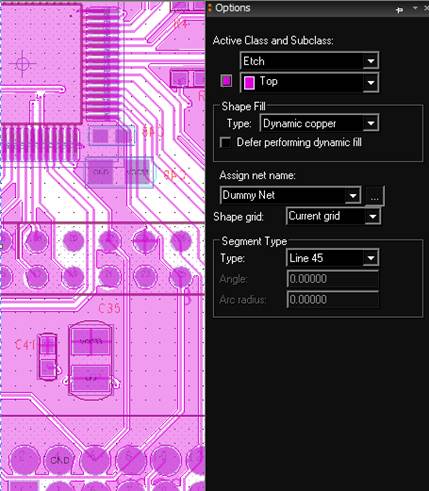

9.当把器件基本上连线连完之后,我们需要对VCC和GND设置成大面积的金属层,也就是敷铜操作。这里以5V电源敷铜操作为例:把鼠标移动到窗口上方的shape上,点击左键,从下拉菜单中选择第一个polygon 命令。然后将鼠标移动到窗口右边选择OPTION菜单,弹出option设置窗口。如下图

10.在assign net name栏点击右边的虚线图标按钮,弹出网络名选择窗口,拖动滑条,选择Vcc5的网络名,左击选中之后,点击OK,回到option设置窗口。然后再这上面设置敷铜的网络属性和放置的位置层。其他的默认。

11.设置完成后,鼠标移动到电路板上,找到5V电源网络的所在位置,选择一个起始位置,一般从板子的左上角开始,按照顺时针方向画一个框,把整个电路板包围在里面。最后回到原始位置,右键选择DONE,所显示的高亮的区域,即为5V网络。

12.全部完成之后,最后进行DRC检查,鼠标移动到窗口上边的display 菜单,点击左键,弹出菜单栏中选择status 命令,如果status窗口各个选项全部编程绿色,那么drc检查通过了,如果出现黄色或者是红色,则点击颜色方块,弹出错误的信息列表,根据提示进行修改。

13.详细的操作请参照教材上的提示完成。

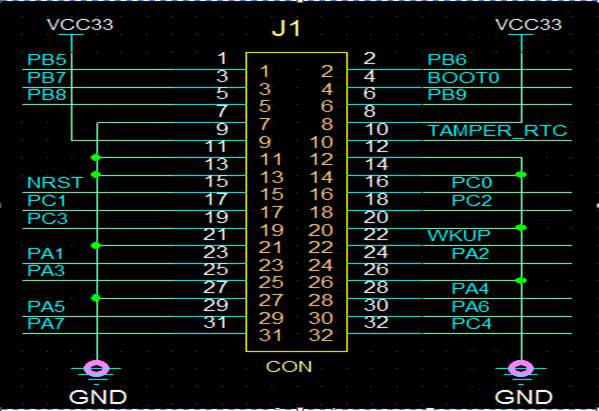

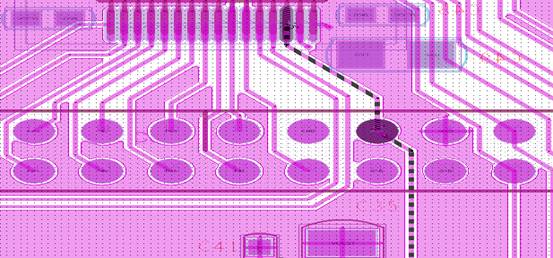

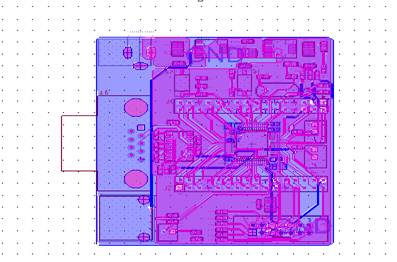

14.整体的效果图如下图所示

完成后的整体效果图

四、实验数据和结果:

完成了网络表的导入,最后完成PCB的成品。

六、 实验总结:

PCB的布局花了我好多的时间,课下放了又删除,删除了又放,真是忙的不亦乐乎,放置元器件在遵循上面说的规则之外,还要自己看电路图,跟着电路图来。不能随便摆,不然连线的时候相当头疼。两线交错也是避免不了的,遇到这种情况。就选择穿孔过去了。。不过一定要少穿孔。我第一次布局的时候,穿了好多孔,最后导致,板子看起来全是孔,后面出现的错误。就无从下手了。所以第一步布局就得做好。做完了布局,连玩了线,到了敷铜这一步的时候,也是要注意,看是否有敷铜无法覆盖某些引脚的现象,如果有。则去删除局部的引脚敷铜。最后删除掉敷铜孤岛。进行DRC检查。全绿。就通过了。

通过这么一次画PCB的经历也是感触颇深。我觉得,这东西一是细心。二是前面的每一步都得做好。任何一步出现了错误。都会对后面产生比较大的影响。主要是修改麻烦。。第三点是,一定要自己动手亲自去摸索自己画。而不是看着别人画一下。自己感觉看懂了。就不动手去亲自画了。这样子。独立让自己画的时候不一定会。希望在以后的学习生活中,cadence还是能够有大的用处的,以后会更加的去研究琢磨这个软件的更深的功能和用法。

第二篇:PCB板实验报告

PCB板实验报告

一, 可焊性试验报告

1, 打开锡炉开关,待锡炉块完全融化成液态,用温度计测量其温度确定温度在245±5℃之

内;

2, 取涂有松香之PCB板,用夹子夹住板两侧,焊接面向下,迅速充分的与锡面接触4—6

秒,然后向脱离锡面;

3, 待PCB冷却后检查判定:

A, 焊盘上锡饱满,湿润面积在95%以上,锡面光滑无漏铜,无阻焊脱落,判定OK; B, 焊锡面粗糙,焊盘漏铜及湿润面积不能完全覆盖焊盘,则判定NG;

二, 抗剥离试验报告

1,

2,

3,

4,

5, 用长约5CM的3M600#胶纸紧贴试验板上,并用碎布将氧泡赶走; 以垂直90℃,迅速拉起胶带; 检查胶带是否粘有异物,OK; 在板四周和中央各重复试验一次。 判定: A,如胶带上未粘有异物,OK;

B,如胶带上粘有异物,则NG;

三, 热冲击试验报告

1,

2, 将待试验之PCB板边缘磨平后,按100℃烘烤20分钟; 打开锡炉电源开关待锡炉完全融化成液态,用温度计测量其温度,确定温度稳定在288

±5℃之内;

3, 用夹子夹住PCB浸入锡炉内,浸泡10±2秒后取出;

4, 待PCB冷却后检查判定;

A, PCB铜箔无起泡,分层,阻焊无脱落,PCB翘曲度≤10%判定OK;

B, PCB出现上述不良情况之一,则判定NG.