实验报告

姓名: 学号:

日期: 成绩:

一、实验目的

1、加深对差动放大器性能及特点的理解

2、学习差动放大器主要性能指标的测试方法

二、实验原理

图5-1是差动放大器的基本结构。 它由两个元件参数相同的基本共射放大电路组成。当开关K拨向左边时,构成典型的差动放大器。调零电位器RP用来调节T1、T2管的静态工作点,使得输入信号Ui=0时,双端输出电压UO=0。RE为两管共用的发射极电阻, 它对差模信号无负反馈作用,因而不影响差模电压放大倍数,但对共模信号有较强的负反馈作用,故可以有效地抑制零漂,稳定静态工作点。

图5-1 差动放大器实验电路

当开关K拨向右边时,构成具有恒流源的差动放大器。 它用晶体管恒流源代替发射极电阻RE,可以进一步提高差动放大器抑制共模信号的能力。

1、静态工作点的估算

典型电路

(认为UB1=UB2≈0)

(认为UB1=UB2≈0)

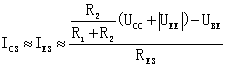

恒流源电路

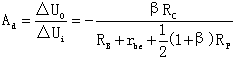

2、差模电压放大倍数和共模电压放大倍数

当差动放大器的射极电阻RE足够大,或采用恒流源电路时,差模电压放大倍数Ad由输出端方式决定,而与输入方式无关。

双端输出: RE=∞,RP在中心位置时,

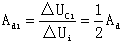

单端输出

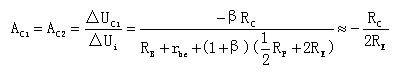

当输入共模信号时,若为单端输出,则有

若为双端输出,在理想情况下

实际上由于元件不可能完全对称,因此AC也不会绝对等于零。

3、 共模抑制比CMRR

为了表征差动放大器对有用信号(差模信号)的放大作用和对共模信号的抑制能力,通常用一个综合指标来衡量,即共模抑制比

或

或

差动放大器的输入信号可采用直流信号也可采用交流信号。本实验由函数信号发生器提供频率f=1KHZ的正弦信号作为输入信号。

三、实验设备与器件

1、±12V直流电源 2、函数信号发生器

3、双踪示波器 4、交流毫伏表

5、直流电压表

6、晶体三极管3DG6×3,要求T1、T2管特性参数一致。

(或9011×3)。

电阻器、电容器若干。

四、实验内容

1、典型差动放大器性能测试

按图5-1连接实验电路,开关K拨向左边构成典型差动放大器。

1) 测量静态工作点

①调节放大器零点

信号源不接入。将放大器输入端A、B与地短接,接通±12V直流电源,用直流电压表测量输出电压UO,调节调零电位器RP,使UO=0。 调节要仔细,力求准确。

②测量静态工作点

零点调好以后,用直流电压表测量T1、T2管各电极电位及射极电阻RE两端电压URE,记入表5-1。

表5-1

2) 测量差模电压放大倍数

断开直流电源,将函数信号发生器的输出端接放大器输入A端,地端接放大器输入B端构成单端输入方式,调节输入信号为频率f=1KHz的正弦信号,并使输出旋钮旋至零, 用示波器监视输出端(集电极C1或C2与地之间)。

接通±12V直流电源,逐渐增大输入电压Ui(约100mV),在输出波形无失真的情况下,用交流毫伏表测 Ui,UC1,UC2,记入表5-2中,并观察ui,uC1,uC2之间的相位关系及URE随Ui改变而变化的情况。

3) 测量共模电压放大倍数

将放大器A、B短接,信号源接A端与地之间,构成共模输入方式, 调节输入信号f=1kHz,Ui=1V,在输出电压无失真的情况下,测量UC1, UC2之值记入表5-2,并观察ui, uC1, uC2之间的相位关系及URE随Ui改变而变化的情况。

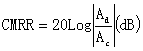

表5-2

2、具有恒流源的差动放大电路性能测试

将图5-1电路中开关K拨向右边,构成具有恒流源的差动放大电路。重复内容1-2)、1-3)的要求,记入表5-2。

五、实验总结

1、 整理实验数据,列表比较实验结果和理论估算值,分析误差原因。

1) 静态工作点和差模电压放大倍数。

在差分放大电路中 ,电路的偏置电阻、晶体管 (BJT)的参数、信号源的内阻、工作温度都会引起输出的误差 .由于前置及高增益 ,差分放大器的误差和零漂会造成整个电路的误差加大。

2) 典型差动放大电路单端输出时CMRR的实测值与具有恒流源的差动放大器CMRR实测值比较。

实验仪器的误差,信号的输出与示波器所测的都有误差;实验板可能用久了,那些板上的器件有损耗;万能表的误差;温度变化引起的零点漂移.还有就是一些实验过程中的操作不对。

2、 比较ui,uC1和uC2之间的相位关系。

Ui和Uc1 Ui和Uc2的相位都是相反的。Uc1和Uc2的相位相同

3、 根据实验结果,总结电阻RE和恒流源的作用。

RE为两管共用的发射极电阻,对共模信号有较强的负反馈作用,可以有效地抑制零漂,稳定静态工作点。恒流源进一步提高差动放大器抑制共模信号的能力。

第二篇:实验四、差分放大器设计

实验四、差分放大器设计

一.实验目的

1.掌握差分放大器的设计方法。

2.掌握差分放大器的调试与性能指标的测试方法。

二.预习要求

1.根据指标要求,设计并计算电路的有关参数。

2.画出所设计的电路,列出元件的值。

3.制定出实验方案,选择实验用的仪器设备。

4.写出预习报告

三.差分放大器的设计方法

1.确定放大电路(选择场效应管)。

2.手工计算场效应管的直流转移特性曲线,并将特性曲线描绘在方格纸上,在曲线上 确定出MOS管的饱和区,确定输入电压、输出电压的范围。

3.确定静态工作点Q:(VImin+VImax)/2

4.确定电路中的其他参数的值。

四.电路的设计要点:

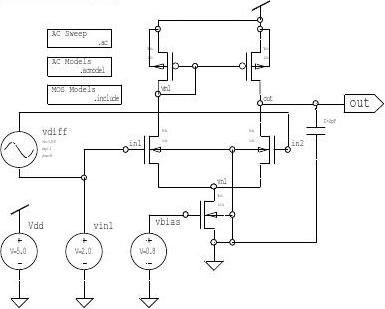

1. 电路图设计参见附录。

2.调整静态工作点:可修改场效应管的w和电阻值。

3.动态调试:从放大器的输入端输入f=1kHz,Ui=100mV的正弦信号(加直流偏置,静态工作点Q)。若放大器的输出波形顶部或底部出现明显失真,说明静态工作点没有设置在恰当的位置,应调整电路使输出波形无明显失真。若顶部和底部同时出现失真,说明静态工作点选择恰当。此时应减小输入信号幅度,使输出波形不失真。

4.测量Au及Δf。

5. 对测量结果进行验算并进行误差分析

(1) 列出静态工作点的测量值

(2) 性能指标的测量值

(3) 根据调整后的电路参数,列出理论计算值。

(4) 将理论计算值与测量值进行比较算出它们的相对误差

五.实验内容

1.按以下指标要求,设计一个差分放大器。

1)电压放大倍数Au≥100

2)负载电阻 RL=10kΩ

3)下限频率fL≤20Hz,上限频率fH ≥200kHz

2.对所设计的电路进行设计、调试。

3.对电路的性能指标进行测试仿真,并对测量结果进行验算和误差分析。

六.实验报告要求

实验报告包括以下内容:

1.项目名称

2.已知条件和指标要求

3.所需的软件仿真语句

4.电路的设计过程,所选用的电路原理图。

5.调试过程,标有经调试后所采用的元件数值的电路图。

6.主要技术指标的计算值、仿真值

7.数据处理及误差分析

8.电路的改进建议和实验中的体会

附录:

1. 所需的软件仿真语句

.include .op .dc .print .tran

.ac DEC 5 1 100MEG 交流仿真语句 .print ac vdb(out) vm(out) 交流输出语句

2. 需要设计的电路图

PMOS负载的NMOS驱动差分电路

自行绘制电阻负载的NMOS驱动差分电路

以下文件与数据仅供参考,但均经过仿真测试,实际使用注意.include路径并加负载电容

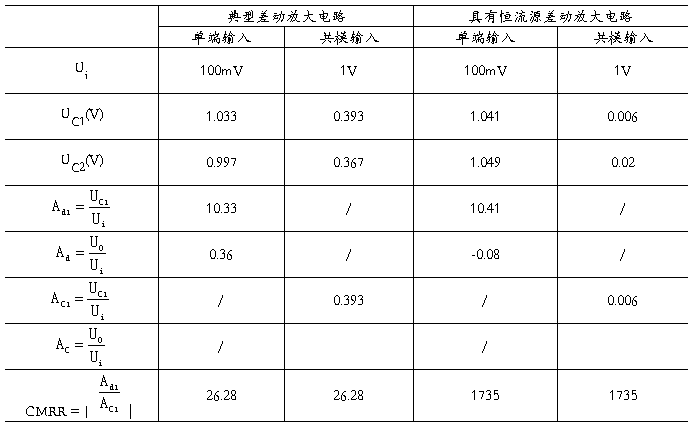

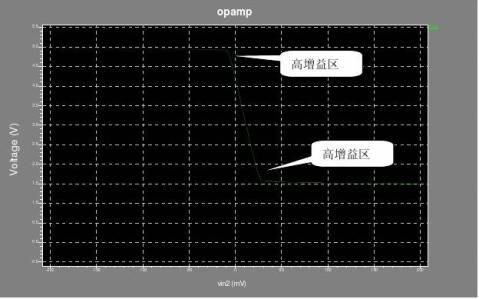

一、共模电压扫描

* Main circuit: opamp

ccomp out Gnd 2pF

mn1 vn1 vbias Gnd Gnd nmos L=10u W=6u

mn2 vm1 in1 vn1 Gnd nmos L=6u W=6u

mn3 out in1 vn1 Gnd nmos L=6u W=6u .

mp1 vm1 vm1 Vdd Vdd pmos L=6u W=6u

mp2 out vm1 Vdd Vdd pmos L=6u W=6u

include ml2_125.md

* End of main circuit: opamp

vbias vbias Gnd 0.8

Vdd Vdd Gnd 5.0

vin1 in1 Gnd 2.5

.dc vin1 0 5 0.1

.print dc in1 out

二、小信号分析

* Main circuit: opamp

ccomp out Gnd 2pF

mn1 vn1 vbias Gnd Gnd nmos L=10u W=6u

mn2 vm1 in1 vn1 Gnd nmos L=6u W=6u

mn3 out in2 vn1 Gnd nmos L=6u W=6u

.include ml2_125.md

mp1 vm1 vm1 Vdd Vdd pmos L=6u W=6u

mp2 out vm1 Vdd Vdd pmos L=6u W=6u

vbias vbias Gnd 0.8

Vdd Vdd Gnd 5.0

vin2 in2 in1 1

vin1 in1 Gnd 2.5

.dc vin2 -2.5 2.5 0.02

.print dc out

* End of main circuit: opamp

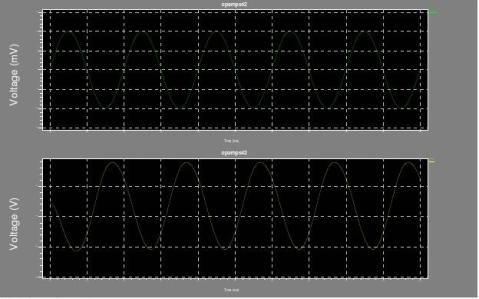

三、动态调整

* Main circuit: opamp

ccomp out Gnd 2pF

mn1 vn1 vbias Gnd Gnd nmos L=10u W=6u

mn2 vm1 in1 vn1 Gnd nmos L=6u W=6u

mn3 out in2 vn1 Gnd nmos L=6u W=6u

.include ml2_125.md

mp1 vm1 vm1 Vdd Vdd pmos L=6u W=6u

mp2 out vm1 Vdd Vdd pmos L=6u W=6u

vbias vbias Gnd 0.8

Vdd Vdd Gnd 5.0

vdiff in2 in1 sin 0 0.015 1000 0.0 0.0 0.0

vin1 in1 Gnd 2.5

.tran 10u 5m

.print tran out v(in2,in1)

* End of main circuit: opamp

四、增益仿真

* Main circuit: opamp

.ac DEC 5 1 100MEG

.acmodel opamp1m.out {*}

ccomp out Gnd 2pF

mn1 vn1 vbias Gnd Gnd nmos L=10u W=6u

mn2 vm1 in1 vn1 Gnd nmos L=6u W=6u

mn3 out in2 vn1 Gnd nmos L=6u W=6u

.include ml2_125.md

mp1 vm1 vm1 Vdd Vdd pmos L=6u W=6u

mp2 out vm1 Vdd Vdd pmos L=6u W=6u

.print ac vdb(out) vp(out)

vbias vbias Gnd 0.8

Vdd Vdd Gnd 5.0

vdiff in2 in1 -0.0007 AC 1.0 90

vin1 in1 Gnd 2.0

* End of main circuit: opamp

* T-Spice 10.10 Simulation Tue Jun 05 08:53:12 2007 C:\Program

EDA\S-Edit\tutorial\schematic\opamp.sp

* Command line: tspice -o "C:\Program Files\Tanner EDA\S-Edit\tutorial\schematic\opamp.out" "C:\Program Files\Tanner EDA\S-Edit\tutorial\schematic\opamp.sp"

* T-Spice Win32 10.10.20050307.17:21:35

* Operating System: Windows XP 5.1 2600 Service Pack 2

*SEDIT: probesdbfile="C:\Program Files\Tanner EDA\S-Edit\tutorial\schematic\opamps41.sdb" *SEDIT: probetopmodule="opamp"

*SEDIT: Alter blocks = 0

* Probing options:

* probefilename = opamps41.dat

* probesdbname = C:\Program Files\Tanner EDA\S-Edit\tutorial\schematic\opamps41.sdb * probetopmodule = opamp

*

* Device and node counts:

* MOSFETs - 5 MOSFET geometries - 3

* BJTs - 0 JFETs - 0

* MESFETs - 0 Diodes - 0

* Capacitors - 1 Resistors - 0

* Inductors - 0 Mutual inductors - 0

* Transmission lines - 0 Coupled transmission lines - 0 Files\Tanner

* Voltage sources - 4 Current sources - 0

* VCVS - 0 VCCS - 0 * CCVS - 0 CCCS - 0 * V-control switch - 0 I-control switch - 0

* Macro devices - 0 External C model instances - 0

* Subcircuits - 0 Subcircuit instances - 0

* Independent nodes - 3 Boundary nodes - 5

* Total nodes - 8

* *** 10 WARNING MESSAGES GENERATED DURING SETUP

*SEDIT: Alter=0

*SEDIT: Analysis types DCOP 0 ACMODEL 0 AC 0 TRANSIENT 0 TRANSFER 0 NOISE 0 * BEGIN NON-GRAPHICAL DATA

AC SMALL-SIGNAL MODELS - temperature=25.0

0 1 2 3

mn1 mn2 mn3 mp1 MODEL nmos nmos nmos pmos

TYPE NMOS NMOS NMOS PMOS REGION Saturation Cutoff Cutoff Saturation

ID 439.46886n 220.00758n 219.45594n -220.01424n

IBS 0. -10.51431f -10.51431f 0.

IBD -10.51431f -42.26207f -42.96842f -7.73793f

VGS 800.00000m 948.56933m 947.86933m -773.79316m VDS 1.05143 3.17478 3.24541 -773.79316m

VBS 0. -1.05143 -1.05143 0.

VTH 613.26877m 1.11014 1.10992 -623.15079m VDSAT 122.93287m 122.57063m 122.57735m -107.43885m RS 0. 0. 0. 0.

RD 0. 0. 0. 0.

GM 4.74927u 1.42837u 1.42480u 2.93066u

GDS 13.69300n 6.36905n 6.28730n 7.64144n

GMB 1.19979u 338.60769n 337.70540n 573.32454n GBD 10.00000f 10.00000f 10.00000f 10.00000f

GBS 389.22857f 10.00000f 10.00000f 389.23393f

CDTOT 1.73400f 1.73400f 1.73400f 2.01000f

CGTOT 76.02715f 15.52382f 15.52578f 46.15251f

CSTOT 48.90369f 1.73400f 1.73400f 28.42784f

CBTOT 22.81544f 12.05582f 12.05778f 10.41229f

CGS 68.85530f 1.73400f 1.73400f 41.34751f

CGD 1.73400f 1.73400f 1.73400f 2.01000f

CGB 5.43786f 12.05582f 12.05778f 2.79500f

CBD 0. -6.58e-024 0. 0.

CBS 11.10157f 0. 0. 4.59680

4

mp2

MODEL pmos

TYPE PMOS

REGION Saturation

ID -219.46282n

IBS 0.

IBD -7.03158f

VGS -773.79316m

VDS -703.15845m

VBS 0.

VTH -623.23662m

VDSAT -107.37133m

RS 0.

RD 0.

GM 2.92482u

GDS 7.97943n

GMB 572.24045n

GBD 10.00000f

GBS 389.23393f

CDTOT 2.01000f

CGTOT 46.15251f

CSTOT 28.42784f

CBTOT 10.41229f

CGS 41.34751f

CGD 2.01000f

CGB 2.79500f

CBD 0.

CBS 4.59680f

* VOLTAGE SOURCES

5 6 7 8 vbias Vdd vdiff vin1 VOLTAGE 800.00000m 5.00000 -700.00000u 2.00000 CURRENT 0. -439.47855n 0. 0. POWER 0. -2.19739u 0. 0. Element name cross-reference:

0 : mn1

1 : mn2

2 : mn3

3 : mp1

4 : mp2

5 : vbias

6 : Vdd

7 : vdiff

8 : vin1

* END NON-GRAPHICAL DATA