实验报告

课程名称:EDA技术实用教程

实验名称:(一)十六进制7段数码显示译码器设计 (二)8位加法器设计实验

(一)十六进制7段数码显示译码器设计

1、实验内容

(1)实验目的:

学习7段数码显示译码器的Verilog硬件设计

(2)实验原理:

7段显示译码器是纯组合电路。通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的。为了满足十六进制数的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD中来实现。所以首先要设计一段程序。设输入的4位码为A[3:0],输出控制7段共阴数码管的7位数据为LED7S[6:0]。输出信号LED7S的7位分别接共阴极数码管7个段,高位在左,低位在右。例如当LED7S输出为“1101101”时,数码管的7个段个g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

(3)实验任务:

将设计好的Verilog译码器程序在Quartus2上进行编辑、编译、综合、适配、仿真。给出其所有信号的时序仿真波形。

2、Verilog代码

module DECL7S (A,LED7S);

input[3:0] A; output[6:0] LED7S;

reg[6:0] LED7S;

always @(A)

case(A)

4'b0000: LED7S<=7'b0111111; 4'b0001: LED7S<=7'b0000110; 4'b0010: LED7S<=7'b1011011; 4'b0100: LED7S<=7'b1100110; 4'b0101: LED7S<=7'b1101101; 4'b0110: LED7S<=7'b1111101; 4'b0111: LED7S<=7'b0000111; 4'b1000: LED7S<=7'b1111111; 4'b1001: LED7S<=7'b1101111; 4'b1010: LED7S<=7'b1110111; 4'b1011: LED7S<=7'b1111100; 4'b1100: LED7S<=7'b0111001; 4'b1101: LED7S<=7'b1011110; 4'b1110: LED7S<=7'b1111001; 4'b1111: LED7S<=7'b1110001; default: LED7S<=7'b0111111; endcase

Endmodule

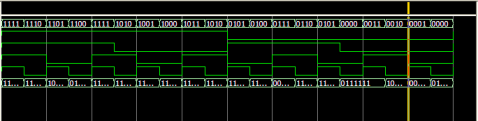

3、仿真图

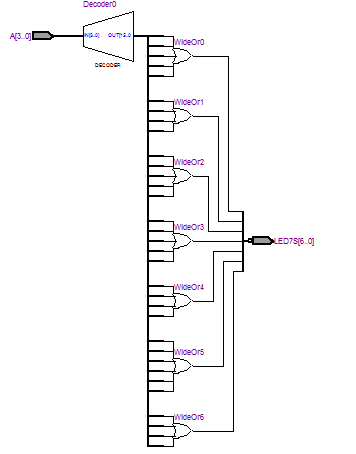

4、电路图

(二)8位加法器设计实验

1、实验内容

(1)实验目的

熟悉使用Quartus2的原理图输入方法设计简单组合单路,掌握层次化设计的方法,并通过8位全加器的设计把握文本和原理图输入方式设计的详细流程。

(2)实验原理

一个8位加法器可以由8个全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin 相接。

(3)实验任务

完成半加器和全加器的设计,包括用文本或原理图输入、编辑、综合、适配、仿真、实验系统的硬件测试,并将此全加器电路设置成一个元件符号入库。

2、Verilog程序

半加器 Verilog描述:

module h_adder(A,B,SO,CO);

input A,B;

output SO,CO;

assign SO=A^B;

assign CO=A&B;

endmodule

全加器Verilog描述:

module f_adder(ain,bin,cin,cout,sum);

output cout,sum;

input ain,bin,cin;

wire net1,net2,net3;

h_adder U1(ain,bin,net1,net2);

h_adder U2(.A(net1),.SO(sum),.B(cin),.CO(net3)); or U3(cout,net2,net3);

endmodule

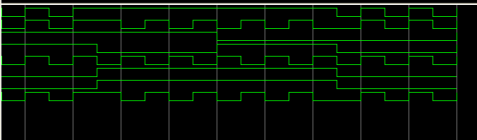

3、仿真图

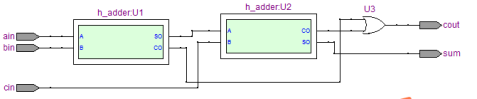

4、电路图

第二篇:实验报告

实 验 报 告