重庆理工大学

嵌入式体系结构课程总结

二级学院 计算机科学与工程学院

专 业 计算机科学与技术专业

班 级 37—2

学生姓名 张建英 学号 11103070231

教 师 刘政

时 间 2013.11.10

成 绩

前言:关于嵌入式部分总结

从技术角度定义嵌入式:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式系统分类:嵌入式微处理器(EMPU)、微控制器、DSP处理器、片上系统SOC。

嵌入式微处理器(EMPU):嵌入式微处理器的基础是计算机中的CPU,在应用中

将微处理器装配在专门设计的电板上,只保留与嵌入式应用有关的母板功能,这样可以大幅减小系统的体积和功耗。

微控制器:微控制器又叫单片机,顾名思义,就是将整个计算机系统集中到一块芯片中,与嵌入式微处理器相比,微控制器的最大特点是单片化。

DSP处理器:效率较高,指令执行速度也较高。

片上系统SOC:SOC就是在一个硅片上实现一个更为复杂的系统,SOC可以分为通用和专用两类。

ARM处理器有两种状态和七种模式:两种状态:ARM状态、Thumb状态;七种模式:用户模式、系统模式、管理模式、中止模式、未定义模式、中断模式、快速中断模式。

ARM状态:32位,处理器执行字方式的ARM指令,处理器在系统上电时默认为ARM状态。Thumb状态:16位,处理器执行半字方式的Thumb指令。

ARM处理器内部共有37个用户可访问的位寄存器,其中有6个人财产2位宽的状态寄存器目前只使用了其中12位。37个寄存器分别为:31个通用32位寄存器,6个状态寄存器。

RISC的结构特性:

1、具有大量的通用寄存器;

2、通过装载和保存结构使用独立的LOAD和STORE指令完成数据在寄存器与外部存储器之间的传送,处理器只处理寄存器中的数据,从而可以避免多次访问存储器;

3、寻址方式非常简单,所有转载、保存的地址都是由寄存器内容和指令域决定;

4、使用统一和固定长度的指令格式;

5、每一条数据处理指令都可以同时包含算数逻辑单元(ALU)的运算和移位处理,以实现对ALU和移位器的最大利用;

6、地址自动增加和自动减少的寻址方式优化了程序中的循环处理;

7、load/store指令可以批量传输数据,从而实现了最大数据吞吐量;

8、大多数ARM指令是可“条件执行”的,也就是说,只有当某个特定条件满足时指令才会被执行。

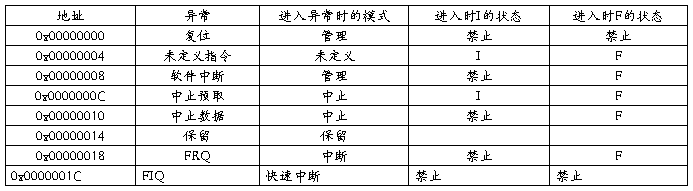

异常向量表:每一种处理器模式都有一个相关联的中断向量,当一个异常发生时,ARM将会改变模式,而程序计数器PC将会被强行指向异常向量。

异常向量表:

第一章系统控制和启动过程

1.1 相关功能的介绍

晶体振荡器:通过外接晶振或时钟为系统提供时钟信号;

复位:复位使ARM内核与外设部件进入一个确定的初始状态;

存储器映射控制:控制异常向量表的重新影射方式;

锁相环:将晶体振荡器输入的时钟倍频到一个合适的时钟频率;

VPB分频器:将内核失重与外设时钟分开的部件;

功率控制:使处理器空闲或者掉电,还能关闭指定的功能部件,以降低芯片功耗唤醒定时器。

1.2功能

1.3相应寄存器

1.4驱动程序

1.5示例代码

第二章 GPIO

2.1 GPIO简介

LPC2000系列ARM的GPIO特性:

1、可以独立控制每个GPIO口的方向(输入/输出模式);

2、可以独立设置每个GPIO的输出状态(高/低电平);

3、所有GPIO口在复位后默认为输入状态。

GPIO控制寄存器组描述:

2.2 GPIO寄存器

2.2.1

2.2.2

2.2.3

2.2.4

2.3

第三章向量中断及外部中断输入

3.1硬件结构

3.2功能

3.3相应寄存器

第四章定时器

4.1硬件结构

4.2功能

4.3相应寄存器

第五章SPI

5.1 SPI硬件结构

SPI总线系统是一种同步串行外设借口,允许MCU与各种外围设备已串行方式进行通信、数据交换。外围设备包括Flash、RAM、A/D、转换器、网络控制器、MCU等。SPI系统可直接与各个厂家生产的多种标准外围器件直接接口,一般使用4条线:串行时钟线SCK、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SSEI。

SPI的接口特性:1、具有2个完全独立的SPI控制器;

2、遵循同步串行接口(SPI)规范;

3、全双工数据通信;

4、可配置为SPI主机或从机;

5、最大数据位速率为外设时钟FPCLK的1/8。

5.2 SPI功能模块

有5个寄存器控制SPI功能模块,下面分别作简单的描述:

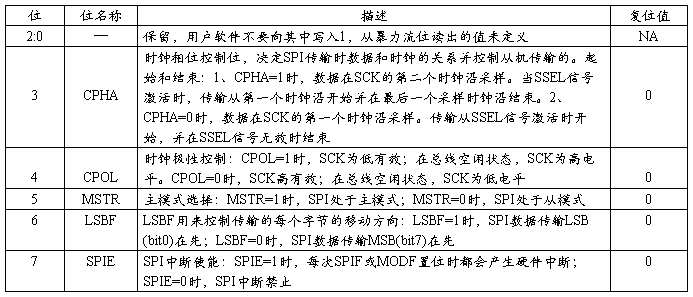

SPCR—SPI控制寄存器。包含一些可编程位来控制SPI功能模块。该寄存器必须在数据传输之前进行设定。

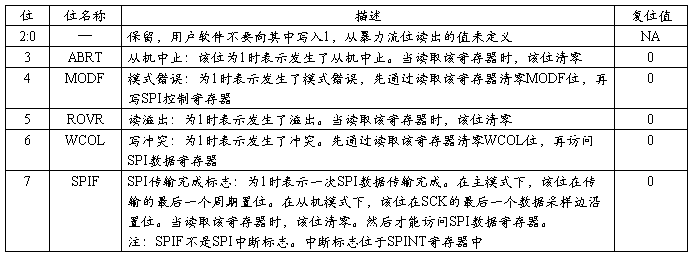

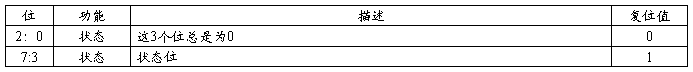

SPSR—SPI状态寄存器。只读的寄存器,用于监视SPI功能模块的状态,包括一些一般性功能和异常状况。该寄存器的主要用途是检测数据传输的完成,这可以通过判断SPIF位来实现,其他位用于指示异常状况。

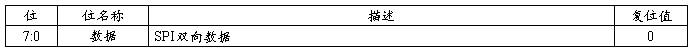

SPDR—SPI数据寄存器。用于发送和接收数据,在发送时向SPI数据寄存器写入数据。串行数据的发送和接收通过内部移位寄存器来实现。写数据时,数据寄存器和内部移位寄存器之间没有缓冲区,写SPDR会使数据直接进入内部一位寄存器,因此数据只能在一次数据发送完成之后写入该寄存器。读数据是带有缓冲区的,当传输结束时,接收到的数据转移到一个单字节的数据缓冲区,读SPI数据寄存器将返回读缓冲区的值。

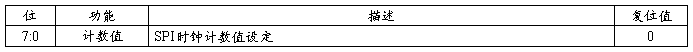

SPCCR—SPI时钟计数器寄存器,用于设置SPI时钟分频值。当SPI功能模块处于主模式时,SPCCR寄存器用于控制时钟速率,即SPI总线速率。该寄存器必须在数据传输之前设定。当SPI功能模块处于从模式时,该寄存器无效。

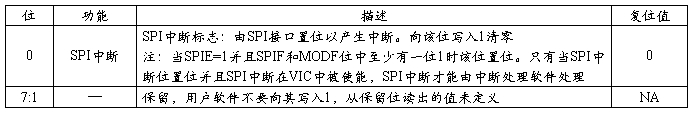

SPINT—SPI中断标志寄存器,该寄存器包含了SPI的中断标志位。

5.3 SPI寄存器描述

5.3.1 SPI控制寄存器(S0SPCR,0xE002 0000;S1SPCR,0xE003 0000)

示例代码:

SPI_SPCR= (0<<3) | //CPHA=0,数据在SCK的第一个跳变沿采样

(1<<4) | //CPOL=1,时钟为低有效

(1<<5) | //设置为主机

(0<<6) | //LSBF=0,数据传输MSB在先

(1<<7) | //SPI中断使能

5.3.2 SPI状态寄存器(S0SPSR,0xE002 0004;S1SPSR,0xE003 0004)

5.3.3 SPI数据寄存器(S0SPDR,0xE002 0008;S1SPDR,0xE003 0008)

示例代码:

SPI_SPDR= data; //发送数据

While((SPI_SPSR&0x80)==0); //等待SPI置位,即等待数据发送完毕

5.3.4 SPI时钟计数寄存器(S0SPCCR,0xE002 000C;S1SPCCR,0xE003 000C)

该寄存器控制主机SCK的频率,见下表。该寄存器的值必须为偶数,因此bit0必须为0,该寄存器的值还必须大于等于8。如果寄存器的值不符合上述条件,可能导致产生不可预测的动作。

频率公式如下:

Fspi=Fpclk/SPCCR

FPCLK=FCCLK/VPB,其中速率为CCLK/VPB除数,由VPBDIV寄存器的内容决定。

示例代码:

SPI_SPCCR=Fpclk/F_spi; //设置SPI时钟分频

5.3.5 SPI中断标志寄存器(S0SPINT,0xE002 001C;S1SPINT,0xE003 001C)

示例代码:

S0PINT=0x01; //清除SPI中断标志位

5.4驱动程序

5.4.1 SPI主机初始化示例

#define MSTR (1<<5)

#define CPOL (1<<4)

#define CPHA (1<<3)

#define LSBF (1<<6)

#define SPI_MODE (MSTR | CPOL)

Void MSpiIni(uint8 fdiv)

{

If(div<8) fdiv=8;

S0PCCR=fdiv&0xFE;

S0PCR=SPI_MODE;

}

5.4.2 SPI主机数据发送和接收示例

Uint8 MSendData(uint8 data)

{

IO0CLR=HC595_CS;

S0PDR=data;

While(0==(S0PSR&0x80));

IO0SET=HC595_CS;

Return(S0PDR);

}

5.4.3 SPI从机初始化示例

#define CPOL (1<<4)

#define CPHA (1<<3)

#define LSBF (1<<6)

#define SPI_MODE (MSTR | CPOL)

Void SSpiIni(void)

{

S0PCR=SPI_MODE;

}

5.4.4 SPI从机数据发送示例

Void SSendData(uint8 data)

{

S0PDR=data;

While((S0PSR&0x80)==0);

}

5.4.5 SPI从机数据接收示例

Uint8 SRcvData(void)

{

While((S0PSR&0x80)==0);

Return(S0PDR);

}

第六章 I2C

6.1 I2C总线简介

I2C BUS是NXP半导体公司推出的芯片间串行传输总线,它以2根连线实现了完善的双向数据传输,可以极方便地构成多机系统和外围器件扩展系统。I2C总线采用了器件地址的硬件设置方法,通过软件寻址完全避免了器件的片选线寻址方法,从而使硬件系统具有最简单而灵活的扩展方法。

I2C总线的2根线(串行数据SDA,串行时钟SCL)连接到总线上的任何一个器件,每个器件都应有一个唯一的地址,而且都可以作为一个发送器或接收器。此外,器件在执行数据传输时也可以被看作是主机或从机。

发送器:本次传送中发送数据(不包括地址和命令)到总线的器件。

接收器:本次传送中从总线接收数据(不包括地址和命令)的器件。

主机:初始化发送、产生时钟信号和终止发送的器件,它可以是发送器或接受器。主机通常是微控制器。

从机:被主机寻址的器件,它可以是发送器或接收器。

I2C总线是一个多主机的总线,即,总线上可以连接多个能控制总线的器件。当2个以上控制器件同时发动传输时,只能有一个控制器件能真正控制总线而成为主机,并使报文不被破坏,这个过程叫仲裁。与此同时,能同步多个控制器件所产生的时钟信号。

SDA和SDL都是双向线路。连接到总线的器件的输出级必须是漏极开路或集电极开路,都通过一个电流源或上拉电阻连接到正的电源电压,这样才能够实现“线与”功能。当总线空闲时,这2条线路都是高电平。

6.2 I2C总线的功能

1. I2C总线上的位传输。2C总线上的每传输一个数据位必须产生一个时钟脉冲。

数据的有效性:SDA线上的数据必须在时钟线SCL的高电平期间保持稳定,数据线的电平状态只有在SCL线的时钟信号为低电平时才能改变。在标准模式下,高低电平宽度不能小于4.7us。

起始信号和停止信号:起始信号,在SCL为高电平时,SDA从高电平向低电平切换。停止信号,在SCL为高电平时,SDA由低电平向高电平切换。

2. 数据传输

字节格式:发送到SDA线上的每个字节必须为8位。每次传输可以发送的字节数量不受限制。每个字节后必须跟一个应答位。首先传输的是数据的最高位(MSB)。

应答:相应的应答时钟脉冲由主机产生。在应答的时钟脉冲期间,发送器释放SDA线(高)。在应答的时钟脉冲期间,接收器必须将SDA线拉低,使它在这个时钟脉冲的高电平期间保持稳定的低电平。

3.仲裁与时钟同步

同步:时钟同步是通过各个能产生时钟的器件连接到SCL线上来实现的,上述的每个器件可能都有自己独立的时钟,各个时钟信号的频率、周期、相位和占空比可能都不相同。由于“线与”的结果,在SCL线上产生的实际时钟的低电平宽度由低电平持续时间最长的器件决定,而高电平宽度由高电平持续时间最短的器件决定。

仲裁:当总线空闲时,多个主机同时启动传输,可能会有不止一个主机检测到满足起始信号,而同时获得主机权,这样就要进行仲裁。当SCL线是高电平时,仲裁在SDA线发生,当其他主机发送低电平时,发送高电平的主机将丢失仲裁,因为总线上的电平与它自己的电平不同。

用时钟同步机制作为握手:期间可以快速接受数据字节,但可能需要更多时间保存接收到的字节或准备一个要发送的字节。此时,这个器件可以使SCL线保持低电平,迫使与之交换数据的器件进入等待状态,直到准备好下一字节的发送或接收。

4.传输协议

寻址字节:主机产生起始信号后,发送的第一个字节为寻址字节,该字节的头7位(高7位)为从机地址,最低位(LSB)决定了报文的方向,“0”表示主机写信息到从机,“1”表示主机读从机中的信息。当发送一个地址后,总线上的每个器件都将头7位与它的地址比较。如果一样,器件就会应答主机的寻址,至于是从机接收器还是从机发送器都有R/W位决定。从机地址由一个固定的和一个可编程的部分构成。

传输格式:主机产生起始信号后,发送一个寻址字节,收到应答后紧跟着的就是数据传输,数据传输一般由主机产生的停止位终止。主机发送数据到从机,寻址字节的“R/W”位为0,数据传输的方向不改变。主机读取从机中的数据,主机发送完寻址字节后,主机立即读取从机中的数据。复合格式,复合格式是上面两种格式的混合。

6.3 I2C寄存器描述

6.3.1 I2C控制置位寄存器(I2CONSET,0xE001 C000)

I2C接口中有2个寄存器,专门用来操作I2C控制寄存器———置位寄存器(I2CONSET)和清零寄存器(I2CONCLR)。

I2CONSET:可将控制寄存器中的某位置1,可读写;

I2CONCLR:可将控制寄存器中的某位清0,只写。

6.3.2 I2C控制清零寄存器(I2CONCLR,0xE001 C018)

6.3.3 I2C状态寄存器(I2STAT,0xE001 C004)

6.3.4 I2C数据寄存器(I2DAT,0xE001 C008)

6.3.5 I2C从地址寄存器(I2ADR,0xE001 C00C)

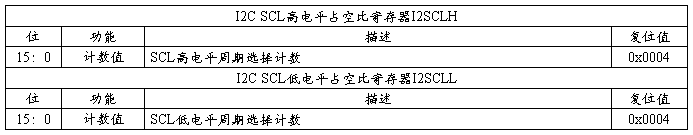

6.3.6 I2C SCL占空比寄存器(I2SCLH,0xE001 C010;I2SCLL,0xE001 C014)

6.4驱动程序

6.4.1主模式I2C初始化示例

Void I2C_Init(uint32 fi2c)

{

If(fi2c > 400000) fi2c = 400000;

PINSEL0 = (PINSEL0 & 0xFFFFFF0F) | 0x50 ;

I2SCLH = (Fpclk/fi2c + 1) / 2 ;

I2SCLL = (Fpclk/fi2c ) / 2 ;

I2CONCLR = 0x2C ;

I2CONSET = 0x40 ;

VICIntSelect = 0x00000000;

VICVectCntl0 = 0x29 ;

VICVectAddr0 = (int)IRQ_I2C ;

VICIntEnable = 0x0200 ;

}

6.4.2从模式I2C初始化示例

Void I2C_SlavInit(uint8 adr)

{

PINSEL0 = (PINSEL0 & 0xFFFFFF0F) | 0x50 ;

I2SADR= adr & 0xFE;

I2CONCLR = 0x28 ;

I2CONSET = 0x44 ;

VICIntSelect = 0x00000000;

VICVectCntl0 = 0x29 ;

VICVectAddr0 = (int)IRQ_I2C ;

VICIntEnable = 0x0200 ;

}

第七章 UART

7.1 UART硬件结构

LPC2000系列ARM7微控制器包含有2个符合16C550工业标准的异步串行口(UART):UART0和UART1。其中,UART0只提供TXD和RXD信号引脚,而UART1增加了一个调制解调器(Modem)接口。其余方面二者都是完全相同的。因此,下面对于二者相同的部分都是统一介绍的。

UART的特性:

1、16字节接收FIFO和16字节发送FIFO;

2、寄存器位置符合16C550工业标准;

3、接收器FIFO触发点可谓1、4、8和14字节;

4、内置波特率发生器;

5、UART1含有标准调制解调器接口信号。

7.2 UART结构

在UART0与UART1中,二者唯一的区别就是:UART1增加了一个Modem接口,其余都是相同的。

7.2.1 UART发送单元—UnTx(n=0、1,以n=0为例)

UnTx接收CPU(或从机)写入的数据,并将数据缓存到UARTn发送保持寄存器(UnTHR)中。发送移位寄存器(UnTSR)读取保持寄存器(UnTHR)中的数据,并将数据通过串行输出引脚TxDn发送出去。

7.2.2 UART接收单元—UnRx(n=0、1,以n=0为例)

UnRx监视串行输入线RxDn上的信号。UARTn Rx移位寄存器(UnRSR)通过RxDn接收有效字符。当UnRsR接收到一个有效字符时,它将该字符传送到UARTn接收缓冲寄存器FIFO中,等待CPU通过VPB总线进行访问。

UnTx和UnRx的状态信息保存在UnLSR中,UnTx和UnRx的控制信息保存在UnLCR中。

7.2.3 UART波特率发生器

UART0和UART1各自都有一个单独的波特率发生器,二者的功能都是相同的,以UART0的波特率发生器(U0BRG)为例进行说明。

U0BRG产生UART0 Tx模块所需要的时钟。UART0波特率发生器时钟源为VPB时钟(PCLK)。时钟源与U0DLL和U0DLM寄存器所定义的除数相除得到UART0 Tx模块所需的时钟,该时钟频率必须是波特率的16倍。

7.2.4 Modem接口

只有UART1含有Modem接口,Modem接口包含寄存器U1MCR和U1MSR,该接口负责一个Modem外设与UART1之间的握手。

7.2.5中断接口

UART0和UART1的中断接口包含中断使能寄存器(UnIER)和中断标识寄存器(UnIIR)。UART0的中断接口信号由U0Tx和U0Rx产生,UART1的中断接口信号除了由U1Tx和U1Rx产生外,还可以由Modem模块产生。

7.3 UART寄存器描述

UART有11个寄存器 :1.UART接收器缓存寄存器UnRBR;2.UART发送器保持寄存器UTHR;3.UART除数锁存寄存器;

7.4驱动程序

第八章 A/D

8.1硬件结构

8.2功能

8.3相应寄存器

8.4驱动程序

第九章 WDT

9.1硬件结构

9.2功能

9.3相应寄存器

9.4驱动程序

第十章 PWM

10.1硬件结构

10.2功能

10.3相应寄存器

10.4驱动程序