目录

项目测试总结报告. 1

1. 引言. 4

1.1 编写目的. 4

1.2 项目背景. 4

1.3 系统简介. 4

1.4 参考文档. 4

2. 测试设计简介. 4

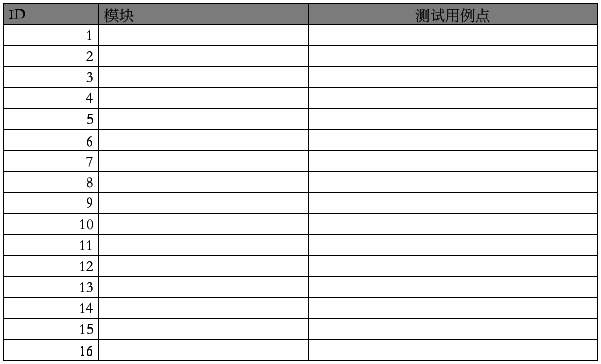

2.1 测试用例设计. 4

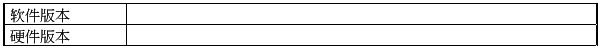

2.2 测试环境与配置. 5

2.3 测试方法和工具. 5

3. 测试结果及其分析. 5

3.1 测试执行情况与记录. 5

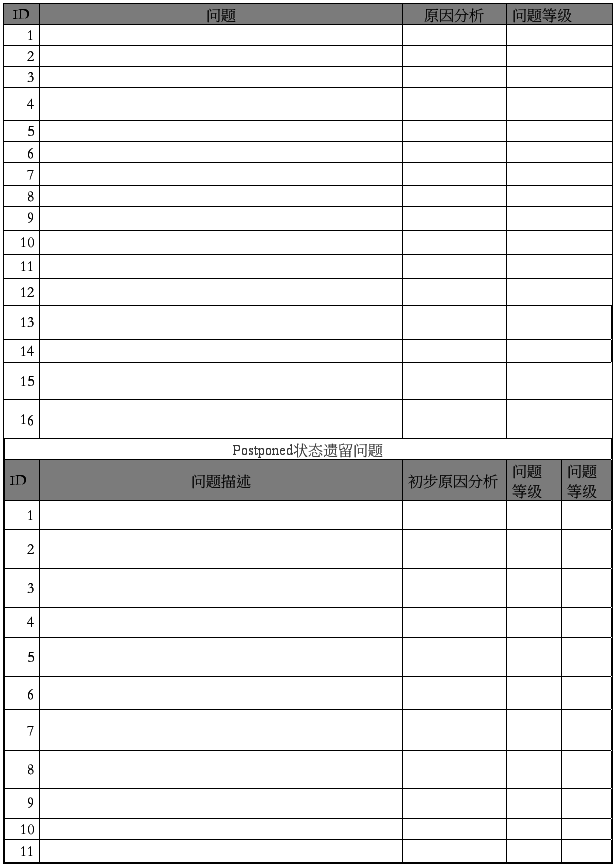

3.2 缺陷汇总. 6

3.3 测试覆盖. 6

4. 测试结论与建议. 6

4.1 结论:. 6

4.2 建议:. 8

1. 引言

1.1 编写目的

1) 本报告按照** 项目的技术要求反映**项目的测试结果

2) 阅读对象为 项目组所有成员及其相关授权的人员

1.2 项目背景

项目背景.

1.3 系统简介

测试目标描述如下:

配合开发部,让该项目最终产品达到产品级标准.

1.4 参考文档

2. 测试设计简介

2.1 测试用例设计

设计测试用例点 个;

2.2 测试环境与配置

2.3 测试方法和工具

手工测试.

3. 测试结果及其分析

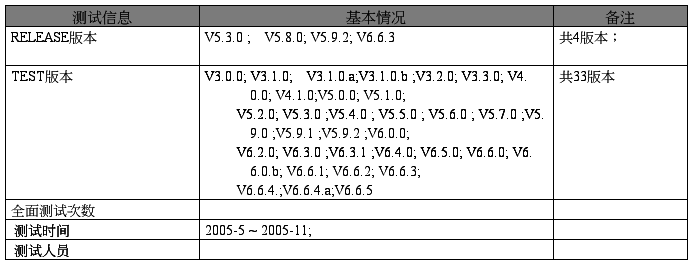

3.1 测试执行情况与记录

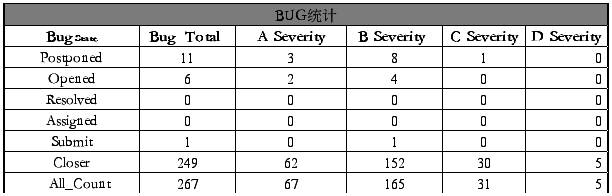

3.2 缺陷汇总

测试中发现A级问题: 67; B级问题 165; C级问题31 ;D级问题 5个;

3.3 测试覆盖

功能覆盖率: 100%;

4. 测试结论与建议

4.1 结论:

所有的功能已经实现;基本稳定;性能上达到了要求;

但还存在以下问题;

4.2 建议:

Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:Protel PCB技术参考

1.原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pin为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上: