实 验 报 告

…… …… 余下全文

计算机组成原理

实验报告

组长 汪 灿 学号 2013302530054 班号 信安二班

成员龚玉凤学号2013302530021 班号信安一班

时间 20##年5月

一. 试验目的

1. 融会贯通本实验课程所教授的知识,通过知识的综合应用,加深对CPU系统各模块的工作原理及相互联系的认识;

2. 学习设计和调试CPU的基本步骤和方法,基本熟悉现代EDA(Electronic Design Automation)技术设计电子系统的流程和方法;

3. 培养科学研究的独立工作能力,取得CPU设计与组装调试的实践和经验。

二. 实验任务

1. 熟悉开发工具、开发流程和实验平台;

2. 以实验教程(参考书1)第1章的通用寄存器组为基础,设计一个包含8个寄存器的通用寄存器组;

3. 以实验教程(参考书1)第2章的实验CPU为基础,或者完全按自己的设计,按要求(见下页)设计一个新的实验CPU;

4. 针对任务3,按要求(见后面)撰写实验报告。

三.设计方案

(一) 指令格式

指令系统说明:

1.有四个通用寄存器,R1,R2,R3,R4,源寄存器由SR表示,目的寄存器由DR表示,在编码中各占2bit。

2.运算指令编码第一位均是‘0’,方便译码。

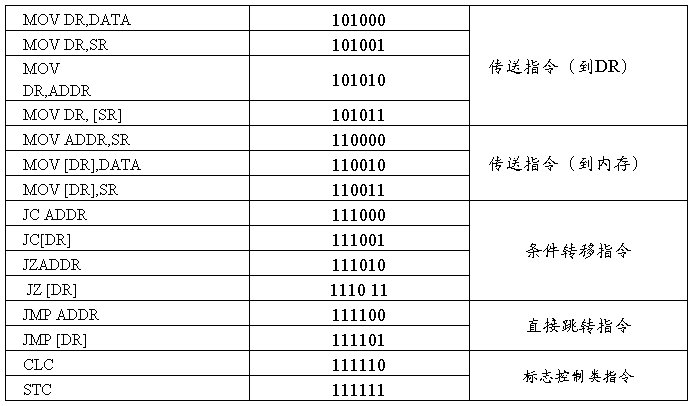

(二) 指令编码

(三) 指令流程

注: 红色流程为执行部分exe_unit所完成的功能;

粉色流程为MEM_unit部分所完成的功能;

…… …… 余下全文

精简8位CPU设计报告

07110401 于露

一、实验原理

RISC即精简指令集计算机(Reduced Instruction Set Computer)的缩写。RISC-CPU与一般的CPU相比,通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。本文对RISC-CPU的架构进行了分析,并使用VHDL语言设计了8位RISC-CPU IP软核。

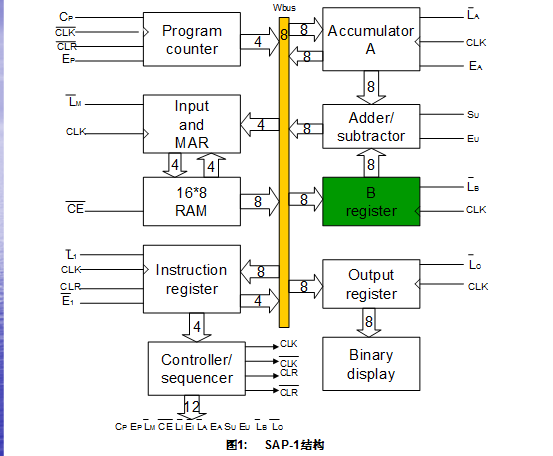

SAP-1 CPU部分:程序计数器、MAR、指令寄存器、控制器/序列发生器、累加器、加减法器、B寄存器、输出寄存器。

1.1 SAP-1 CPU及计算机的组成架构简介

1.程序计数器

它是一个4Bits的计数器,计数范围由0~15。主要功用是记录下每个执行的指令地址,并把这个地址传送至MAR寄存器存放。

2.输入与MAR(Memory Access Register)

这个方块应分成两个部分,一个是接受由“输入”部分输入到RAM内存的外部程序和数据,另一部分“MAR”是用来在CPU执行上述所加载的程序时,暂存下一个要执行的指令地址。

3.16×8 RAM

这个RAM有16个存储单元,每个单元为1字节,即8bits。所以这个RAM的地址总线是4bit,地址编码是由0000,0001,0010…1111,这个地址内容是由上述MAR传送过来,然后通过译码将地址存放的8位数据或指令输出至Wbus。

4.指令寄存器

属于CPU内的控制单元,主要是将在RAM的8位数据,通过Wbus后读入指令寄存器,然后再把数据一分为二,较高的4位属于指令部分,送至下一级的“控制器”,而较低的4位属于数据部分,将会被送至Wbus。

5.控制器/序列发生器

这个模块也是属于CPU内控制单元的一部分,这个控制器在程序执行时,负责送出整个计算机的时序信号CLK,而且会把指令寄存器送来的4位指令,解译成12位的控制信号,由这组控制信号指挥其它的功能方块,完成该指令的运作。由于使用VHDL语言设计整个SAR-1,依照语法的使用,这部分会被省略,而且不会影响整个CPU运作。

…… …… 余下全文

计算机组成实验报告

实验名称:单周期CPUVerilog实现

实验日期:2011.4.12-2011.4.19

实验人员:

同组者:

一、 主要实验内容

将已做好的各个模块进行模块合并,实现单周期CPU的各项指令,(注:由于此次设计只是利用verilog硬件编程语言实现具体功能,因此数据寄存器和存储器部件内的内容需由程序设计者自己给出,并不能从计算机中直接读取),下面对各个子模块进行简单的介绍。

二、各个子模块的简单介绍

此程序将数据通路(SingleDataLoad)设定为顶层模块,下面的模块包括:算术逻辑运算单元(ALU)、数据存储器(DataStore)、数据寄存器(Registers)、取指令部件(GetCode)、总控制器(Control),通过顶层模块对各个子模块的调用从而实现了整个单周期CPU。

1) 数据通路(SingleDataLoad):进行数据的运算、读取以及存储功能,通过总控制器产生的各个控制信号,进而实现对数据的各项操作。

2) 算术逻辑运算单元(ALU):数据通路调用此模块,根据得到的控制信号对输入数据进行处理,处理功能有:addu、add、or、subu、sub、sltu、slt等。

3) 数据存储器(DataStore):当WrEn控制信号为1时,此时就将输入数据存储到此存储器中,当WrEn为0时,则根据输入的地址,找到地址对应的单元将单元中的数据输出。

…… …… 余下全文

计算机硬件技术基础课程实验报告

实验题目:CPU性能测试

实验人班级: 学号: 姓名:

1、实验目的

了解CPU参数的含义,以及各个参数对CPU性能的影响

2、实验环境

①实验硬件环境(计算机的型号、基本配置)

②实验软件坏境(操作系统、测试软件等)

CPU-Z,是一款检测CPU使用程度最高的一款软件,它可以提供一些关於处理器的资讯,包含了制造厂及处理器名称,核心构造及封装技术,内部、外部频率,最大超频速度侦测,也可以查出处理器相关可使用的指令集。最新的1.5.5版加入了可侦测处理器的核心电压、L2快取汇流排频宽、Windows NT/2000环境下的双处理器模式侦测,及记忆体时脉(如CAS Latency, RAS to CAS, RAS Precharge)。

Everestultimate(原名AIDA32)一款强大测试软硬件系统信息的工具。它可以详细的测试PC每一个方面的信息。支持CPU、FPU基准测试,提供CPU Queen、CPU PhotoWorxx、CPU ZLib、CPU AES、FPU Julia、FPU Mande、FPU SinJulia基准测试模块,最新版支持三核心AMD Phenom、六核心Intel Dunnington Xeon处理器;

SuperPi cpu性能测试软件原理是计算圆周率小数点的位数SuperPi是一个测试CPU性能的计算软件;它的工作原理是计算圆周率小数点的位数.例如:SuperPi 100万位就是CPU计算到圆周率小数点后100万的意思,时间越短表示CPU的计算能力越强!

Fritz Chess Benchmark是一款国际象棋测试软件,是国际象棋软件Fritz自带的电脑棋力测试程序,由于支持多线程,而且它做的是大量科学计算,所有经常被用来测试电脑的科学运算能力。它通过穷举每一步策略来测试处理器的运算能力,而且它还支持多线程运算,是目前个人计算机方面最好的步法计算和预测软件。同时该软件还给出了一个基准参数,就是在P3 1.0G处理器下,其可以每秒运算48万步。

…… …… 余下全文

实验一类与对象

一、 实验目的

1、 掌握类的声明和使用。

2、 掌握类的声明和对象的声明。

3、 复习具有不同访问属性的成员的访问方式。

4、 观察构造函数和析构函数的执行过程。

5、 学习类的组合使用方法。

6、 使用VC++的debug调试功能观察程序流程,跟踪观察类的构造函数、析构函数、成员函数的执行顺序。

二、 实验任务

1、 声明一个CPU类,包含等级(rank)、频率(frequency)、电压(voltage)等属性,有两个公有成员函数run、stop。其中,rank为枚举类型CPU_Rank,声明为enum CPU_Rank{P1=1,P2,P3,P4,P5,P6,P7},frequency为单位是MHz的整型数,voltage为浮点型的电压值。观察构造函数和析构函数的调用顺序。

2、 声明一个简单的Computer类,有数据成员芯片(cpu)、内存(ram)、光驱(cdrom)等等,有两个公有成员函数run、stop。cpu为CPU类的一个对象,ram为RAM类的一个对象,cdrom为CDROM类的一个对象,声明并实现这个类。

3、 (选作)设计一个用于人事管理的People(人员)类。考虑到通用性,这里只抽象出所有类型人员都具有的属性:number(编号)、sex(性别)、birthday(出生日期)、id(身份证号)等等。其中“出生日期”声明为一个“日期”类内嵌子对象。用成员函数实现对人员信息的录入和显示。要求包括:构造函数和析构函数、拷贝构造函数、内联成员函数、组合。

…… …… 余下全文

.

实验报告

实验项目名称 超线程技术

所属课程名称 计算机操作系统

实验类型 检索型

实 验 日 期 20##-5-7

班 级 11 级信管班

学 号 20111111118

姓 名 ***

成 绩

经济信息管理及计算机应用系

…… …… 余下全文

数学与计算机学院 计算机组成原理 实验报告

年级 *****级 学号 ********** 姓名 ***** 成绩

专业网络工程 实验地点 主楼528 指导教师 何欣枫

实验项目 CPU指令译码器 实验日期 20##-12-5

一、实验目的

(1)理解指令译码器的作用和重要性。

(2)学习设计指令译码器。

二、实验原理

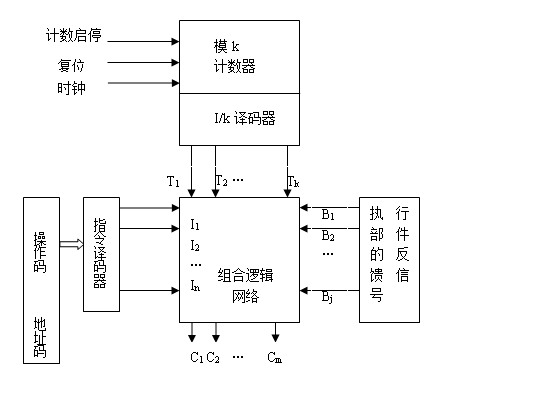

指令译码器是计算机控制器中最重要的部分。所谓组合逻辑控制器就是指指令译码电路是由组合逻辑实现的。

组合逻辑控制器又称硬连线控制器,是设计计算机的一种方法。这种控制器中的控制信号直接由各种类型的逻辑门和触发器等构成。这样,一旦控制部件构成后,除非重新设计和物理上对它重新连线,否则要想增加新的功能是不可能的。结构上这种缺陷使得硬连线控制器的设计和调试变得非常复杂而且代价很大。所以,硬连线控制器曾一度被微程序控制器所取代。但是随着新一代及其及VLSI技术的发展,这种控制器又得到了广泛重视,如RISC机广泛使用这种控制器。

图6-42是组合逻辑控制器的方框图。逻辑网络的输入信号来源有3个:①指令操作码译码器的输出In;②来自时序发生器的节拍电位信号Tk;③来自执行部件的反馈信号Bj。逻辑网络的输出信号就是微操作控制信号,用来对执行部件进行控制。

图6-42 组合逻辑控制器的结构方框图

组合逻辑控制器的基本原理可描述位:某一微操作控制信号Cm是指令操作码译码器的输出In、时序信号(节拍电位信号Tk)和状态条件信号Bj的逻辑函数。即

…… …… 余下全文