EDA课程设计报告

课题名称:交通信号灯的控制

姓名:吴曼

学号:1010910530

随着我国经济社会快速发展,城市机动车保有量迅速增长,在进行城市基础设施建设以改善中心城区的交通问题时,仍然存在道路体系未健全,功能未理顺,公共系统不发达等问题,交通矛盾突出。而我国交通灯使用定周期控制和各路口各自独立控制方法,在解决这些问题时效果并不是很好。

随着电子信息的发展,找到一种更为合理的控制方法尤为重要。目前,控制交通信号灯的方法有很多,这次课程设计利用FPGA作为核心芯片,设计交通信号指示系统。

一、任务分析

设计一个交通信号灯控制器,在一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯。要求主干道处于常允许通行的状态,支干道有车来时才允许通行。主、支干道均有车时,两者交替通行,主干道每次放行45秒,支干道每次放行25秒。在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡。

综合分析,需用状态机实现功能。

二.原理分析

1.1设计目的

学习DEA开发软件和QuartusII的使用方法,熟悉可编程逻辑器件的使用。

1.2设计说明

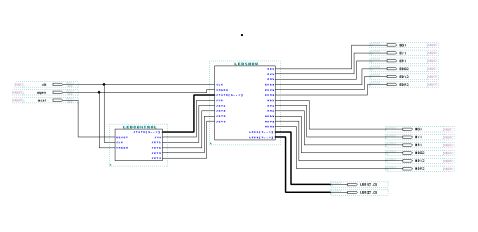

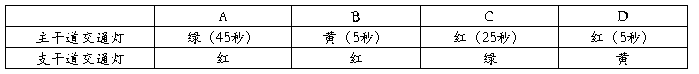

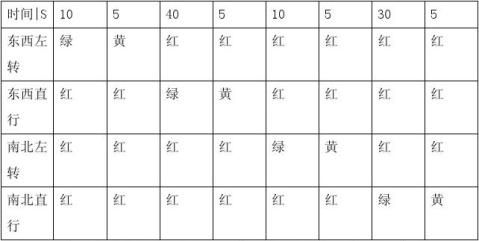

利用状态机的转换实现模拟交通灯的控制,状态表如下所示:

表1 交通信号灯的4种状态

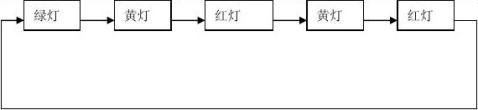

根据要求,可将各状态转换为状态转换图,如下所示:

图2:交通信号控制系统状态转换图

1.3模块分析

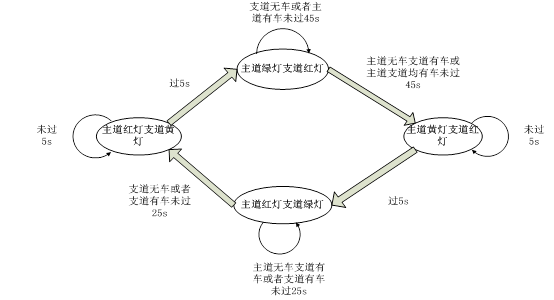

1.3.1分频模块

系统时钟为48MHZ,根据题目要求,利用分频器,将系统时钟分频为1HZ,分频器如下所示:

图3:分频器

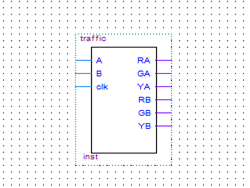

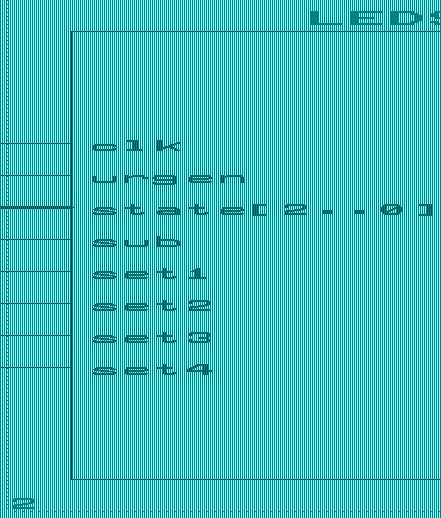

1.3.2状态转换电路

实现各个状态的转换,包含各个灯的计时器,当记满时间后,用于状态的变换。用两个按键分别控制两个输入A,B。A输入高电平时,代表主道有车,B输入高电平时,代表支道有车。RA,GA,YA分别控制主干道红绿黄灯,RB,GB,YB分别控制支干道红绿黄灯。

图3:状态机

一.程序清单

1.1分频模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fp is

port( clk :in std_logic;

fout:out std_logic);

end;

architecture one of fp is

signal full :std_logic;

begin

fpq: process(clk)

variable d :integer range 48000000 downto 0;

begin

if clk'event and clk ='1' then

if d= 48000000 then

d :=0;

full <= '1';

else d := d+1;

full <= '0';

end if;

end if;

end process fpq;

fpq2 :process(full)

variable d2 :std_logic;

begin

if full'event and full = '1' then

d2 := not d2;

if d2 ='1' then fout <= '1';

else fout<='0';

end if;

end if;

end process fpq2;

end;

1.2状态机及计时模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity traffic is

port(

A:in std_logic;

B:in std_logic;

clk:in std_logic;

RA,GA,YA:out std_logic;

RB,GB,YB:out std_logic

);

end;

architecture behav of traffic is

type states is(st0,st1,st2,st3);

signal current_state,next_state:states:=st0;

signal C,D,E:std_logic;

signal RAx,GAx,YAx,RBx,GBx,YBx:std_logic;

begin

reg:process(clk)begin

if(clk'event and clk ='1')then current_state<=next_state;

end if;

end process ;

COM1:process(current_state,A,B,C,D,E)begin

case current_state is

when st0=>if(B and (not A or C))='1' then next_state<=st1;

else next_state<=st0;

end if;

when st1=>if D='1' then next_state<=st2;

else next_state<=st1;

end if;

when st2=>if(B and (not (A and E)))='1' then next_state<=st2;

else next_state<=st3;

end if;

when st3=>if D='1' then next_state<=st0;

else next_state<=st3;

end if;

when others=>next_state<=st0;

end case;

end process;

COM2:process(current_state)

begin

Case current_state is

when st0=>RAx<='0';GAx<='1';YAx<='0';RBx<='1';GBx<='0';YBx<='0';

when st1=>RAx<='0';GAx<='0';YAx<='1';RBx<='1';GBx<='0';YBx<='0';

when st2=>RAx<='1';GAx<='0';YAx<='0';RBx<='0';GBx<='1';YBx<='0';

when st3=>RAx<='1';GAx<='0';YAx<='0';RBx<='0';GBx<='0';YBx<='1';

when others=>RAx<='0';GAx<='1';YAx<='0';RBx<='1';GBx<='0';YBx<='0';

end case;

end process;

G45:process(current_state,clk)

variable Q45:std_logic_vector(5 downto 0);

begin

if(current_state=st0)then

if(clk'event and clk='1')then

if Q45<"101101"then Q45:=Q45+'1';

else Q45:=(others=>'0');

end if;

end if;

if Q45="101101"then C<='1';

else C<='0';

end if;

else null;

end if;

end process;

R25:process(current_state,clk)

variable Q25:std_logic_vector(4 downto 0);

begin

if(current_state=st2)then

if(clk'event and clk='1')then

if Q25<"11001"then Q25:=Q25+'1';

else Q25:=(others=>'0');

end if;

end if;

if Q25="11001"then D<='1';

else D<='0';

end if;

else null;

end if;

end process;

Y5:process(current_state,clk)

variable Q5:std_logic_vector(2 downto 0);

begin

if((current_state=st1)or(current_state=st3))then

if(clk'event and clk='1')then

if Q5<"101" then Q5:=Q5+'1';

else Q5:=(others=>'0');

end if;

end if;

if Q5="101" then E<='1';

else E<='0';

end if;

else null;

end if;

end process;

Px:process(clk)begin

if(clk'event and clk='1')then

RA<=RAx;GA<=GAx;YA<=YAx;RB<=RBx;GB<=GBx;YB<=YBx;

end if;

end process;

end;

三.仿真波形

四.故障分析

五.心得体会

第二篇:EDA课程设计交通灯

目录

1绪论?????????????????2

1.1 课程设计说明???????????2

1.2 课程设计目的???????????2 2 系统分析与总体方案?????????2

2.1 系统分析?????????????2

2.2 设计思想?????????????3

2.3 设计的总体方案??????????3 3 硬件电路设计???????????4

3.1控制流程电路设计?????????4

3.2译码显示电路设计?????????6

4、程序仿真与分析??????????11

4.1 仿真结果????????????11

4.2 仿真结果分析??????????11 5 心得体会?????????????12 6 参考文献?????????????13 附录A、各模块连接图????????14

1、绪论

1.1课程设计说明

伴随着社会的发展以及人类生活水平的提高,汽车的数量在不断增加,交通事业得以蓬勃发展,而随之引起的安全问题已经不容忽视。EDA技术的发展和应用领域也在不断的扩大与深入,机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域的重要性日益突出。为了确保十字路口的行人和车辆顺利,畅通的通过,往往采用电子控制的交通信号来进行指挥。利用EDA技术设计交通灯来完成这个需求就显的更加迫切,同样也是非常的实用和合理。

1.2 课程设计目

a.掌握十字路口交通灯控制的设计原理,并能够运用VHDL编程语言编写出实验程序,进一步对所学的EDA知识进行掌握与实际应用。

b.学会在MAX+plus Ⅱ软件环境中仿真,熟悉软件的基本操作和运行环境。 c.锻炼自己获取信息的能力,以及能够独立自主的思考和解决问题的能力。

2、系统分析与总体方案

2.1系统分析

通过分析可以知道,所要设计的十字路口交通灯控制电路要能够使南北方向有左转、直行各三个灯(红、黄、绿),东西方向有左转、直行各三个灯(红、黄、绿),三个灯能够按顺序依次亮灭。而且要求绿灯亮转黄灯亮然后其他时间为红灯,红灯亮可以直接转绿灯(三种灯的循环顺序如图2.1所示)。还要求三种灯的点亮时间能够以倒计时的形式显示出来。可以用VHDL语言合理设计系统功能,使红黄绿灯的转换有一个准确的时间间隔和转换顺序。

图2.1三种灯的循环顺序

2.2 设计思想

1 时间脉冲可以直接赋予得到。

2 10s、5s、40s、30s定时信号用倒计时,计时起始信号由控制流程电路给出,每当计满所需时间,即向控制电路输出“时间到”的信号,并使计数器清零,由控制电路启、闭三色信号灯。

3 主控电路是核心,这是一个时序电路,其输入信号为东西、南北方向: 10s、5s、40s、30s定时信号,其输出状态控制相应的三色灯。

4 三种灯转换状态表:

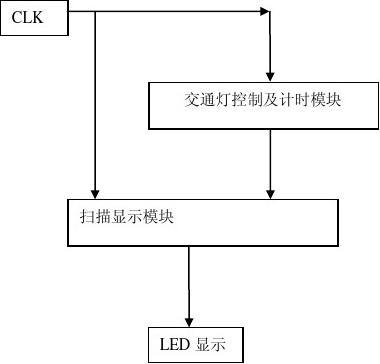

2.3 设计的总体方案

根据设计要求和系统所具有功能,并参考相关的文献资料经行方案设计画出如下所示的十字路口交通灯控制器系统框图,及为设计的总体方案,框图如下图

3.1所示:

图2.2 系统的框图

3、硬件电路设计

3.1控制器电路设计

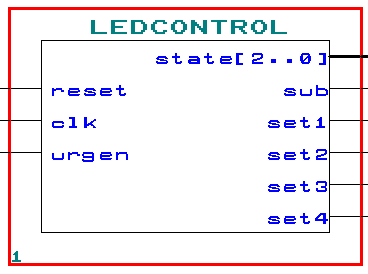

流程控制器的作用是根据计数器的计数值控制各方向上发光二极管的亮、灭,当计时时间到达,状态控制器就响应,自动跳转到下一个状态。此外,当检测到特殊情况(urgen =‘1’)发生时,无条件点亮红灯的二极管(急救灯按下urgen ='1',则东西南北都亮红灯,在这种状态下原来的状态必须保持,即东西南北方向定时时间保持不变。急救灯未按下或者按下后恢复,则继续计时(计时通过计数器count),同时恢复东西南北原来灯的状态)。具体实物模块如图:

图3.1控制器模块

程序实现如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ledcontrol IS

PORT(

reset,clk,urgen state : IN STD_LOGIC; : OUT STD_LOGIC_VECTOR(2 DOWNTO 0); : OUT STD_LOGIC); sub,set1,set2,set3,set4

END ledcontrol;

ARCHITECTURE a OF ledcontrol IS

SIGNAL count : STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL subtemp: STD_LOGIC;

BEGIN

sub<=subtemp AND (NOT clk) ; --将电平型信号变为脉冲型,即高电平时输出一个脉冲

statelabel:

PROCESS (reset,clk)

BEGIN

IF reset='1' THEN --――系统复位

count<="0000000";

state<="000";

set2<='1';set4<='1';

ELSIF clk'event AND clk='1' THEN

IF urgen='0' THEN count<=count+1;subtemp<='1';ELSE subtemp<='0';END IF;

--――经过脉冲电平变换后,使得正常状态时,正常减计数,紧急状态下停止计数

IF count=0 then

state<="000";set1<='1';set2<='1';set3<='1';set4<='1';

ELSIF count=10 then state<="001";set1<='1';

ELSIF count=15 THEN state<="010";set1<='1';set2<='1';

ELSIF count=55 THEN state<="011";set2<='1';

ELSIF count=60 THEN state<="100";set2<='1';set3<='1';

elsif count=70 THEN state<="101";set3<='1';

elsif count=75 THEN state<="110";set3<='1';set4<='1';

elsif count=105 THEN state<="111";set4<='1';

ELSIF count=110 THEN count<="0000000";

ELSE set1<='0'; set2<='0';set3<='0';set4<='0';END IF;

END IF; -- ――控制流程

END PROCESS statelabel;

END a;

3.2输出显示电路设计

根据状态控制器所控制的状态和计数器的计时时间,选择当前状态下的显示器,使显示器输出当前状态下的数码管亮、灭指令,其中数码管的显示采用动态扫描显示。具体实物模块如图:

图3.2译码显示电路模块

程序实现如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ledshow IS

PORT( clk,urgen state : IN : IN STD_LOGIC; STD_LOGIC_VECTOR(2 DOWNTO 0); : IN STD_LOGIC; : OUTsub,set1,set2,set3,set4 eg1,ey1,er1,edg2,edy2,edr2,ng1,ny1,nr1,ndg2,ndy2,ndr2 STD_LOGIC; led1,led2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ledshow;

ARCHITECTURE a OF ledshow IS

SIGNAL count1,count2,count3,count4 : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL setstate1,setstate2,setstate3,setstate4 : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL

etg1,ety1,etr1,edirr1,edirg1,ediry1,norg2,nory2,norr2,nordirg2,nordiry2,nordirr2 : STD_LOGIC;

BEGIN

led1<="00000000" WHEN urgen='1' AND clk='0' ELSE --显示东西向行和停

count1 WHEN state="000" ELSE count1 WHEN state="001" ELSE count2 WHEN state="010" ELSE count2 WHEN state="011" ELSE count2;

led2<="00000000" WHEN urgen='1' AND clk='0' ELSE

count3 WHEN state="000" ELSE

count3 WHEN state="001" ELSE

count3 WHEN state="010" ELSE

count3 WHEN state="011" ELSE

count3 WHEN state="100" ELSE

count3 WHEN state="101" ELSE

count4 WHEN state="110" ELSE

count4;

etg1<='1' WHEN state="000" AND urgen='0' ELSE '0';

ety1<='1' WHEN state="001" AND urgen='0' ELSE '0';

etr1<='1' WHEN state="010" or urgen='1' OR state="011" OR state="100" OR state="101" OR state="110" OR state="111" ELSE '0';

edirg1<='1' WHEN state="010" and urgen='0' ELSE '0';

ediry1<='1' WHEN state="011" and urgen='0' ELSE '0';

edirr1<='1' WHEN state="000" OR urgen='1' OR state="001" OR state="100" OR state="101" OR state="110" OR state="111" ELSE '0';

norg2<='1' WHEN state="100" AND urgen='0' ELSE '0';

nory2<='1' WHEN state="101" and urgen='0' ELSE '0';

norr2<='1' WHEN state="000" OR state="001" OR state="010" OR state="011" OR state="110" OR state="111" OR urgen='1' ELSE '0';

nordirg2<='1' WHEN state="110" AND urgen='0' ELSE '0';

nordiry2<='1' WHEN state="111" and urgen='0' ELSE '0';

nordirr2<='1' WHEN state="000" OR state="001" OR state="010" OR state="011" OR state="100" OR urgen='1' OR state="101" ELSE '0';

setstate1<= "00010000" WHEN state="000" ELSE

"00000101" WHEN state="001" ELSE "10010101" ;

setstate2<= "00010101" WHEN state="000" ELSE

--"00000101" WHEN state="001" ELSE "01000000" WHEN state="010" ELSE "00000101" WHEN state="011" ELSE "01010000" ;

setstate3<= "01100000" WHEN state="000" ELSE

"00010000" WHEN state="100" ELSE "00000101" WHEN state="101" ELSE "00110101" ;

setstate4<= "01110101" WHEN state="000" ELSE

"00110000" WHEN state="110" ELSE "00000101" ;

label4: ----南北直行

PROCESS (sub)

BEGIN

IF sub'event AND sub='1' THEN

IF set4='1' THEN

count4<=setstate4;

elsif count4(3 downto 0)="0000" then count4<=count4-7; ELSE count4<=count4-1;

END IF;

ndy2<=nordiry2; ndg2<=nordirg2; ndr2<=nordirr2;

END IF;

END PROCESS label4;

label3: ----南北左行

PROCESS (sub)

BEGIN

IF sub'event AND sub='1' THEN

IF set3='1' THEN

count3<=setstate3;

elsif count3(3 downto 0)="0000" then count3<=count3-7; ELSE count3<=count3-1;

END IF;

ng1<=norg2; ny1<=nory2; nr1<=norr2;

END IF;

END PROCESS label3;

label2: ---东西直行

PROCESS (sub)

BEGIN

IF sub'event AND sub='1' THEN

IF set2='1' THEN

count2<=setstate2;

elsif count2(3 downto 0)="0000" then count2<=count2-7; ELSE count2<=count2-1; END IF;

edg2<=edirg1; edy2<=ediry1; edr2<=edirr1;

END IF;

END PROCESS label2;

label1: --东西左行

PROCESS (sub)

BEGIN

IF sub'event AND sub='1' THEN

IF set1='1' THEN

count1<=setstate1;

elsif count1(3 downto 0)="0000" then count1<=count1-7; ELSE count1<=count1-1;

END IF;

eg1<=etg1; er1<=etr1; ey1<=ety1;

END IF;

END PROCESS label1;

END a;

4、程序仿真与分析

4.1 仿真结果

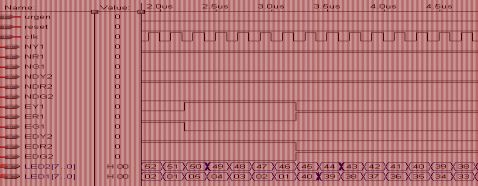

利用MAX+PLUS II软件对本程序进行编译,生成了可以进行仿真定时分析以及下载到可编程器件的相关文件。仿真结果如图5.1所示:

图5.1 仿真结果

4.2 仿真结果分析

通过设定clk值以及reset和urgen的初值,就可以得到如上所示的仿真波形图。由仿真波形图可以看出波形是由reset初值信号触发而显示出各个状态的。Urgen高电平信号输入时,所有交通灯都变为红灯状态(符合任务书的要求)。由仿真波形图还可以清楚的看出各时间段每个交通灯的状态。

要得到正确的仿真波形图就不许设定合适的时间信号clk值。如果clk值设置的太小则交通灯状态变化得太快无法分辨,如果clk值设置得太大则交通灯状态转换缓慢,效果不明显。其次,要设定reset初值,如果没有设定reset初值就不可能触发而得到仿真图。最后,就是要设置一Urgen高电平信号来检测紧急情况下的交通灯的状态。

5、心得体会

通过此次课程设计,使我对EDA程序设计有了进一步的学习,进一步的认识;在程序的设计,程序的调试方面都学到了很多东西,这是第一次编写EDA的大程序,很有成就感。在这几天课设的时间里,实验室的氛围对我们的影响很大,大家一起努力,这也是我们能完成课设的动力。在编程中出现问题时,一定要戒骄戒躁,脚踏实地,认真看书,仔细分析,仔细调试,就一定会发现错误,克服困难,我们也是这么做的,这在课设中十分重要。从这次的课程设计中,我真真正正的意识到,在以后的学习中,要理论联系实际,把我们所学的理论知识用到实际当中,学习EDA更是如此,程序只有在经常的写与读的过程中才能提高,这就是我在这次课程设计中的最大收获。

生活就是这样,汗水预示着结果也见证着收获。劳动是人类生存生活永恒不变的话题。虽然我这次做的课程设计不是非常的复杂,但在设计和仿真的过程中,我们也遇到了不少的困难,回首整个过程,却受益匪浅。

对我而言,知识上的收获重要,精神上的丰收更加可喜。让我知道了学无止境的道理。我们每一个人永远不能满足于现有的成就,人生就像在爬山,一座山峰的后面还有更高的山峰在等着你。挫折是一份财富,经历是一份拥有。这次课程设计必将成为我人生旅途上一个非常美好的回忆!

6 参考文献

[1] 阎石 主编,《数字电子技术基础》,高等教育出版社,1998

[2] 谭会生等主编,《EDA技术及应用》,西安电子科技大学出版社,2001

[3] 廖裕评等主编,《CPLD数字电路设计——使用MAX+plusⅡ入门篇》,清华大学出版社,2001

[4] 冯涛等主编,《可编程逻辑器件开发技术:MAX+plusⅡ入门与提高》,人民邮电出版社,2002

[5] 杨崇志,《特殊新型电子元件手册》,辽宁科学技术出版社,1999

[6] 彭介华,《电子技术课程设计指导》高等教育出版社.20xx年出版.

[7] Mark Zwolinski, Digital System Design with VHDL, 电子工业出版社,2002

[8] Alan B. Marcovitz Introduction to logic Design, 电子工业出版社,2002

附录A、各模块连接图