南京工程学院

自动化学院

实 验 报 告

课程名称电子设计自动化EDA技术

实验项目名称 EDA开发软件Max+plus II

或Quartus II

实验学生班级

实验学生姓名

同组学生姓名

实验时间

实验地点

实验成绩评定

指导教师签字

年 月 日

第二篇:《EDA技术及应用》实训报告

桂林电子科技大学信息科技学院

《EDA技术及应用》实训报告

学 号 1151100130

姓 名 龙舟

指导教师:梁勇

2013 年 7 月 8 日

实训题目:万年历

1 系统设计

1.1 设计要求

1.1.1 设计任务

设计一个数字日历电路

1.1.2 性能指标要求

⑴用Verilog HDL语言设计一个数字日历。

⑵数字日历能正确显示年、月、日、时、分和秒。

⑶通过开关分别控制对年、月、日或时、分、秒校对及自动切换、,并且

运用按钮对年、月、日或时、分、秒校对。

⑷通过按钮对数码管全部清零。

1.2 设计思路及设计框图

1.2.1设计思路

通过EDA课程的学习,可知运用Verilog HDL语言设计一个数字日历括计时器模块(jsq60、jsq24)、年月日模块(nyr2009)、控制模块(conr)、校时选择模块(mux_4)、显示选择模块(mux_16);然后将各个模块连接起来画成原理图再下载到实训仪上,调节开关及按钮来实现数字日历的功能

1.2.2总体设计框图

2 各个模块程序的设计

(1)设计一个分频器进行20MHz分频得到实训所需的1Hz的频率

分析:这是个20MHZ时钟的分频器,将原来EDA实训仪提供的频率为20MHZ的时钟转换成频率1HZ的时钟,然后输出到有需要的端口,触发模块起作用。

(2)分别设计一个能显示年月日和时分秒的程序

校准年月日和秒分时的原理图如下:

分析:①当k=0时,开关j1,j2,j3校秒时分然后将信号分别送到jsq24模块的jm(校秒)、jf(校分)、js(校时)。

②当k=1时,开关j1,j2,j3校年月日然后将信号分别送到nyr2009模块的jr(校日)、jy(校月)、jn(校年)。

计算年月日的模块如下:

分析:clrn是异步清除输入端,低电平有效;clk是时钟输入端,上升沿有效;jn、jy和jr分别是校年、校月、校日输入端;qn[15..0]、qy[7..0]、qr[7..0]分别是年、月、日的输出端。

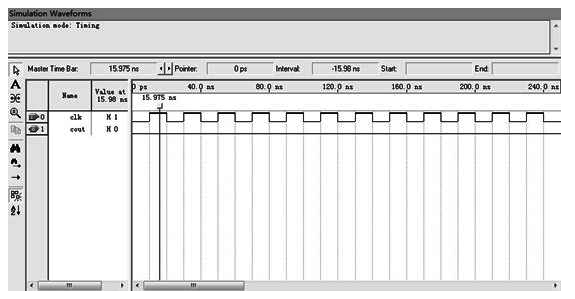

计时器模块如下:

分析: cln是异步清除输入端,低电平有效;clk是时钟输入端,上升沿有效;im、if和is分别是校秒、校分、校时输入端;qm[7..0]、qf[7..0]、qs[7..0]分别是年、月、日的输出端;cout是进位;

显示时分秒与年月历的模块如下:

分析:①当k=0时,把jsq24送来的时分秒的状态信号送到数码管显示。

②当k=1时,把nyr2009送来的年月日的状态信号送到数码管显示。

3 调试过程

在这次的实训中我选择了EDA课程中讲解过的万年历的设计,在其基础上添加了时间、日期自动切换一个拓展功能,通过运用Verilog HDL语言对程序进行设计,然后运用QuartusII9.0软件对各程序进行编译,看是否能通过,如有错误可以逐条对语句进行调试,当所有模块编译成功后就下载到EDA工具实验箱进行验证。

4 功能测试

4.1 测试仪器与设备

QuartusII9.0软件以及eda实训开发箱

4.2 性能指标测试

能够正常显示计时以及显示日期及其来回切换和自动切换。

4.3 误差分析(某些题目需要)

××××××××××××××××××××

5 实训心得体会

通过这两周的EDA实训,不仅更熟练的运用Verilog HDL语言在QuartusII9.0软件上的设计方法与步骤,还在参考资料后添加了一个日期,时间自动跳转模块拓展功能完成了数字日历电路的设计。在实训过程中,设计切换模块时,不能自动切换,后来在老师的指导下,在控制模块(contr)前面加一个分频器(clkgen)就可以实现8秒自动切换功能。从一开始接受课程任务,建立设计框图,再到网上查阅相关资料,确定电路图到最终制作成型,每一步都必须真诚付出。刚开始我是做的并不成功,不能实现切换功能。在多次检修之后,最终实现了课程设计作业的全部功能。将各个部分组成起来设计成为万年历功能。通过这次EDA实训我对数字逻辑电路也更加地了解,有了更直观的了解。

6 参考文献

例:[1] 谢自美.电子线路设计·实验·测试(第二版).武汉:华中科技大学出版社,2000

附录

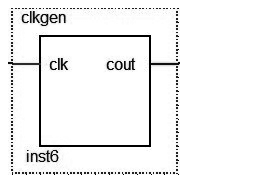

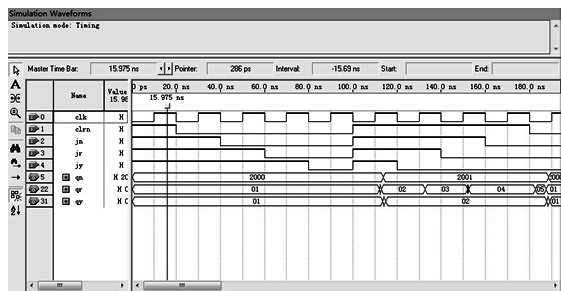

附录1:仿真波形图(部分模块)

Clkgen模块波形仿真图:

Cnt24模块波形仿真图:

Jishuqi模块波形仿真图:

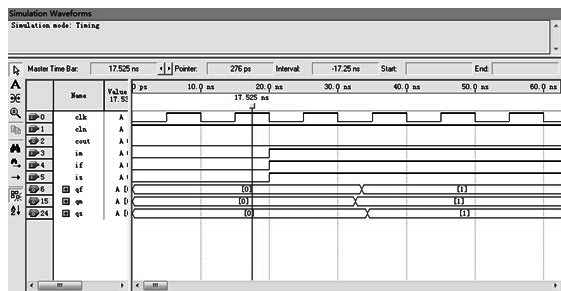

Mux_4模块波形仿真图:

Mux_16模块波形仿真图:

Nry2009模块波形仿真图:

附录2:程序清单

1、contr模块程序

module contr(clk,k1,k2,k);

input clk,k1,k2;

output reg k;

reg [3:0] qc;

reg rc;

always @(posedge clk)

begin qc=qc+1;

if (qc<8) rc=0;

else rc=1;

case({k1,k2})

0:k=rc;

1:k=0;

2:k=1;

3:k=rc;

endcase

end

endmodule

2、 mux_4模块程序

module mux_4(k,jm,jf,js,jr,jy,jn,j1,j2,j3);

input k,j1,j2,j3;

output reg jm,jf,js,jr,jy,jn;

always

begin

if(k==0) {jm,jf,js}={j1,j2,j3};

else {jr,jy,jn}={j1,j2,j3};

end

endmodule

3、clkgen模块程序

module clkgen(clk,cout);

input clk;

reg[24:0] q;

output reg cout;

always @(posedge clk)

begin

if(q==20000000-1) q=0;

else q=q+1;

if(q==20000000-1) cout=1;

else cout=0;

end

endmodule

4、 cnt60模块程序

module cnt60(clk,cln,j,q,cout);

input clk,cln,j;

output reg [7:0] q;

output reg cout;

always @(posedge clk^j or negedge cln)

begin

if(~cln)q=0;

else begin

if(q=='h59) q=0;

else q=q+1;

if(q[3:0]=='ha) begin

q[3:0]=0;q[7:4]=q[7:4]+1;end

if(q=='h59) cout=1;

else cout=0;end

end

endmodule

5、cnt24模块程序

module cnt24(clk,q,j,cln,cout);

input clk,cln,j;

output reg [7:0] q;

output reg cout;

always @(posedge clk^j or negedge cln)

begin

if(~cln) q=0;

else begin

if(q=='h23) q=0;

else q=q+1;

if(q[3:0]=='ha) begin

q[3:0]=0;q[7:4]=q[7:4]+1;end

if(q=='h23) cout=1;

else cout=0;end

end

endmodule

6、nyr2009模块程序

module nyr2009(clrn,clk,jn,jy,jr,qn,qy,qr);

input clrn,clk,jn,jy,jr;

output [15:0] qn;

output [7:0] qy,qr;

reg [15:0] qn;

reg [7:0] qy,qr;

reg clkn,clky;

reg [7:0] date;

reg clkn1,clkn2,clkn3;

initial begin clkn1=1;clkn2=1;clkn3=1;end

initial begin qn='h2000;qy=1;qr=1;end

always@(posedge (clk^jr) or negedge clrn)

begin

if(~clrn) qr=1;

else begin

if(qr==date) qr=1;

else qr=qr+1;

if(qr[3:0]=='ha) begin

qr[3:0]=0;qr[7:4]=qr[7:4]+1;end

if(qr==date) clky=1;

else clky=0;end

end

always@(posedge clky^jy or negedge clrn)

begin

if(~clrn ) qy=1;

else begin

if (qy=='h12) qy=1;

else qy=qy+1;

if(qy[3:0]=='ha) begin

qy[3:0]=0;qy[7:4]=qy[7:4]+1;end

if(qy=='h12) clkn = 1;

else clkn = 0;end

end

always

begin

case(qy)

'h01: date = 'h31;

'h02: begin

if((qn/4==0)&(qn/100 !=0)|(qn/400 ==0)) date='h29;

else date = 'h28;end

'h03: date = 'h31;

'h04: date = 'h30;

'h05: date = 'h31;

'h06: date = 'h30;

'h07: date = 'h31;

'h08: date = 'h31;

'h09: date = 'h30;

'h10: date = 'h31;

'h11: date = 'h30;

'h12: date = 'h31;

default :date='h30;

endcase

end

always @(posedge (clkn^jn) or negedge clrn )

begin

if (~clrn) qn[3:0]=0;

else begin if(qn[3:0]==9) qn[3:0]=0;

else qn[3:0]=qn[3:0]+1;

if(qn[3:0]==9) clkn1=0;

else clkn1=1;end

end

always @(posedge clkn1 or negedge clrn)

begin

if(~clrn) qn[7:4]=0;

else begin if (qn[7:4]==9) qn[7:4]=0;

else qn[7:4]=qn[7:4]+1;

if(qn[7:4]==9) clkn2=0;

else clkn2=1;end

end

always @(posedge clkn2 or negedge clrn)

begin

if(~clrn) qn[11:8]=0;

else begin if (qn[11:8]==9) qn[11:8]=0;

else qn[11:8]=qn[11:8]+1;

if(qn[7:4]==9) clkn3=0;

else clkn3=1;end

end

always @(posedge clkn3 or negedge clrn)

begin

if(~clrn) qn[15:12]=2;

else if (qn[15:12]==9) qn[15:12]=0;

else qn[15:12]=qn[15:12]+1;

end

endmodule

7、 mux_16模块程序

module mux_16(k,qm,qf,qs,qr,qy,qn,q);

input k;

input [7:0] qm,qf,qs,qr,qy;

input [15:0] qn;

output reg [31:0] q;

always

begin

if (k==0) begin

q[31:24]=0;

q[23:0]={qs,qf,qm};end

else q={qn,qy,qr};

end

endmodule