EDA技术及应用

实 验 报 告

实验四 数字频率计的设计

2015.4.28

实验四 数字频率计的设计

一、实验目的

1.掌握VHDL语言的基本结构。

2.掌握VHDL层次化的设计方法。

3.掌握VHDL基本逻辑电路的综合设计应用。

二、实验内容

设计并调试好一个8位十进制数字频率计。要求编写上述8位十进制数字频率计逻辑图中的各个模块的VHDL语言程序,并完成8位十进制数字频率计的顶层设计,然后利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

三、实验条件

1.计算机一台;

2.Max+PlusII和Quartus II开发工具软件;

3.EDA实验开发箱一台;

4.编程器件: EP3C55U48417

四、实验步骤

1.根据测频控制信号发生器的基本原理编写TESTCTL模块的VHDL程序,并对其进行编译和仿真,初步验证设计的正确性。

2.编写十进制计数器CNT10模块的VHDL程序,并对其进行编译和仿真,初步验证设计的正确性。

3.编写寄存器REG32B模块的VHDL程序,并对其进行编译和仿真,初步验证设计的正确性。

4.完成8位十进制数字频率计的顶层设计,并对其进行编译和仿真,初步验证设计的正确性。

5.利用开发工具软件,选择所用可编程逻辑器件,并对8位十进制数字频率计进行管脚配置。

6.通过下载电缆将编译后的*.pof文件下载到目标器件之中,并利用实验开发装置对其进行硬件验证。

五、实验原理

1.系统设计思路

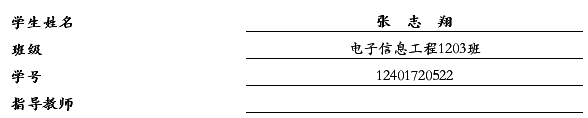

图1是8位十进制数字频率计的电路逻辑图,它由一个测频控制信号发生器TESTCTL、8个有时钟使能的十进制计数器CNT10、一个32位锁存器REG32B组成。以下分别叙述频率计各逻辑模块的功能与设计方法。

2.VHDL源程序

1)十进制计数器的源程序CNT10.VHD

--CNT10.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT10 IS

PORT(CLK,CLR,ENA:IN STD_LOGIC;

CQ:OUT INTEGER RANGE 0 TO 15;

CO:OUT STD_LOGIC);

END ENTITY CNT10;

ARCHITECTURE ART OF CNT10 IS

SIGNAL CQI:INTEGER RANGE 0 TO 15;

BEGIN

PROCESS(CLK,CLR,ENA)IS

BEGIN

IF CLR='1' THEN CQI<=0;

ELSIF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQI<9 THEN

CQI<=CQI+1;

ELSE

CQI<=0;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CQI)IS

BEGIN

IF CQI=9 THEN CO<='1';

ELSE

CO<='0';

END IF;

END PROCESS;

CQ<=CQI;

END ARCHITECTURE ART;

2)32位锁存器源程序REG32B.VHD

--REG32B.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32B IS

PORT(LOAD:IN STD_LOGIC;

DIN :IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END REG32B;

ARCHITECTURE ART OF REG32B IS

BEGIN

PROCESS(LOAD,DIN)IS

BEGIN

IF LOAD'EVENT AND LOAD='1' THEN

DOUT<=DIN;

END IF;

END PROCESS;

END ARCHITECTURE ART;

3)信号发生器源程序TESTCL.VHD

--TESTCTL.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TESTCTL IS

PORT(CLK:IN STD_LOGIC;

TSTEN:OUT STD_LOGIC;

CLR_CNT:OUT STD_LOGIC;

LOAD:OUT STD_LOGIC);

END ENTITY TESTCTL;

ARCHITECTURE ART OF TESTCTL IS

SIGNAL DIV2CLK : STD_LOGIC;

BEGIN

PROCESS(CLK)IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

DIV2CLK<=NOT DIV2CLK;

END IF;

END PROCESS;

PROCESS (CLK,DIV2CLK) IS

BEGIN

IF CLK='0' AND DIV2CLK='0' THEN

CLR_CNT<='1';

ELSE CLR_CNT<='0';

END IF;

END PROCESS;

LOAD<=NOT DIV2CLK;

TSTEN<=DIV2CLK;

END ARCHITECTURE ART;

4)CTRLS.VHD

--CTRLS.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CTRLS IS

PORT(CLK:IN STD_LOGIC;

SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END ENTITY CTRLS;

ARCHITECTURE ART OF CTRLS IS

SIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK)IS

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF CNT="111"THEN

CNT<="000";

ELSE

CNT<=CNT+'1';

END IF;

END IF;

END PROCESS;

SEL<=CNT;

END ARCHITECTURE ART;

5)DISPLAY.VHD

--DISPLAY.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY DISPLAY IS

PORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

--LEDW:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DISPLAY;

ARCHITECTURE ART OF DISPLAY IS

SIGNAL DATA:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

P1:PROCESS(SEL)IS

BEGIN

CASE SEL IS

WHEN "000"=>COM<="11111110";

WHEN "001"=>COM<="11111101";

WHEN "010"=>COM<="11111011";

WHEN "011"=>COM<="11110111";

WHEN "100"=>COM<="11101111";

WHEN "101"=>COM<="11011111";

WHEN "110"=>COM<="10111111";

WHEN "111"=>COM<="01111111";

WHEN OTHERS=>COM<="11111111";

END CASE;

END PROCESS P1;

--LEDW<=SEL;

P2:PROCESS(SEL)

BEGIN

CASE SEL IS

WHEN "000"=>DATA<=DATAIN(3 DOWNTO 0);

WHEN "001"=>DATA<=DATAIN(7 DOWNTO 4);

WHEN "010"=>DATA<=DATAIN(11 DOWNTO 8);

WHEN "011"=>DATA<=DATAIN(15 DOWNTO 12);

WHEN "100"=>DATA<=DATAIN(19 DOWNTO 16);

WHEN "101"=>DATA<=DATAIN(23 DOWNTO 20);

WHEN "110"=>DATA<=DATAIN(27 DOWNTO 24);

WHEN "111"=>DATA<=DATAIN(31 DOWNTO 28);

WHEN OTHERS=>DATA<="0000";

END CASE;

CASE DATA IS

WHEN "0000"=>SEG<="00111111"; --3FH

WHEN "0001"=>SEG<="00000110"; --06H

WHEN "0010"=>SEG<="01011011"; --5BH

WHEN "0011"=>SEG<="01001111"; --4FH

WHEN "0100"=>SEG<="01100110"; --66H

WHEN "0101"=>SEG<="01101101"; --6DH

WHEN "0110"=>SEG<="01111101"; --7DH

WHEN "0111"=>SEG<="00000111"; --07H

WHEN "1000"=>SEG<="01111111"; --7FH

WHEN "1001"=>SEG<="01101111"; --6FH

WHEN OTHERS=>SEG<="00000000"; --00H

END CASE;

END PROCESS P2;

END ARCHITECTURE ART;

6)CLKGEN.VHD

--CLKGEN.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CLKGEN IS

PORT(CLK_IN:IN STD_LOGIC;

RESET:IN STD_LOGIC;

CLK_OUT:OUT STD_LOGIC);

END ENTITY CLKGEN;

ARCHITECTURE ART OF CLKGEN IS

CONSTANT DIVIDE_PERIOD:INTEGER:=500000;

--CONSTANT DIVIDE_PERIOD:INTEGER:=20;

BEGIN

PROCESS(CLK_IN,RESET)IS

VARIABLE CNT:INTEGER RANGE 0 TO 499999;

--VARIABLE CNT:INTEGER RANGE 0 TO 19;

BEGIN

IF(RESET='1')THEN

CNT:=0;

CLK_OUT<='0';

ELSIF RISING_EDGE(CLK_IN)THEN

IF(CNT<(DIVIDE_PERIOD/2))THEN

CLK_OUT<='1';

CNT:=CNT+1;

ELSIF(CNT<(DIVIDE_PERIOD-1))THEN

CLK_OUT<='0';

CNT:=CNT+1;

ELSE

CNT:=0;

END IF;

END IF;

END PROCESS DIVIDE_CLK;

END ARCHITECTURE ART;

7) FREQ.VHD

--FREQ.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FREQ IS

PORT(FSIN: IN STD_LOGIC;--5ns\10ns\5ns

CLK: IN STD_LOGIC;--500ns

CLK2:IN STD_LOGIC;

RESET: IN STD_LOGIC;

SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY FREQ;

ARCHITECTURE ART OF FREQ IS

--CNT10

COMPONENT CNT10 IS

PORT(CLK, CLR, ENA: IN STD_LOGIC;

CQ: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO: OUT STD_LOGIC);

END COMPONENT CNT10;

--REG32B

COMPONENT REG32B IS

PORT(LOAD: IN STD_LOGIC;

DIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT: OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END COMPONENT REG32B;

--TESTCTL

COMPONENT TESTCTL IS

PORT(CLK: IN STD_LOGIC;

TSTEN: OUT STD_LOGIC;

CLR_CNT: OUT STD_LOGIC;

LOAD: OUT STD_LOGIC);

END COMPONENT TESTCTL;

--CLKGEN

COMPONENT CLKGEN IS

PORT(CLK_IN: IN STD_LOGIC;

RESET: IN STD_LOGIC;

CLK_OUT: OUT STD_LOGIC );

END COMPONENT CLKGEN;

--CTRLS

COMPONENT CTRLS IS

PORT(CLK: IN STD_LOGIC;

SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT CTRLS;

--DISPLAY

COMPONENT DISPLAY IS

PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT DISPLAY;

SIGNAL SE,SC,SL,CLK1:STD_LOGIC;

SIGNAL S0,S1,S2,S3,S4,S5,S6,S7,S8:STD_LOGIC;

SIGNAL SD,DOUT:STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL SEL:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

U0:CLKGEN PORT MAP(CLK,RESET,CLK1);

U1:TESTCTL PORT MAP(CLK=>CLK1,TSTEN=>SE, CLR_CNT=>SC, LOAD=>SL);

U2:CNT10 PORT MAP(CLK=>FSIN, CLR=>SC, ENA=>SE, CQ=>SD(3 DOWNTO 0),CO=>S1);

U3:CNT10 PORT MAP(CLK=>S1, CLR=>SC, ENA=>SE, CQ=>SD(7 DOWNTO 4),CO=>S2);

U4:CNT10 PORT MAP(S2, SC, SE, SD(11 DOWNTO 8),S3);

U5:CNT10 PORT MAP(S3, SC, SE, SD(15 DOWNTO 12),S4);

U6:CNT10 PORT MAP(S4, SC, SE, SD(19 DOWNTO 16),S5);

U7:CNT10 PORT MAP(S5, SC, SE, SD(23 DOWNTO 20),S6);

U8:CNT10 PORT MAP(S6, SC, SE, SD(27 DOWNTO 24),S7);

U9:CNT10 PORT MAP(S7, SC, SE, SD(31 DOWNTO 28),S8);

U10:REG32B PORT MAP(LOAD=>SL, DIN=>SD, DOUT=>DOUT);

U11:CTRLS PORT MAP(CLK2,SEL);

U12:DISPLAY PORT MAP(SEL,DOUT,COM(7 DOWNTO 0),SEG(7 DOWNTO 0));

END ARCHITECTURE ART;

3.仿真波形设置

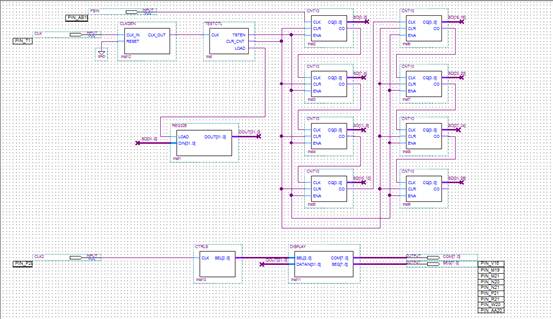

1.CNT10仿真结果如下:

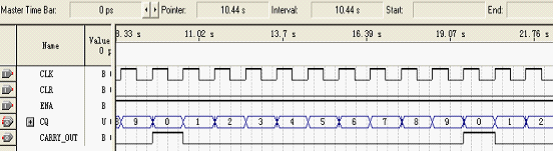

2.FREQ的仿真结果

4.逻辑综合验证

5.硬件逻辑验证

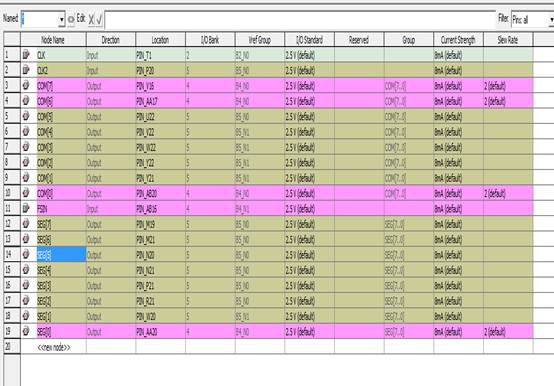

1)引脚锁定图

管脚锁定后,重新再编译一次,再进行硬件下载。(如果安装硬件驱动,要先进行驱动安装,安装好后,在进行硬件下载)

2)硬件验证图

六.实验总结

很好地巩固了我们学过的专业知识,使我对数字系统结构也有了更进一步的了解和认识,同时对数据库软件、EDA技术、VHDL 等系列知识都有了一定的了解。使用EDA技术开发页面的能力也有了很大提高。