西安交通大学数电实验报告

——四位智力抢答器

日期:20##年6月15日

目录

一.实验目的... 4

二.项目设计概要... 4

1. 设计实现的目标... 4

2. 整体设计概述... 4

3. 项目设计特点... 4

三.系统设计方案... 5

四.测试结果及分析... 9

1. 模拟仿真测试方案:... 9

2. 抢答鉴别模块仿真测试波形... 9

3. 加分电路模拟仿真测试波形图... 9

4. 计时电路模拟仿真测试波形图... 10

六.项目总结... 11

七.结束语... 11

一.实验目的

电子技术专题实验是对“数字逻辑”课程内容的全面、系统的总结、巩固和提高的一项课程实践活动。根据数字逻辑的特点,选择相应的题目,在老师的指导下,由学生独立完成。目的是通过实验使学生掌握数字逻辑电路设计的基本方法和技巧,正确运用QuartusⅡ软件及实验室多功能学习机硬件平台,完成所选题目的设计任务,并掌握数字逻辑电路测试的基本方法,训练学生的动手能力和思维方法。通过实验,一方面提高运用数字逻辑电路解决实际问题的能力,另一方面使学生更深入的理解所学知识,为以后的计算机硬件课程的学习奠定良好的基础。

二.项目设计概要

1. 设计实现的目标

(1) 设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(2) 电路具有第一抢答信号的鉴别和锁存功能。

(3) 设置计分电路。

(4) 设置犯规电路。

2. 整体设计概述

整个电子表分为三个主功能模块:抢答鉴别模块QDJB;抢答计时模块JSQ;抢答计分模块JFQ。对于需显示的信息,需增加或外接译码器,进行显示译码。考虑到FPGA/CPLD的可用接口及一般EDA实验开发系统提供的输出显示资源的限制,这里我们将组别显示和计时显示的译码器内设,而将各组的计分显示的译码器外接。

3. 项目设计特点

我们在项目设计过程中采用模块化设计思想,事先制定了模块间的接口方案,使得整个系统的组合变得十分灵活。由于我们在设计时为电子钟和秒表模块中都加入了显示电路,总控模块可分别与之连接组成一个分系统,便于调试。在最终整合时,我们也只需要将两个模块中的显示电路合二为一即可。

三.系统设计方案

电路模块的设计:

(1) 抢答模块设计:

抢答器,有A,B,C,D四个输入分别代表四个要抢答的组。CLR信号代表清零信号。清除后表示重新开始新一轮抢答。ZF信号表示主持人信号,表示是否开始抢答。Clk为时钟信号,表示检测是否有人抢答的周期。抢答器用四个上升沿D触发器,并将Q端输出信号送给A1,B1,C1,D1表示四个小组的抢答结果。ALRET信号表示抢答违规。采用四输入或门检测是否有输出信号,若有输出信号,则将clk置为高位不再检测输入。将CLR接入D触发器的清零端,将所有输出清零。检测主持人信号与输出信号是否同时为高,若都为高则表示有人抢答违规。

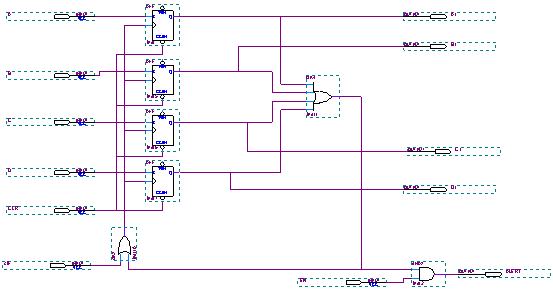

抢答器电路图如下:

(2)加分电路

加分器有RST输入,表示该组加分结束可以进行下一轮加分。ADD输入表示给该组加一分。CHOS[3..0]采用总线输入,表示要加分的组别。将CHOS[3..0]与抢答器的输出相接,某组抢答成功,并答题正确时给该组加一分。加分器共32个输出,从A1[3..0]到D2[3..0]分别用两位十进制数字表示各个小组的当前分数。

加分电路代码:

--JFQ.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY JFQ IS

PORT(RST: IN STD_LOGIC;

ADD: IN STD_LOGIC;

CHOS: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

AA2,AA1,AA0,BB2,BB1,BB0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CC2,CC1,CC0,DD2,DD1,DD0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY JFQ ;

ARCHITECTURE ART OF JFQ IS

BEGIN

PROCESS(RST,ADD,CHOS) IS

VARIABLE POINTS_A2,POINTS_A1: STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE POINTS_B2,POINTS_B1: STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE POINTS_C2,POINTS_C1: STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE POINTS_D2,POINTS_D1: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF (ADD'EVENT AND ADD='1') THEN

IF RST='1' THEN

POINTS_A2:="0001"; POINTS_A1:="0000";

POINTS_B2:="0001"; POINTS_B1:="0000";

POINTS_C2:="0001"; POINTS_C1:="0000";

POINTS_D2:="0001"; POINTS_D1:="0000";

ELSIF CHOS="0001" THEN

IF POINTS_A1="1001" THEN

POINTS_A1:="0000";

IF POINTS_A2="1001" THEN

POINTS_A2:="0000";

ELSE

POINTS_A2:=POINTS_A2+'1';

END IF;

ELSE

POINTS_A1:=POINTS_A1+'1';

END IF;

ELSIF CHOS="0010" THEN

IF POINTS_B1="1001" THEN

POINTS_B1:="0000";

IF POINTS_B2="1001" THEN

POINTS_B2:="0000";

ELSE

POINTS_B2:=POINTS_B2+'1';

END IF;

ELSE

POINTS_B1:=POINTS_B1+'1';

END IF;

ELSIF CHOS="0100" THEN

IF POINTS_C1="1001" THEN

POINTS_C1:="0000";

IF POINTS_C2="1001" THEN

POINTS_C2:="0000";

ELSE

POINTS_C2:=POINTS_C2+'1';

END IF;

ELSE

POINTS_C1:=POINTS_C1+'1';

END IF;

ELSIF CHOS="1000" THEN

IF POINTS_D1="1001" THEN

POINTS_D1:="0000";

IF POINTS_D2="1001" THEN

POINTS_D2:="0000";

ELSE

POINTS_D2:=POINTS_D2+'1';

END IF;

ELSE

POINTS_D1:=POINTS_D1+'1';

END IF;

END IF;

END IF;

AA2<=POINTS_A2; AA1<=POINTS_A1; AA0<="0000";

BB2<=POINTS_B2; BB1<=POINTS_B1; BB0<="0000";

CC2<=POINTS_C2; CC1<=POINTS_C1; CC0<="0000";

DD2<=POINTS_D2; DD1<=POINTS_D1; DD0<="0000";

END PROCESS;

END ARCHITECTURE ART;

(2) 计时器模块:

计时器LCR为清零信号,与抢答器的清零信号接同一输入,TA,TB为时间设置信号,可以自主设计时间,LOD为装载信号,装载TA,TB中的值给计时器,重新设置计时时间。CLK为时钟信号,接1HZ的输入信号来计时。

计时器代码:

--JSQ.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY JSQ IS

PORT(CLR,LDN,EN,CLK: IN STD_LOGIC;

TA,TB: IN STD_LOGIC;

QA: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

QB: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY JSQ;

ARCHITECTURE ART OF JSQ IS

SIGNAL DA: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL DB: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(TA,TB,CLR) IS

BEGIN

IF CLR='1' THEN

DA<="0000";

DB<="0000";

ELSE

IF TA='1' THEN

DA<=DA+'1' ;

END IF;

IF TB='1' THEN

DB<=DB+'1';

END IF;

END IF;

END PROCESS;

PROCESS(CLK) IS

VARIABLE TMPA: STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE TMPB: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF CLR='1' THEN TMPA:="0000"; TMPB:="0110";

ELSIF CLK'EVENT AND CLK='1' THEN

IF LDN='1' THEN TMPA:=DA; TMPB:=DB;

ELSIF EN='1' THEN

IF TMPA="0000" THEN

TMPA:="1001";

IF TMPB="0000" THEN TMPB:="0110";

ELSE TMPB:=TMPB-1;

END IF;

ELSE TMPA:=TMPA-1;

END IF;

END IF;

END IF;

QA<=TMPA; QB<=TMPB;

END PROCESS;

END ARCHITECTURE A

四.测试结果及分析

1. 模拟仿真测试方案:

将计时器,抢答鉴别器,加分器分别进行波形仿真测试,在对各个模块测试时与其他模块相关的输入信号可自行设置,如加分模块测试时CHOS[3..0]信号可设置为1000或0100。在设置输入信号时注意对输入信号进行限定。并尽可能多的测试不同情况下的输出。

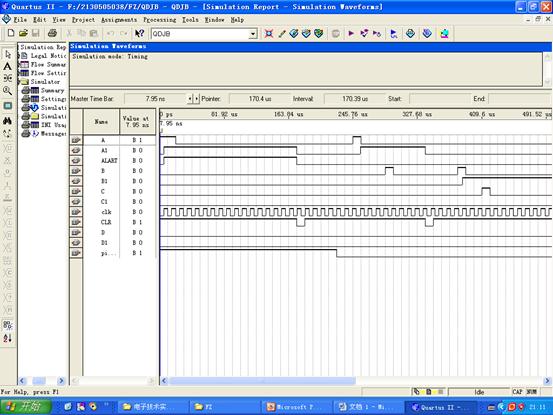

2. 抢答鉴别模块仿真测试波形

如图将输入设置为A抢答,主持人信号不允许抢答,观察输出波形为A1灯亮,警报灯亮,设置清零信号,设置信号为A先抢答,B后抢答,主持人信号设置为允许抢答,观察输出为A1灯亮。

3. 加分电路模拟仿真测试波形图

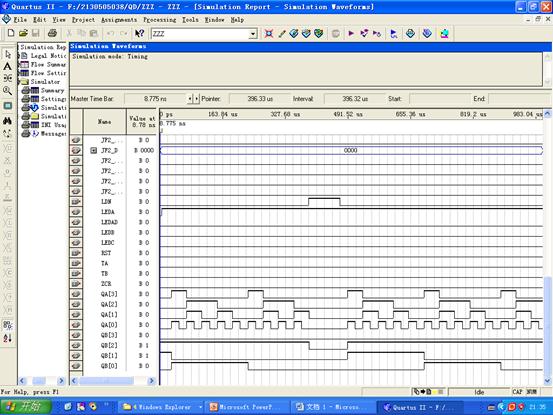

先将CHOS[3...1]信号设置为1000,ADD信号输入两次高,观察输出信号为A[3…0]的值为2。再将CHOS设置成0100,ADD信号设置两次高,观察B[3…0]变为2。

4. 计时电路模拟仿真测试波形图

给时钟信号接入周期信号观察输出,可得到输入波形输出波形为计时波形。再将TA,TB送零信号,加装载信号,输出为0 0.

六.项目总结

这次项目刚开始想的比较简单,没有考虑抢答时前一个人抢了之后后一个人按键时不能再有输出,导致整个抢答模块出错。整个项目的设计实现难度较大,设计过程比较顺利,并完成了预期的设计任务。毕竟我们只是学过一些比较基础的数字逻辑理论知识,能力有限,虽然整个模块经过精心设计和调试,其中仍难免存在一些不足之处。

七.结束语

数字电子技术是一门理论与实践密切相关的学科,如果光靠理论,我们就会学的头疼,如果借助实验,效果就不一样了,特别是数字电子技术实验,能让我们自己去验证一下书上的理论,自己去设计,这有利于培养我们的实际设计能力和动手能力。 通过数字电子技术实验, 我们不仅仅是做了几个实验,不仅要学会实验技术,更应当掌握实验方法,即用实验检验理论的方法,寻求物理量之间相互关系的方法,寻求最佳方案的方法等等,掌握这些方法比做了几个实验更为重要。 在数字电子技术实验中,我们可以根据所给的实验仪器、实验原理和一些条件要求,设计实验方案、实验步骤,画出实验电路图,然后进行测量,得出结果。