《sopc》课程报告之二

《基于FFPGA的图像压缩传输与解码系统》技术报告

院系:电子工程学院微电子学系

小组成员:郭从林 朱潮勇 杨欢 程亭

班级:电路1103班

组长:郭从林

学号:05116093

日期:20##年11月3日

《基于FFPGA的图像压缩传输与解码系统》功能定义与开发计划

摘要

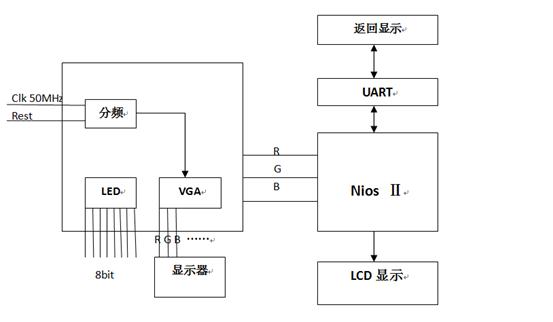

本文介绍了基于SOPC的通用嵌入式图像处理系统的实现方法,其中叙述了SOPC及NIOS ii 嵌入式处理器的特点和使用。分别具体说明了系统的硬件结构设计和图像处理算法的流程及软件实现,采用此系统可以大大简化图像处理系统的硬件和软件设计,优化系统设计。

关键字:SOPC(可编程片上系统);嵌入式处理器;静止图像压缩

一、 引言

1)随着计算机和多媒体技术的发展,图像等多媒体信源的传输处理显得日益重要,各种图像压缩处理的标准、协议也相继出现,其中 JPEG 静止图像压缩编码是图像压缩的一项重要技术,也是图像压缩的一个基本指标。

可编程片上系统 SOPC(System on a Programmable Chip)将处理器、存储器、I/O 等系统模块集成到单片 FPGA,完成系统的功能设计,使整个系统设计更加灵活,可扩充,可裁减,并且实现了软硬件的可编程,因此本系统采用 NiosⅡ嵌入式处理器实现一个通用嵌入式图像处理系统。

2) 通过UART传输图像的压缩信息,在sopc中解压并传输到VGA显示器显示

3)实现图像压缩传输,解压缩,显示。

二、 功能定义

功能:定义所开发项目软件与硬件功能;

硬件设计部分

1.使用FPGA普通端口作为GPIO使用。

2.使用FPGA开发板的50MHZ时钟分频后25MHZ作为VGA输出时钟。

3.时钟频率25MHZ完成行扫描信号计数。

4.时钟频率25MHZ完成祯扫描信号计数,并完成祯计数。

5.在行,场信号有效范围内进行VGA数据输出。

软件设计部分

1:用matlab取图像的reb值,将取出的rgb值写入文件。

2:读取rbg值,将十六进制数表示的rgb值转化为以该asc||值对应的字符(减少信息传输量),将转化后的的字符写入文件中。

3:对转化后的文件数据进行压缩,发送目标文件格式为,文件头信息,发送文件的起始信息,用来判定开始发送数据,用三个字节,信息数据为GCL,一个字节表示最后一个字节的有效位,最后一个字节有效位为0bit- 8bit之间,一个字节表示文件中rgb的种类,0-255,四字节,表示整个压缩文件的大小,其后数据格式为,字符及字符对应的出现次数,即字符频度信息,字符频度之后对应的是压缩信息。

性能指标:频率、功耗等各种与系统相关性能指标;

三、 系统验证方案

描述系统级的验证方案,要求测试案例覆盖所设计系统的全部功能。

测试案例1:验证Huffman算法压缩解压缩可行性

1:编写最简单的huffman树,huffmancode,compress code。

2:显示软件统计字符及频度与最小模型是否一样。

3:显示软件生成的huffmantab与最小模型huffmantab是否一样。

4:显示软件递归生成的huffmantab code与最小模型huffmantab code是否一样。

5显示软件递归生成compresse code与最小模型compress code是否一样。

测试案例2:验证UART传输的正确性

利用串口由文件中读取数据,nios接收收据后将数据返回并显示,对比发送接收过程是否有数据丢失。确保数据正常的传输。

软件功能定义

LCD完成数据的显示。LCD的控制由8bit数据线,1bit的RS寄存器选择端,1数据寄存器,0表示指令寄存器,EN为1bit的使能端,值由0到1发生跳变,液晶执行指令,RW为1bit的读写信号线,高电平执行读的功能,低电平执行写的功能。lcd_on为电源端,lcd_blon为背光。

软件详细设计

1:LCD写命令

void LCD_Write_Command(Boolean Command)

{ IOWR_ALTERA_AVALON_PIO_DATA(LCD_DATA_ADDRESS , Command); //写数 IOWR_ALTERA_AVALON_PIO_DATA(LCD_RS_ADDRESS , 0); //指令

IOWR_ALTERA_AVALON_PIO_DATA(LCD_RW_ADDRESS , 0); // 写入 IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 1); // 使能 IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 0); //

usleep(2000);//2ms /*延时*/

}

2:LCD写数据

void LCD_Write_data(Boolean Data)

{ IOWR_ALTERA_AVALON_PIO_DATA(LCD_DATA_ADDRESS , Data); //写数据

IOWR_ALTERA_AVALON_PIO_DATA(LCD_RS_ADDRESS , 1); // 数据

IOWR_ALTERA_AVALON_PIO_DATA(LCD_RW_ADDRESS , 0); // 写入

IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 1); // 使能

/*延时150ns*/

IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 0); //

usleep(2000);//2ms /*延时*/

}

4:LCD初始化

void LCD_Write_Command(Boolean Command)

{IOWR_ALTERA_AVALON_PIO_DATA(LCD_DATA_ADDRESS , Command); //往数据

IOWR_ALTERA_AVALON_PIO_DATA(LCD_RS_ADDRESS , 0); //指令

IOWR_ALTERA_AVALON_PIO_DATA(LCD_RW_ADDRESS , 0); // 写入

IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 1); // 使能

IOWR_ALTERA_AVALON_PIO_DATA(LCD_EN_ADDRESS , 0); //

usleep(2000);//2ms /*延时*/

}

四、 开发资源

介绍所用到FPGA开发板所用的资源,主要包括:

1. 板上资源:例如VGA、LCD等;

2. 片上资源:Altera Cyclone II 2C70;

五、 系统开发计划

1. 系统需求分析、功能定义与验证方案

2. 硬件详细设计与验证方案

1. VGA接口模块详细设计

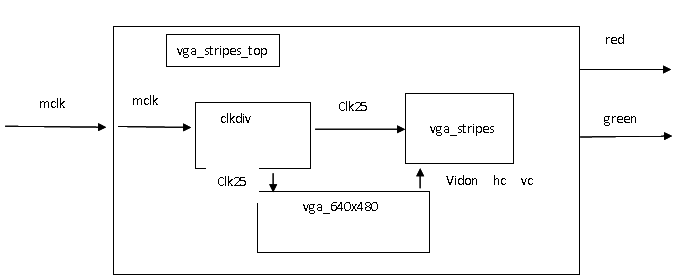

1). 每个子模块的功能

一,vga_640x480模块,进行计时,来控制显示

二,vga_stripes模块 这样每隔16行颜色交替为红色和绿色(且在vidon=1时显示)

三,clkdiv模块:进行时钟分频,得到该实验需要的25MHZ的时钟;

四,vga_stripes_top模块:为主调用函数

五,test_vga模块:激励模块

2). 每个子模块的输入输出

3 软件详细设计与验证方案

1. 哈弗曼解压缩模块设计

1)子程序功能定义

将接收到的压缩数据进行解压缩

2)子程序输入输出说明

输入为abc_code.txt-------编码文件;

输出为abc_dcode.txt------译码文件。

4. FPGA后端调试与测试

5.撰写报告

六、 开发环境

Quartusii 8.0 NIOSii IDE DE2-70开发板

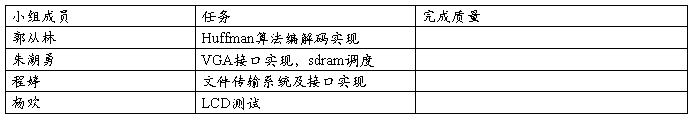

七、 人员分配

八、 结束语

1)对技术报告进行总结;

本文主要研究JPEG静态图象压缩编码解码技术,并在Nios系统中完成了图像压缩系统。主要工作在于:

(1)设计基于SOPC技术的Huffman编码解码系统使用FPGA和一些比较通用的器件设计并实现了图像压缩系统,该压缩系统在一块FPGA上实现了vga接口处理器。

(2)完成了图像压缩解码系统的编程

主要介绍了Huffman的解码原理和Nios IDE实现了该算法。在软件设计中配置完成了Nios操作系统,并完成了系统软件和一些外围硬件的驱动。并且结合Huffman算法原理和FPGA的硬件平台和嵌入式编程环境,较好地实现了Huffman算法的编码解码。

参考书

1.吕凤军.数字图像处理编程入门,清华大学出版社,1999, 287312.

2.林福宗.多媒体技术基础,清华大学出版社,2000, 178200.

BHASKARAN, V., KONSTANTINIDES, K. ((Image and Video Compression Standards

Algorithms and Architectures一Second Edition)).Kluwer Academic Publishers, USA,

1999.

3.汪宇.JPEG高速编码芯片的设计及其性能优化,西北工业大学硕士学位论文,2006.2.

4.任爱锋,初秀琴等.基于FPGA的嵌入式系统设计.第一版.西安:西安电了科技大学出版社,2004, 9一53

5.潘松,黄继业.EDA技术实用教程.第一版.北京:科学出版社,2002,3254

6.任艳颖,土彬.IC设计基础.西安电了科技大学出版社.2003.5:342.

7.吴继华,土诚.Altera FPGA/CPLD设计(高级篇).人民邮电出版社.2005.7:1 }50.

第二篇:SoC设计方法学-报告二格式 - 副本

《XXX系统》课程报告之二(三号字)

《XXX系统》功能定义与开发计划

班级:

小组:

班级:

组长:

学号:

日期:

(小二,黑体)

《XXX系统》功能定义与开发计划(三号字)

摘要(四号、黑体)

简要说明这份文档的主要内容(小四)

关键字:

一、 引言(四号字、黑体,标题)

介绍拟开发项目的动机;本次报告的目的;(小四)

二、 功能定义

1. 功能:定义所开发项目软件与硬件功能;

2. 性能指标:频率、功耗等各种与系统相关性能指标;

3. 输入输出定义:定义所设计系统的输入输出;

三、 系统验证方案

描述系统级的验证方案,要求测试案例覆盖所设计系统的全部功能。 测试案例1:测试目的

测试案例2:测试目的

。。。。

四、 开发资源

介绍所用到FPGA开发板所用的资源,主要包括:

1. 板上资源:例如VGA、指示灯等;

2. 片上资源:说明用到FPGA的软IP与硬IP;

五、 系统开发计划

1. 系统需求分析、功能定义与验证方案

2. 硬件详细设计与验证方案

3 软件详细设计与验证方案

4. FPGA后端调试与测试

5.撰写报告

六、 开发环境

介绍项目开发用到的软硬件环境

七、 人员分配

介绍一个小组人员的分工情况,每个小组需要列出各个成员的任务及其完成的设计模块。

八、 结束语

参考书

1.作者姓名,书名/文件名,出版社/杂志名称,出版日期/杂志卷号+页号; 2.

3.

。。。

说明:1. 本次报告以小组为单位只提交一份。

2. 标题用四号黑体,正文用小四宋体,行间距1.3

3. 一级标题用汉语一、二、三、…. ;二级标题用罗马数字1,2,。。。;三级标题用1),2),3)。原则上不超过三级标题。

4. 报告中的图用:图1,图2.。。说明,每张图必须说明用途;例如,图1 XXX系统的总体设计;图的解释需要在图下面。如果用表,则用表1,表2.。。说明,每张表也需要说明用途。 例如,表1 XXX实验在XXX参数设置下的结果;表的解释需要放在表上面。

5报告用A4打印纸打印。

6提交的报告需要组员签字。组长给出每个小组成员在报告中的贡献,给出一个成绩,成绩范围为1分~10分。