扬州大学广陵学院

扬州大学广陵学院

课程设计报告

设计题目: 流水灯设计

姓 名: z t y

学 号: 100036137

班 级: 微电81001

时 间:2013年 7月 4日

目 录

一. 设计任务与要求…………………………………………3

二. 实验目的…………………………………………….…..3

三. 实验思路…………………………………………….…..3

1系统逻辑设计……………………………………...…3

2源程序代码………………………………………..…3

⑴LED流水灯控制模块………………………………….4

⑵分频器…………………………………………………5

⑶四位选择器…………………………………………….5

⑷六位计数器…………………………………………..6

⑸2位计数器…………………………………………...6

3实验原理调用………………………………… …….7

4仿真结果与分析…………………………….……….7

四. 心得体会……………………………………………..….8

一.设计任务与要求

随着大规模集成电路技术和EDA技术的迅速发展,使得数字系统的硬件设计如同软件设计那样方便快捷,而Verilog HDL 是当前应用最广泛的并成为IEEE标准的一种硬件描述语言。Verilog HDL是在C语言的基础上演化而来,具有结构清晰、文法简明、功能强大、高速模拟和多库支持等优点。此次课程设计通过使用Verilog HDL硬件描述语言设计了一个程序,使得流水灯可以根据自己所期望的方式点亮,并能在、MAX+plusⅡ进行仿真测试,得出出仿真结果。通过课程设计深入理解VHDL语言的精髓,加深对数字电路和VHDL基本单元的理解,理论联系实际,提高设计能力,提高分析、解决计算机技术实际问题的独立工作能力。

二、实验目的

1、熟悉利用MAX+plusⅡ开发数字电路的基本流程和MAX+plusⅡ软件的相关操作。

2、掌握基本的设计思路、软件环境参数配置和仿真。

3、了解VerilogHDL语言设计或原理图设计方法。

4、通过本知识点的学习,了解流水灯的工作原理,掌握其逻辑功能设计方法。

三、实验思路

根据时钟信号的脉冲输入,我们以改变每个LED点亮状态的保持的时间来改变LED的变换间隔时间,根据LED的循环点亮和时间间隔的改变设计成为一个直观的LED流水灯自动循环系统,由此思路我们就可以很容易的着手流水灯控制程序的设计。

1. 系统逻辑设计:

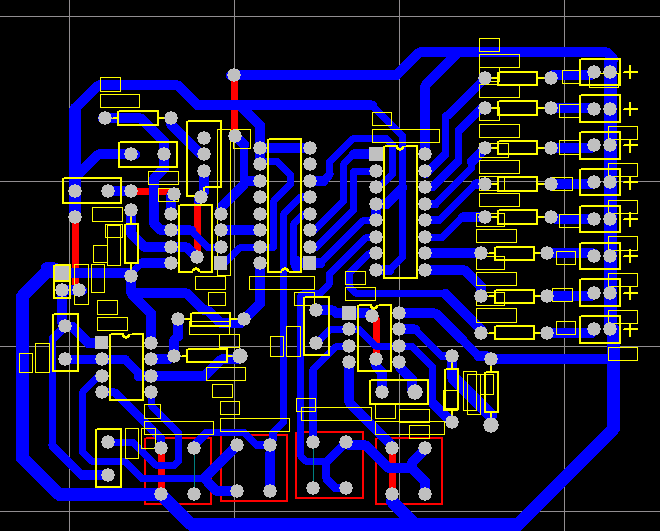

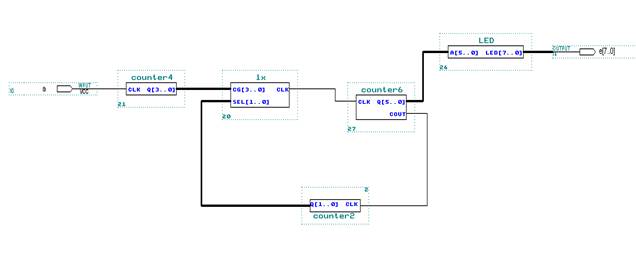

根据以上的设计要求,运用模块化的设计思路,我们在MAX+plusⅡ 软件系统中设计了LED流水灯控制模块、分频器模块、4位选择器、6位计数器、2位计数器,并通过各个模块程序之间的端口合理连接和协调,成功设计出LED流水灯灯控制电路,得到逻辑结构原理图,即为整个流水灯控制电路的逻辑结构。使用VerilogHDL语言设计相应的模块。

2. 源程序代码:

⑴LED流水灯控制模块

控制流水灯闪烁方案。

module LED( a, led );

input [5:0]a;

output [7:0]led;

reg [7:0] led;

always @(a)

begin

case(a)

0: led <= 8'b11111110;

1: led <= 8'b11111101;

2: led <= 8'b11111011;

3: led <= 8'b11110111;

4: led <= 8'b11101111;

5: led <= 8'b11011111;

6: led <= 8'b10111111;

7: led <= 8'b01111111;

8: led <= 8'b00111111;

9: led <= 8'b10011111;

10: led <= 8'b11001111;

11: led <= 8'b11100111;

12: led <= 8'b11110011;

13: led <= 8'b11111001;

14: led <= 8'b11111100;

15: led <= 8'b11111010;

16: led <= 8'b00011111;

17: led <= 8'b11000111;

18: led <= 8'b11110001;

19: led <= 8'b11111000;

20: led <= 8'b11110010;

21: led <= 8'b00111011;

22: led <= 8'b00101111;

23: led <= 8'b10111100;

24: led <= 8'b00001111;

25: led <= 8'b10000111;

26: led <= 8'b11000011;

27: led <= 8'b11100001;

28: led <= 8'b11110000;

29: led <= 8'b10111000;

30: led <= 8'b11101000;

31: led <= 8'b00011101;

32: led <= 8'b00000111;

33: led <= 8'b10000011;

34: led <= 8'b11000001;

35: led <= 8'b11100000;

36: led <= 8'b01110000;

37: led <= 8'b00111000;

38: led <= 8'b11001000;

39: led <= 8'b00010101;

default: led <= 8'b00000000;

endcase

end

endmodule

转化成symbol文件

⑵分频器

分频器可以用四位计数器替代。4位选择器选择不同的计数时,就会实验分频器的功能。

module counter4(q,clk);

output [3:0]q;

input clk;

reg [3:0] q;

always @( negedge clk)

begin

q<=q+1;

end

endmodule

转化成symbol文件

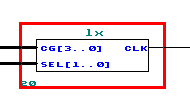

⑶四选一选择器

用来选择分频器不同时钟信号来控制流水灯亮暗速度。

module lx (cg,clk,sel);

input [3:0]cg;

input[1:0] sel;

output clk;

reg clk;

always @(cg or sel)

case(sel)

2'b00 : clk<=cg[0];

2'b01 : clk<=cg[1];

2'b10 : clk<=cg[2];

2'b11 : clk<=cg[3];

default :clk<=2'bx;

endcase

endmodule

转化成symbol文件

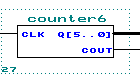

⑷六位计数器

六位计数器的输出来控制彩灯亮暗顺序一次执行

module counter6(q,clk,cout);

output [5:0]q;

output cout;

reg cout;

input clk;

reg [5:0] q;

always @(posedge clk)

begin

if(q==63)

begin

cout<=1;q<=0;

end

else

begin

q<=q+1;

cout<=0;

end

end

endmodule

转化成symbol文件

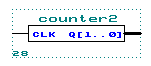

⑸2位计数器

6位计数器进位输出是2位计数器输入,2位计数器输出,用来反馈给选择器,选择不同时钟信号。

module counter2(q,clk);

output [1:0]q;

input clk;

reg [1:0] q;

always @( negedge clk)

begin

q<=q+1;

end

endmodule

转化成symbol文件

3. 文本式顶层文件调用

module led8(a,e);

input a;

output [7:0]e;

reg e;

LED a1(q,e);

Counter6 a2(q,clk,cout);

Lx a3(cg,clk,sel);

Counter4 a4(q,clk);

Counter2 a5(q,clk);

endmodule

原理顶层文件图

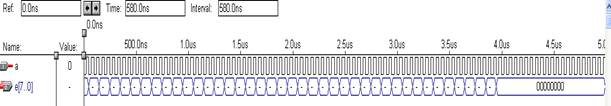

4.仿真结果与分析

从仿真结果中可以看出每一次波形过来时八盏彩灯亮的顺序和控制电路顺序一样,共设计四十种情况,当这四十种情况依次按照控制电路设计顺序亮结束时,剩余二十四种情况全部为熄灭,六十四种全部亮结束时再依次重复上面的顺序。

四、心得体会

通过本次课程设计,我基本对Verilog HDL的设计流程有了入门的了解和认识,在课堂之外进一步加深了对半定制课程各知识点的学习和以及MAX+plusⅡ软件开发平台的操作。也深深地感受到,工科的学习是来不得半点虚伪的,一定要自己动手操作,不懂就是不懂,而且不懂的多问问老师。对于程序的编写过程其实就是一个改错的过程,通过改错就会发现自己只是的不足。做课程设计的过程也是一个升华自我耐心的机会,不能因为一时找不到方法就放弃。课程设计与此同时也让我加深强了对课题的专业知识的认识和对专业文件检索能力。在短短的一周左右的时间里,我们经过自己的努力编写了流水灯设计。同时也感谢老师的帮助和提醒。

第二篇:多功能流水灯实验报告

多功能流水灯实验报告

作者:黄玉龙

20##年5月20日

一、设计任务及要求

1、 基本要求

(1) 设计一个彩灯控制电路,能使彩灯的流向可以变化。可以正向流水,也可以逆向流水。灯流动的方向可以手控也可以自控,自控往返变换时间为5秒。

(2) 彩灯可以间歇流动,10秒间歇1次,间歇时间1秒。

2、 发挥部分

(1) 彩灯流速可以改变

(2) 设计显示图案循环的控制电路

二、方案设计

基本原理设计框图如下图(1)所示:

电源 NE555 可逆计数器 191 译码器138

电源 NE555 可逆计数器 191 译码器138

图(1)设计框图

1、给整个电路接个电源。

2、用NE555来产生脉冲送到后面的芯片中。这里用了三个555。第一个是产生一般的秒冲,使得计数器计数;第二个是产生高低电平分别为5秒5秒的脉冲,使得191自动加减计数;第三个是用来产生10秒1秒的脉冲,使得可以产生工作10秒间歇1秒的功能。

3、可逆计数器,可用74HC191,也可用74LS190等,来实现加减计数,使得流水灯可以正向流动,也可以反向流动。

4、译码器用74LS138。用译码器的八个输出端分别接8个LED灯,根据3-8译码器的功能表就可知道每当加一次数,输出端就出现一个低电平,如此循环下来,就可实现LED灯的顺序流动。

信号流程如下:电源——第一个555——计数器——译码器——LED灯

电源——第二个555——计数器

电源——第三个555——译码器

三、电路设计

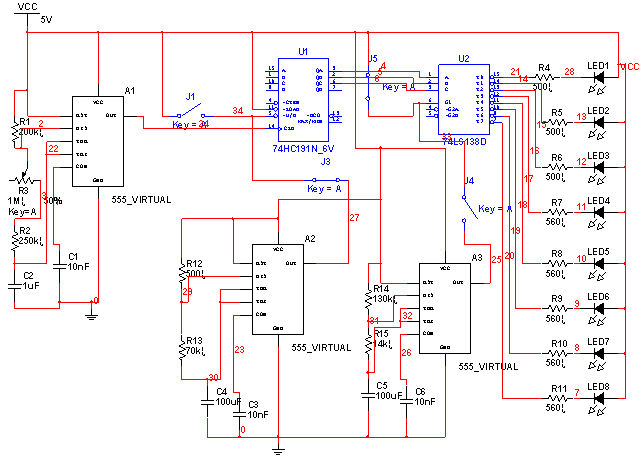

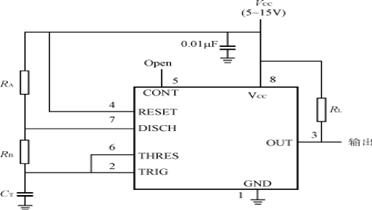

基本原理设计电路图如图(2)所示:

图(2)

基本的电路原理分析见第二步的方案设计,为了实现流速可变,可在第一个555的电路中加个可变电阻,调节电阻阻值改变脉冲周期,即改变计数时间,从而实现流速可调。

相应的计算如下:

根据以下两个公式t1=0.7R2 C t2=0.7(R1+R2)C 可得如下数据:

C1=10nF C2=1uF R1=200k R2=250k Rp=200k

C3=10nF C4=100uF R3=500 R4=70k

C5=10nF C=100uF R5=130k R6=14k

根据发光二极管的工作电流为10-16mA左右,可计算得所加的限流电阻为400-600右,试验中取RL=510

四、测试与结果分析

电路设计,安装元器件及连好导线后,进行实验结果测试。实验前首先完成以下步骤:

1.检查电路原理图及导线的连接。在电脑上仿真,能够得出正确的实验现象,

所以电路原理图正确。检查导线的连接是否与电路原理图上一致。

2.检查导线的连接。对照电路原理图,用数字万用表打到合适的档位,测试各对应的接点是否连接好并导通。

3.检查实验仪器和器材是否完好。电源5伏直流电压输出正常,CD4017芯片测试其功能均正常,用万用表检查开关,按下时导通均正常。

完成上述步骤后,接通5伏的直流电源,实验现象为:

(注:因为我用的开关不是锁住开关,所以按开关时要长按住开关才能实现所要求的功能)

开关S1为手控开关,一开始开关S1断开,灯为正向流动,长按开关S1时流水灯逆向流动;开关S2为自控开关,长按住开关S2,流水灯正向流完后会自动反向流动,如此一直往返;长按住开关S3,流水灯会出现亮10秒停1秒的间歇流动;调节Rp的阻值,流水灯的流速发生了改变。至此,多功能流水灯电路设计,调试与实验基本成功。

五、个人总结

做板的时候遇到了一些问题,如铜线太大,又如焊盘太小不好焊接的问题,经过几次的修改基本完成了本实验。在protel中弄原理图时,有个555芯片少接了个地,最后检查出来就在电路板上补加了一条导线连接到地。在555电路中,把两个电容接反了,最后改了过来。

最终经过不断的检查、调试和分析,成功完成了多功能流水灯的基本要求和部分发挥部分,得出了正确的实验现象,按下电路开关,电路可在预定的时间到来时,产生一个控制信号控制彩灯的流向、间歇等,与此同时,通过利用中规模集成电路中可逆计数器和译码器来·实现正、逆流水功能,利用组合电路实现自控、手控、流向控制等功能。通过这个实验得到了不少经验,实验的检查测试阶段,实验现象不符合理论时,切忌过分紧张和焦急,而应该冷静地检查分析存在的问题,在导线的连接过程中,检查一根测试一根,查处问题及时解决,避免了完成连接后又出现混乱,没法解决的局面。这也是每个人在平时的实验过程中值得重视和注意的。

本人还认为,多功能流水灯的设计这个课题重点考察了对数字电路知识的理解和应用,如试验中的编码和译码,555定时器的应用,进一步强化和巩固了理论知识的学习,同时又加深了自己对multisim和protel灯软件的学习与应用,理论和实践相结合,从而更好地掌握所学知识,达到学为所用的目的。

六、参考文献

[1] 高吉祥 主编 电子技术基础实验与课程设计 电子工业出版社 2002.2

[2] 康华光 电子技术基础数字部分(第四版) 高等教育出版社 2003.3

[3] 陈俊亮 数字电路逻辑设计 人民邮电出版社 1980

[4] 张端 数字电路与逻辑设计 高等教育出版社 1985

[5] 韩广兴 电子元器件与使用电炉基础 电子工业出版社 2005

[6] 陈永甫 新编555继承电路应用800例 电子工业出版社 2000

[7] 吴立新 实用电子技术手册 机械工业出版社 2003

[8] 陆昆 电子设计技术 电子科技大学出版社 1997

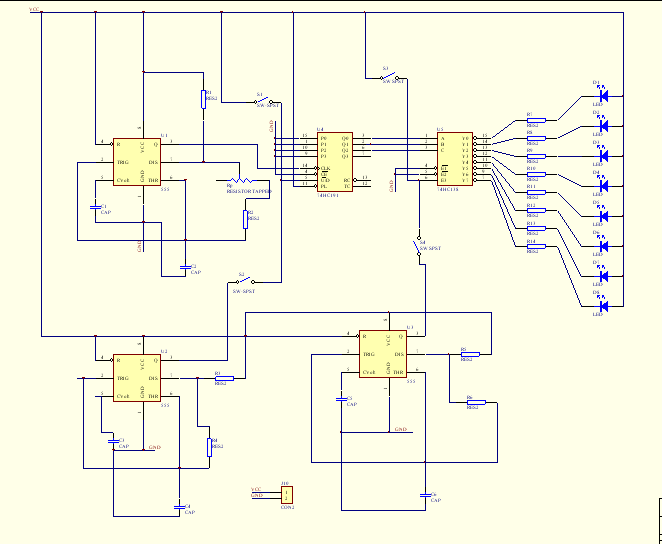

七、附录

附录一

系统电路原理图

附录二

NE555集成电路内部方框图及引脚图

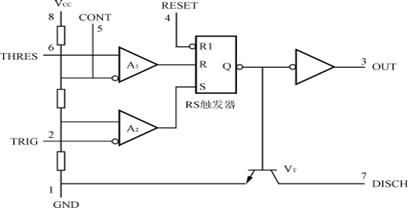

NE555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。NE555的作用是用内部的定时器来构成时基电路,给其他的电路提供时序脉冲。NE555时基电路有两种封装形式有,一是dip双列直插8脚封装,另一种是sop-8小型(smd)封装形式。其他ha17555、lm555、ca555分属不同的公司生产的产品。内部结构和工作原理都相同。NE555的内部结构可等效成23个晶体三极管.17个电阻.两个二极管.组成了比较器.RS触发器.等多组单元电路.特别是由三只精度较高5k电阻构成了一个电阻分压器.为上.下比较器提供基准电压.所以称之为555.NE555属于cmos工艺制造. 其内部含有两个电压比较器,一个分压器,一个RS触发器,一个放电晶体管和一个功率输出级。

NE555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。NE555的作用是用内部的定时器来构成时基电路,给其他的电路提供时序脉冲。NE555时基电路有两种封装形式有,一是dip双列直插8脚封装,另一种是sop-8小型(smd)封装形式。其他ha17555、lm555、ca555分属不同的公司生产的产品。内部结构和工作原理都相同。NE555的内部结构可等效成23个晶体三极管.17个电阻.两个二极管.组成了比较器.RS触发器.等多组单元电路.特别是由三只精度较高5k电阻构成了一个电阻分压器.为上.下比较器提供基准电压.所以称之为555.NE555属于cmos工艺制造. 其内部含有两个电压比较器,一个分压器,一个RS触发器,一个放电晶体管和一个功率输出级。

图1 NE555集成电路内部方框图

图2 NE555集成电路引脚图

附录三

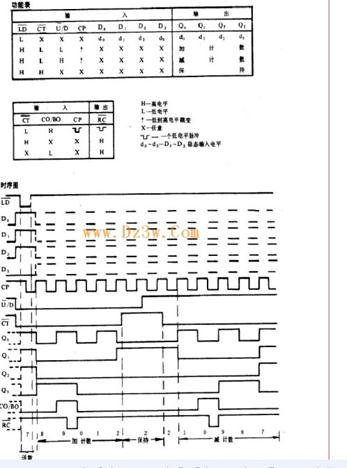

74HC191资料

附录四

印刷电路版图