计算机科学与技术学院团委 新闻中心

第二篇:苏州大学计算机组成题库

本科生期末试卷 一

一. 选择题 (每小题1分,共10分)

1.计算机系统中的存贮器系统是指______。

D 主存贮器和外存贮器

2.某机字长32位,其中1位符号位,31位表示尾数。若用定点小数表示,则最大正小数为______。

B +(1 – 2-31)

3.算术 / 逻辑运算单元74181ALU可完成______。

C 16种算术运算功能和16种逻辑运算功能

4.存储单元是指______。

B 存放一个机器字的所有存贮元集合

5.相联存贮器是按______进行寻址的存贮器。

C 内容指定方式

6.变址寻址方式中,操作数的有效地址等于______。

C 变址寄存器内容加上形式地址(位移量)

7.以下叙述中正确描述的句子是:______。

A 同一个CPU周期中,可以并行执行的微操作叫相容性微操作

D 同一个CPU周期中,不可以并行执行的微操作叫相斥性微操作

8.计算机使用总线结构的主要优点是便于实现积木化,同时______。

C 减少了信息传输线的条数

9.带有处理器的设备一般称为______设备。

A 智能化

10.某中断系统中,每抽取一个输入数据就要中断CPU一次,中断处理程序接收取样的数 据,并将其保存到主存缓冲区内。该中断处理需要X秒。另一方面,缓冲区内每存储 N 个数据,主程序就将其取出进行处理,这种处理需要Y秒,因此该系统可以跟踪到每 秒______次中断请求。

A.N / (NX + Y)

二. 填空题(每小题3分,共24分)

1.存储A.______并按B.______顺序执行,这是C.______型计算机的工作原理。

2.移码表示法主要用于表示A.______数的阶码E,以利于比较两个B.______的大小和

C.______操作。

3.闪速存储器能提供高性能、低功耗、高可靠性及A.______能力,为现有的B.______体 系结构带来巨大变化,因此作为C.______用于便携式电脑中。

4.寻址方式按操作数的A.______位置不同,多使用B.______和C.______型,前者比后者执 行速度快。

5.微程序设计技术是利用A.______方法设计B.______的一门技术。具有规整性、可维护 性、C .______等一系列优点。

6.衡量总线性能的重要指标是A.______,它定义为总线本身所能达到的最高B.______。PCI 总线的带宽可达C.______。

7.显示适配器作为CRT和CPU的接口,由A. ______存储器,B. ______控制器,C. ______ 三部分组成。

8.DMA技术的出现使得A. ______可通过B. ______直接访问C. ______。

三. 应用题

1. (11分)设机器字长32位,定点表示,尾数31位,数符1位,问:

(1)定点原码整数表示时,最大正数是多少?最大负数是多少?

1

(2)定点原码小数表示时,最大正数是多少?最大负数是多少?

2. (11分)设存储器容量为32字,字长64位,模块数m = 4,分别用顺序方式和交叉方式进行组织。存储周

期T = 200ns,数据总线宽度为64位,总线周期τ = 50ns .问顺序存储器和交叉存储器的带宽各是多少?

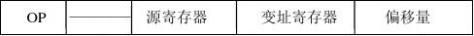

3. (11分)指令格式如下所示,OP为操作码字段,试分析指令格式特点。

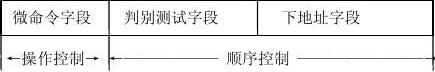

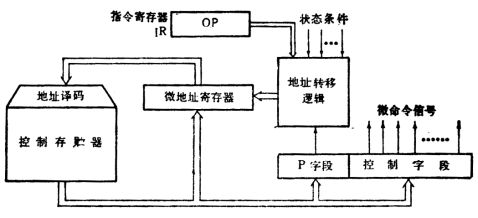

4. (11分)已知某机采用微程序控制方式,其存储器容量为512×48(位),微程序在整个控制存储器中实现

转移,可控制微程序的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式,如图所示:

(1) 微指令中的三个字段分别应多少位?

(2) 画出对应这种微指令格式的微程序控制器逻辑框图。

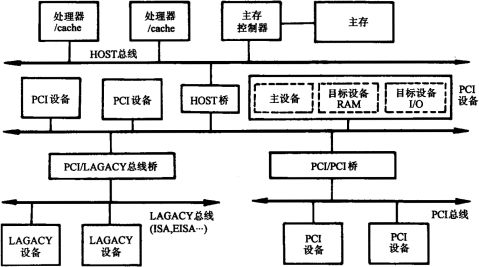

5. (11分)画出PCI总线结构图,说明三种桥的功能。

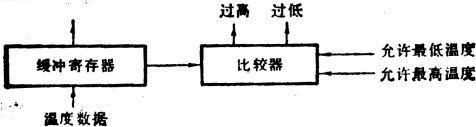

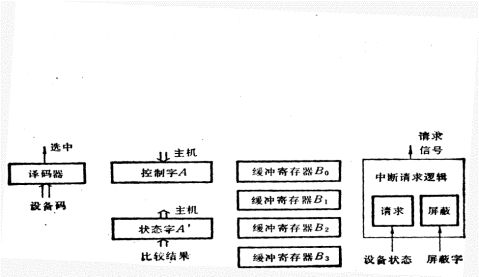

6. (11分)某机用于生产过程中的温度数据采集,每个采集器含有8位数据缓冲寄存器一个,比较器一个,

能与给定范围比较,可发出“温度过低”或“温度过高”的信号,如图B1.1所示。主机采用外设单独编址,四个采集器公用一个设备码,共用一个接口,允许采用两种方式访问:

(1) 定期巡回检测方式,主机可编程指定访问该设备中的某一采集器。

(2) 中断方式,当采集温度比给定范围过底或过高时能提出随机中断请求,主机应能判别是哪一个采集器

请求,是温度过低或过高。

请拟定该接口中有哪些主要部件(不要求画出完整的连线图),并概略说明在两

种方式下的工作原理。

图B1.1

本科生期末试卷一答案

一. 选择题

1. D 2. B 3. C 4. B 5. C

6. C 7. A、D 8. C 9. A 10. A

二. 填空题

1. A.程序 B.地址 C.冯·诺依曼

2. A.浮点 B.指数 C.对阶

3. A. 瞬时启动 B.存储器 C.固态盘

4. A.物理 B.RR C.RS

2

5. A.软件 B.操作控制 C.灵活性

6. A.总线带宽 B.传输速率 C.264MB / S

7. A.刷新 B.显示 C.ROM BIOS

8. A.外围设备 B.DMA控制器 C.内存

三. 应用题

1. 解:(1

31

数值 = (2 – 1)10

最大负数: 数值 = -(2 – 1)10

(2)定点原码小数表示:

最大正数值 = (1 – 2-31 )10

最大负数值 = -(1 – 2)10

2. 解:信息总量: q = 64位 ×4 =256位

顺序存储器和交叉存储器读出4个字的时间分别是:

t2 = m T = 4×200ns =8×10 –7 (s)

t1 = T + (m – 1)τ = 200 + 3×50 = 3.5 ×10 –7 (s)

顺序存储器带宽是:

W1 = q / t2 = 32 ×107 (位/ S)

交叉存储器带宽是:

W2 = q / t1 = 73 ×107 (位/ S)

63. 解:(1)操作码字段为6位,可指定 2 = 64种操作,即64条指令。

(2)单字长(32)二地址指令。

(3)一个操作数在原寄存器(共16个),另一个操作数在存储器中(由变址寄

存器内容 + 偏移量决定),所以是RS型指令。

(4)这种指令结构用于访问存储器。

4. 解:(1)假设判别测试字段中每一位为一个判别标志,那么由于有4个转移条件, 故该字段为4

位,(如采用字段译码只需3位),下地址字段为9位,因为控制容量为512单元,微命令字段是( 48 – 4 - 9 )= 35 位。

(2)对应上述微指令格式的微程序控制器逻辑框图B1.2如下:其中微地址寄存器对应下地址字段,P字段即为判别测试字段,控制字段即为微命令子段,后两部分组成微指令寄存器。地址转移逻辑的输入是指令寄存器OP码,各状态条件以及判别测试字段所给的判别标志(某一位为1),其输出修改微地址寄存器的适当位数,从而实现微程序的分支转移。

图B1.2 -31

3

5. 解:PCI总线结构框图如图B1.3所示:

图.B1.3

PCI总线有三种桥,即HOST / PCI桥(简称HOST桥),PCI / PCI桥,PCI / LAGACY桥。在PCI总线体系结构中,桥起着重要作用:

(1) 它连接两条总线,使总线间相互通信。

(2) 桥是一个总线转换部件,可以把一条总线的地址空间映射到另一条总线的地址空间上,从而使系统中任

意一个总线主设备都能看到同样的一份地址表。

(3) 利用桥可以实现总线间的卒发式传送。

6. 解:数据采集接口方案设计如图B1.4所示。

现结合两种工作方式说明上述部件的工作。

(1)定期检寻方式

主机定期以输出指令DOA、设备码;(或传送指令)送出控制字到A寄存器,其中用四位分别指定选中的缓冲寄存器(四个B寄存器分别与四个采集器相应)。然后,主机以输入指令DIA、设备码;(或传送指令)取走数据。

(2)中断方式

比较结果形成状态字A' ,共8位,每二位表示一个采集器状态:00 正常 ,01 过低 ,10 过高。有任一处不正常(A' 中有一位以上为“1”)都将通过中断请求逻辑(内含请求触发器、屏蔽触发器)发出中断请求。中断响应后,服务程序以DIA、设备码;或传送指令)取走状态字。可判明有几处采集数据越限、是过高或过低,从而转入相应处理。

图B1.4

4