桂林电子科技大学信息科技学院

《EDA技术及应用》实训报告

学 号 1252100301

姓 名

指导教师:覃琴

2014年 4 月 29 日

实训题目:数字日历电路

1 系统设计

1.1 设计要求

1.1.1 设计任务

(1)用Verilog HDL语言设计出能够在EDA实训仪的I/O设备和PLD芯片实现的数字日历。

(2)数字日历能够显示年、月、日、时、分和秒。

(3)用EDA实训仪上的8只八段数码管分两屏分别显示年、月、日和时、分、秒,即在一定时间段内显示年、月、日(如20140101),然后在另一时间段内显示时、分、秒(如010101099),两个时间段能自动倒换。

(4)数字日历具有复位和校准年、月、日、时、分、秒的按钮,但校年和校时同用一个按钮,即在显示年、月、日时用此按钮校年,在显示时、分、秒时则用此按钮校时。

(5)体现创新部分

1.1.2 性能指标要求

1)数字电路能够在一定的时间内显示切换的功能,并且能手动校准年月日和时分秒

2)具有复位和进位的功能

3)能起到提示的作用,如闹钟或亮彩灯等。

1.2 设计思路及设计框图

1.2.1设计思路

如图1.2.2所示

1) EDA实训箱上的功能有限,可以用到的有8支数码管和12个lED灯。年、月、日和时、分、秒可以通过数码管显示,年月日和时分秒的切换可以通过拨动开关控制,校正可以通过按键实现。

2)输入的秒脉冲由DEA实训仪上的20MHZ晶振经过分频得到,秒脉冲经过60分频后产生1分钟脉冲信号,在经过60分频后产生1小时的脉冲信号,最后进行24分频,得到1天的脉冲送24进制的 cout输出。在将两个60分频和一个24分频的输出送到送到数码管的译码器输入端,得到24小时的计时显示结果。由此得到数字日历的计时器模块。

1.2.2设计框图

cout cout

cout cout

秒脉冲

秒脉冲

图1.2.2数字钟的原理框图

2 各个模块程序的设计

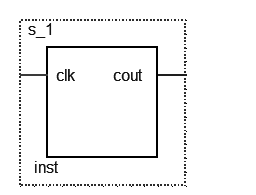

2.1图1 1HZ秒脉冲的分频模块元件符号

2.1输入的秒脉冲由EDA实训仪上的20MHZ晶振经过分频得到,设计一个输出频率为1HZ的秒脉冲。图1是1HZ秒脉冲的分频模块元件符号

图1 1HZ秒脉冲的分频模块元件符号

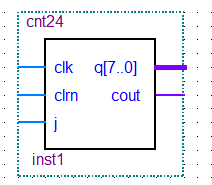

2.2 图2是cnt24与cnt60模块设计的元件符号

图2 cnt24与cnt60模块的元件符号

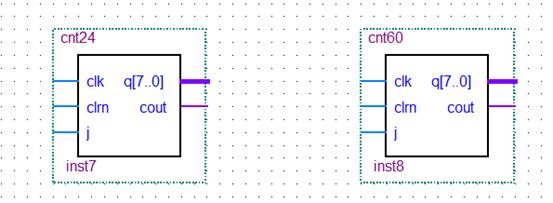

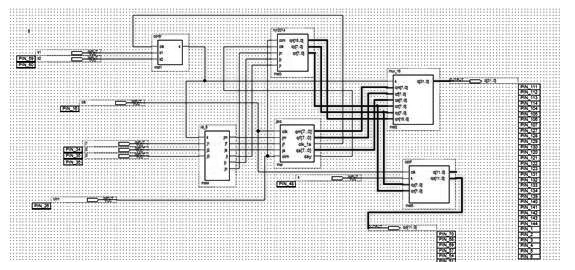

2.3 图3是计时器设计原理图

clk秒时钟输入端,clrn清除输入端,低电平有效;jm、jf 、js分别是校秒、校分和校时的输入端,下降沿有效;qm[7..0]、qf[7..0]和qs[7..0]分别是秒、分、和时的输出端;cout是“天”脉冲输出端。

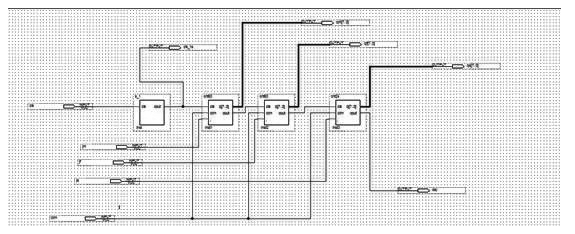

2.4数字日历电路的设计

数字电路原理图包括包括计时器模块(jsq)、年月日模块(nyr2014)、控制模块(cour)、校时选择模块(xs_6)、显示选择模块(mux_16)和流水灯(LED)提示模块。图4是数字日历设计的原理图。

图4是数字日历设计的原理图

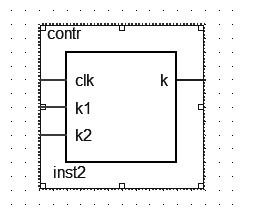

2.5控制模块的设计

图5是控制模块的元件符号

图5 控制模块的元件符号

clk是1s时钟输入端;k1和k2是控制输入端,k是控制输出端。k1k2=00或11时是自动显示模块,控制数码器用8s钟时间显示年月日8s显示时分秒,k1k2=01时仅控制显示时分秒,同时用j1、j2、j3校秒、校分和校时,k1k2=10时,仅显示年、月、日,同时用j1、j2、j3校年、校月和校日。

2.6校时选择模块的设计

校时选择模块的元件符号如图6所示。k是控制输入端,k=0是,控制将校时按钮j1、j2和j3的信号分别分别送到计时器模块的jm、jf、js,k=1时校时按钮j1、j2、j3的信号分别送到年月日模块的jr、jy、jn。

图6 校时选择模块的元件符号

2.7显示选择模块

图7是显示选择模块的元件符号。k是控制输入端,K=0时,控制将计时器模块送来的qm[7..0]、qf[7..0]、和qs[7..0]状态信号送到数码管显示。k=1时将年月日送来的qr[7..0]、qy[7..0]、qn[7..0]状态信号送到数码管显示。

图7 显示选择模块的元件符号

2.8流水灯提示模块的设计

图8是流水灯提示模块的元件符号。clk是一秒钟输入端,K是控制输入端,qy[7..0](月)、qr[7..0](日)是状态信号送到数码管显示。qo[11..0]是输出的流水灯

图8 流水灯提示模块的元件符号

3 调试过程

当数字日历得所有模块编译成功后我首次下载到实训箱上时,它并不能实现进位的功能,经调整。数字日历的各基本功能通实现后,在其基础上新增了彩灯控制模块。经过逐条编写和更正。程序最终通过编译并能顺利下载到实训箱上进行验证。

4 功能测试

4.1 测试仪器与设备

EDA实训箱

4.2 性能指标测试

当所设定的生日到时流水灯能顺利的实现该提示功能,不过自动显示模块还是没能很准确的进行累加,该功能的延时时间超出了设计的时间。

5 实训心得体会

从陌生到熟悉,我基本上的摸清了QuartusII9.0的用法。并逐渐掌握了verilog HDL语言的规则。并能编写简单的程序。经过查找资料和各个老师的耐心指导。我完成了数字日历电路的设计。不仅添加了创新部分,还在EDA实训仪上成功实现了它的彩灯旋转功能。并用一个拨动开关来控制灯的亮灭。记得刚开始拿到实训课题时,我那一脸的茫然,不知从哪儿入手。来回跑了图书馆好几趟,最后跟着舍友起步。从编写代码开始,经编译后逐个查找错误并纠正。几番波折,最终完成了数字日历的设计和添加了创新功能。

通过此次EDA实训我熟练的掌握了QuartusII9.0软件,并能通过波形仿真更加透彻的掌握了程序与该设计。从编程到生成元器件再到波形仿真和成功下载,给我的最大体会是一步一个脚印,付出总会有回报的。

6 参考文献

【1】EDA技术与应用 江国强

【2】EDA技术与verilog设计 王金明 冷自强

附录

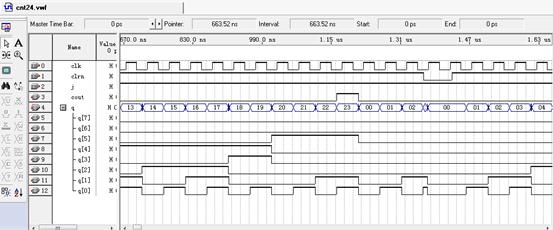

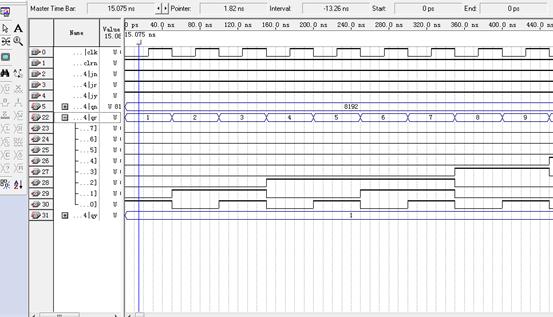

附录1:仿真波形图(部分模块)

cnt24模块仿真波形图

nyr模块仿真波形图

附录2:程序清单

2.1 分频器模块

module s_1 ( clk,cout);

input clk;

reg [24:0] q;

output reg cout;

always @(posedge clk)

begin

if (q==20000000-1) q=0; //1s

else q=q+1;

if(q<=10000000-1) cout=1; //0.5s

else cout=0;

end

Endmodule

2.2 cnt24计数器源程序

module cnt24(clk,clrn,j,q,cout); //clk秒时钟输入端,clrn清除输入端,cout“天”脉冲输出端

input clk,clrn,j; //j校时输入端,

output reg [7:0] q;

output reg cout;

always @ (posedge clk^j or negedge clrn) //j与时钟输入端clk异或就可以达到校时的作用

begin

if (~clrn) q=0; //低电平有效

else begin

if (q=='h23) q=0;

else q=q+1;

if (q[3:0]=='ha) begin

q[3:0]=0; q[7:4]=q[7:4]+1; end

if (q=='h23) cout=1;

else cout=0;end

end

endmodule

2.3 cnt60计数器源程序

module cnt60(clk,clrn,j,q,cout);

input clk,clrn,j;

output reg [7:0] q;

output reg cout;

always @ (posedge clk^j or negedge clrn)

begin

if (~clrn) q=0;

else begin

if (q=='h59) q=0;

else q=q+1;

if (q[3:0]=='ha) begin

q[3:0]=0; q[7:4]=q[7:4]+1; end

if (q=='h59) cout=1;

else cout=0;end

end

endmodule

2.4 年月日模块

module nyr2014(clrn,clk,jn,jy,jr,qn,qy,qr);

input clrn,clk,jn,jy,jr;

output [15:0] qn;

output [7:0]qy,qr;

reg [15:0] qn;

reg[7:0] qy,qr;

reg clkn,clky;

reg[7:0] date;

reg clkn1, clkn2 , clkn3;

initial begin clkn1=1; clkn2=2 ; clkn3=1;end

initial begin qn='h2000;qy=1;qr=1;end

always @ (posedge (clk^jr) or negedge clrn)

begin

if (~clrn) qr=1;

else begin

if (qr==date) qr=1;

else qr=qr+1;

if (qr[3:0]=='ha) begin

qr[3:0]=0; qr[7:4]=qr[7:4]+1; end

if (qr==date) clky=1;

else clky=0;end

end

always @ (posedge clky^jy or negedge clrn)

begin

if (~clrn) qy=1;

else begin

if (qy=='h12) qy=1;

else qy=qy+1;

if (qy[3:0]=='ha) begin

qy[3:0]=0; qy[7:4]=qy[7:4]+1; end

if (qy=='h12) clkn=1;

else clkn=0;end

end

always

begin

case(qy)

'h01: date='h31;

'h02: begin

if ((qn/4==0)&(qn/100!=0)|(qn/400==0)) date='h29;

else date='h28;end

'h03: date='h31;

'h04: date='h30;

'h05: date='h31;

'h06: date='h30;

'h07: date='h31;

'h08: date='h31;

'h09: date='h30;

'h10: date='h31;

'h11: date='h30;

'h12: date='h31;

default :date='h30;

endcase

end

always @ (posedge (clkn^jn) or negedge clrn)

begin

if (~clrn) qn[3:0]=0;

else begin if (qn[3:0]==9) qn[3:0]=0;

else qn[3:0]= qn[3:0]+1;

if (qn[3:0]==9) clkn1=0;

else clkn1=1;end

end

always @ (posedge clkn1 or negedge clrn)

begin

if (~clrn) qn[7:4]=0;

else begin if (qn[7:4]==9) qn[7:4]=0;

else qn[7:4]=qn[7:4]+1;

if (qn[7:4]==9) clkn2=0;

else clkn2=1;end

end

always @ (posedge clkn2 or negedge clrn)

begin

if (~clrn) qn[11:8]=0;

else begin if (qn[11:8]==9) qn[11:8]=0;

else qn[11:8]= qn[11:8]+1;

if (qn[7:4]==9) clkn3=0;

else clkn3=1;end

end

always @ (posedge clkn3 or negedge clrn)

begin

if (~clrn) qn[15:12]=2;

else if (qn[15:12]==9) qn[15:12]=0;

else qn[15:12]= qn[15:12]+1;

end

Endmodule

2.5 校时选择模块

module xs_6(k,jm,jf,js,jr,jy,jn,j1,j2,j3); //k是控制输入端

input k,j1,j2,j3;

output reg jm,jf,js,jr,jy,jn;

always

Begin

if (k==0) {jm,jf,js}={j1,j2,j3};//k=0是,控制将校时按钮j1、j2和j3的信号分别分别送到计时器模块的jm、jf

else {jr,jy,jn}={j1,j2,j3};//k=1时校时按钮j1、j2、j3的信号分别送到年月日模块的jr、jy、jn

end

Endmodule

2.6显示选择模块的设计

module mux_16(k,qm,qf,qs,qr,qy,qn,q);

input k; //k是控制输入端,k=1时将年月日送来的qr、qy、qn状态信号送到数码管显示

input[7:0] qm,qf,qs,qr,qy;

input[15:0] qn;

output reg [31:0] q;

always

begin

if(k==0) begin

q[31:24]=0;

q[23:0]={qs,qf,qm};end

else q={qn,qy,qr};

end

endmodule

2.7控制模块源程序

module contr(clk,k1,k2,k); //clk是1s时钟输入端;k1和k2是控制输入端

input clk,k1,k2;

output reg k; //k是控制输出端

reg[3:0] qc;

reg rc;

always @(posedge clk)

begin

qc=qc+1;

if (qc<8)rc=0;

else rc=1;

case({k1,k2})

0:k=rc; //k1k2=00或11时是自动显示模块,控制数码器用8s钟时间显示年月日8s显示时分秒

1:k=0; //k1k2=01时仅控制显示时分秒,同时用j1、j2、j3校秒、校分和校时

2:k=1; //k1k2=10时,仅显示年、月、日,同时用j1、j2、j3校年、校月和校日

3:k=rc; //11

endcase end

endmodule

//在控制模块中使用了一个16分频电路,输出rc时16s的方波,即8s为高电平、8s为低电平用于万年历的自动倒换模式。

2.8 生日彩灯模块

module czbf (clk,k,qy,qr,q,qo);

input clk,k;

input [7:0] qy,qr;

output reg [11:0] q, qo;

reg s,qs,clkn;

reg[24:0] qq;

reg[6:0] qss;

initial q=5;

always @( posedge clk)

begin if (qq==2000000-1) qq=0; else qq=qq+1;

if (qq==2000000-1) clkn=1; else clkn=0;

end

always @(posedge clkn)

begin

if (s) begin qs=q[11]; q=q<<1;q[0]=qs;end

else begin qs=q[0]; q=q>>1;q[11]=qs;end

end

always @(posedge clkn)

begin

qss=qss+1;

if (qss<63) s=0; else s=1;

end

always

begin if (qy=='h05&qr=='h13&k) qo=q;

else qo=0;

end

endmodule

//当数码管上的月日与某生日相同时,流水灯相继左右旋转。此时可通用拨动开关K控制流水灯的亮灭。