静态随机存储器实验

组员:

组号:21组

日期:周二5、6节

【实验目的】

掌握静态随机存储器RAM工作特性及数据的读/写方法。

【实验设备】

实验仪一台、PC机一台(观察波形)

【实验原理】

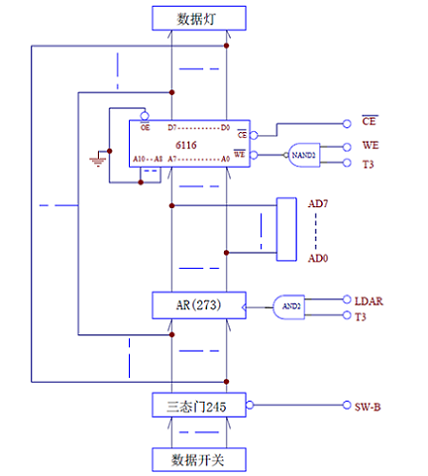

由一片6116(2K x 8)芯片、一片8位锁存器(74LS273)、一片8位三态门(74LS245)构成存储器原理图。

存储器实验原理图

由于存储器地址是由数据开关(input device)锁存在(273),存储器写数据也是由数据开关提供的,因此要分时给出地址和写数据。

因地址寄存器为8 位,所以接入6116 的地址为A7~A0,而高三位A8~A10 接地,所以其实际容量为256 字节。6116 有三个控制线:CE(片选线)、OE(读线)、WE(写线)。当片选有效(CE=0)时,OE=0 时进行读操作,WE=0 时进行写操作。本实验中将OE 常接地,在此情况下,当CE=0、WE=0 时进行读操作,CE=0、WE=1 时进行写操作,其写时间与T3 脉冲宽度一致。

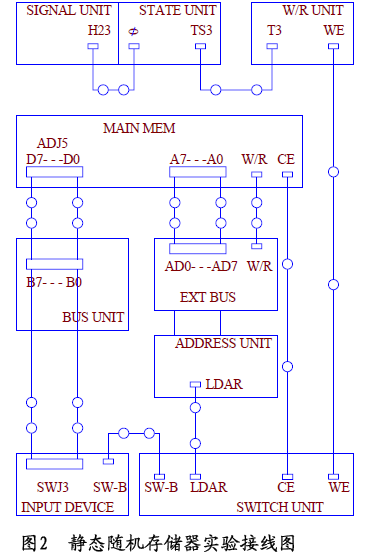

实验时将T3 脉冲接至实验板上时序电路模块的TS3 相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B 为低电平有效,LDAR 为高电平有效。

【实验步骤】

(1) 形成时钟脉冲信号T3。具体接线方法和操作步骤如下:

① 接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1 及W2 ,使H23 端输出实验所期望的频率及占空比的方波。

② 将时序电路模块(STATE UNIT)单元中的ф和信号源单元(SIGNAL UNIT)中的H23 排针相连。

③ 在时序电路模块中有两个二进制开关“STOP”和“STEP” 。将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则TS3端即输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3 输出实验要求的脉冲信号。当“STOP”开关置为“RUN”状态、“STEP”开关置为“STEP”状态时,每按动一次微动开关START,则T3 输出一个单脉冲,其脉冲宽度与连续方式相同。若用PC 联机软件中的示波器功能也能看到波形,可以代替真实示波器。实验测得的实验频率和周期分别为:f=104.49HZ,T=9.57ms

(2) 按图连接实验线路,仔细查线无误后接通电源。

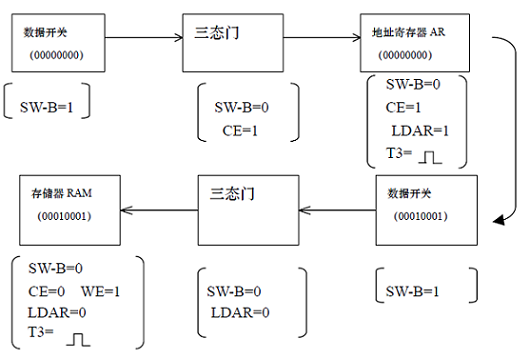

(3) 写存储器

给存储器的00、01、02、03、04 地址单元中分别写入数据11、12、13、14、15。

由上面的存储器实验原理图看出,由于数据和地址全由一个数据开关来给出,这就要分时地给出。下面的写存储器要分两个步骤,第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动START 产生T3 脉冲将地址打入到地址锁存器,第二步写数据,关掉地址锁存器门控信号(LDAR=0),打开存储器片选,使处于写状态(CE=0,WE=1),由开关给出此单元要写入的数据,按动START 产生T3 脉冲将数据写入到当前的地址单元中。写其它单元依次循环上述步骤。

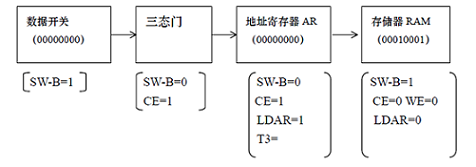

写存储器流程如下:(以向00 号单元写入11 为例)

(4) 读存储器

依次读出第 00、01、02、03、04 号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。同写操作类似,读每个单元也需要两步,第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动START 产生T3 脉冲将地址打入到地址锁存器;第二步读存储器,关掉地址锁存器门控信号(LDAR=0),关掉数据开关三态门(SW-B=1),片选存储器,使它处于读状态(CE=0,WE=0),此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。读其它单元依次循环上述步骤。读存储器操作流程如下:(以从00 号单元读出1 1 数据为例。

(5)将存储单元内数据进行运算

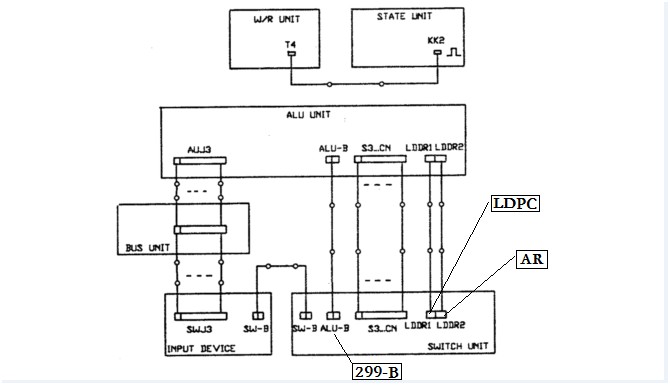

在原来实验连线的基础上,按如下所示图连线。

其中,由于某些端口需要重复连接,所以为防止出现运算错误,借连接到其他端口上。,如:ALU-B借连接到299-B,LDDR1借连接到LDPC,LDDR2借连接到AR上。

① 进行读操作,读出03号地址中数据,然后置SW-B=1,ALU-B=1(即使299-B开关置1),LDAR=0,CE=0,LDDR1=1(LDPC=1),LDDR2=0( AR=0),按动微动开关KK2,则将03号地址中的数据输入保存到LDDR1中。

② 进行读操作,读出04号地址中数据,然后SW-B, ALU-B, LDAR, CE开关置数保持不变,LDDR1=0,LDDDR2=1,按动微动开关KK2,则将04号地址中数据输入保存到LDDR2。

③ SW-B=1,ALU-B=0,CE=1,再分别将S3、S2、S1、S0、M、Cn分别置为100101,则3、4号地址中数据进行加法运算。

④ 将结果送入8号单元,将LDDR1,LDDR2全置0,然后按动微动开关KK2,将加法运算的结果送入LDDR1中,接着进行写地址操作:CE=1,LDAR=1,SW-B=0,由开关给出地址(00001000),按动START键产生T3脉冲将地址打入地址锁存器。然后写入数据: SW-B=0,ALU-B=0,按动KK2开关,将LDDR1中的数据输出到总线上,然后关闭地址锁存器LDAR=0打开存储器片选,使CE=0,WE=1,按动START开关将总线上的数据写入到8号地址单元中。

【结果分析】

将3号单元与4号单元中的数进行加法运算以后,然后得出结果为00101001(29),而3号单元中的00010100(14)与4号单元中的00010101(15),进行加法运算的结果也的确为00101001(29),可知运算器运算结果正确。将数据送入8号单元后,进行读数据操作,8号单元中的数据也与结果相符,说明操作无误。

【出现问题】

由于线路在写、读数据和进行运算时,线路有共用现象,所以在进行写、读数据的时候要保持ALU-B关闭,在进行运算器运算时要关闭片选CE,否则会出现地址和数据混乱的情况,不能得到正确的输入和输出结果,在实验的时候要特别注意。

第二篇:嵌入式存储器实验报告

实验三 存储器实验

1、FPGA中LPM_ROM定制与读出实验

实验课件参考:/CMPUT_EXPMT/Experiments/Expmt3 / 实验3-1.ppt

实验示例参考:/CMPUT_EXPMT/Experiments/Expmt3 / DEMO_3_1_rom

一.实验目的

1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。

2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于lpm_ROM中;

3、在初始化存储器编辑窗口编辑mif文件配置ROM;

4、验证FPGA中mega_lpm_ROM的功能。

二.实验原理

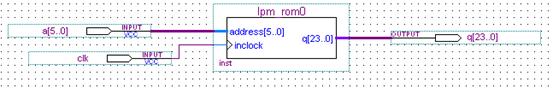

ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23..0]——lpm_ROM的24位数据输出端;a[5..0]——lpm_ROM的6位读出地址。

实验中主要应掌握以下三方面的内容:

(1)lpm_ROM的参数设置; (2)lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写;

(3)lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。

三.实验步骤

(1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[]和数据总线宽度q[],分别为6位和24位,并添加输入输出引脚,如图3-1-1设置和连接。

(2)设置图3-1-1为工程。

(3)在设置lpm_rom数据参数选择项lpm_file的对应窗口中(图3-1-2),用键盘输入lpm_ROM配置文件的路径(rom_a.mif),然后设置在系统ROM/RAM读写允许,以便能对FPGA中的ROM在系统读写。

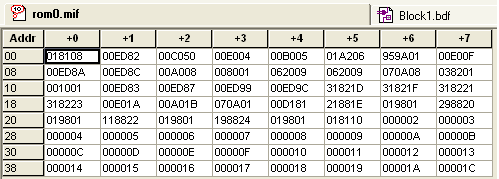

(4)用初始化存储器编辑窗口编辑lpm_ROM配置文件(文件名.mif)。这里预先给出后面将要用到的微程序文件:rom_a.mif 。rom_a.mif中的数据是微指令码(图3-1-3)。

(5)全程编译。

四.实验原理图

(1)rom结构图

(2)初始化文件rom

五.实验仿真波形图

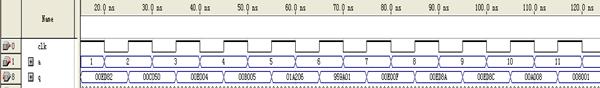

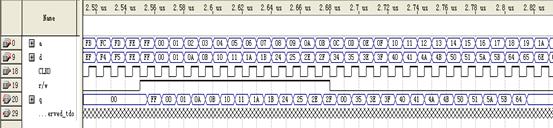

Clk为时钟脉冲,a为地址,q为数据。当clk上升沿时,将地址锁入,显示数值。波形图中,a为1时,q为00ED82;a为2是,q为00C050;a为3时,q为00E004。以此类推。可以看出,波形图与ROM初始化文件数据相同。

2.FPGA中LPM_RAM读写实验

实验课件参考:/CMPUT_EXPMT/Experiments/Expmt3 / 实验3-2.ppt

实验示例参考:/CMPUT_EXPMT/Experiments/Expmt3 / DEMO_3_2_RAM

一.实验目的

1、了解FPGA中RAMlpm_ram_dq的功能, 2、掌握lpm_ram_dq的参数设置和使用方法,

3、掌握lpm_ram_dq作为随机存储器RAM的工作特性和读写方法。

二.实验原理

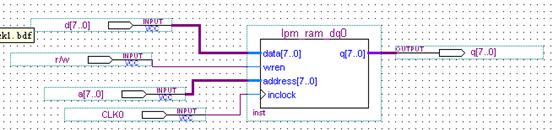

在FPGA中利用嵌入式阵列块EAB可以构成存储器,lpm_ram_dq的结构如图3-2-1。数据从ram_dp0的左边D[7..0]输入,从右边Q[7..0]输出,R/W——为读/写控制信号端。数据的写入:当输入数据和地址准备好以后,在inclock是地址锁存时钟,当信号上升沿到来时,地址被锁存,数据写入存储单元。

数据的读出:从A[7..0]输入存储单元地址,在CLK信号上升沿到来时,该单元数据从Q[7..0]输出。

R/W——读/写控制端,低电平时进行读操作,高电平时进行写操作;

CLK——读/写时钟脉冲; DATA[7..0]——RAM_dq0的8位数据输入端;

A[7..0]——RAM的读出和写入地址; Q[7..0]——RAM_dq0的8位数据输出端。

三.实验步骤

(1)按图3-2-1输入电路图。并进行编译、引脚锁定、FPGA配置。

(2)通过键1、键2输入RAM的8位数据(选择实验电路模式1),键3、键4输入存储器的8位地址。键8控制读/写允许,低电平时读允许,高电平时写允许;键7(CLK0)产生读/写时钟脉冲,即生成写地址锁存脉冲,对lpm_ram_dq进行写/读操作。

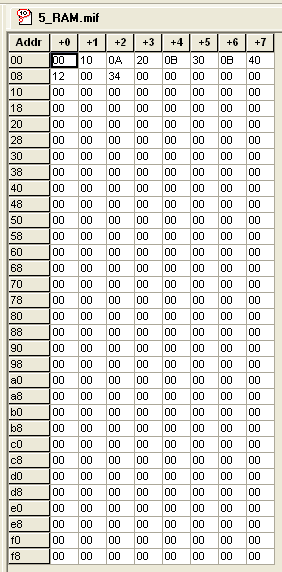

(3)注意,lpm_ram_dq也能加入初始化文件(这里是5_ram.mif ,是后面将要用到的模型CPU执行微程序文件),注意此文件加入的路径表达和文件表达(3-2-2): ./ 5_ram.mif ,(后缀mif要小写);

同时择在系统读写RAM功能,RAM的ID名取为:ram1。

四.实验原理图

(1)ram结构图

(2)初始化文件5_ram

五.实验仿真波形图

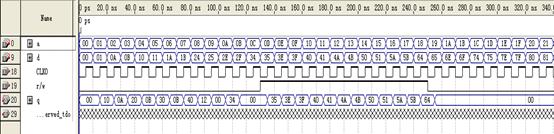

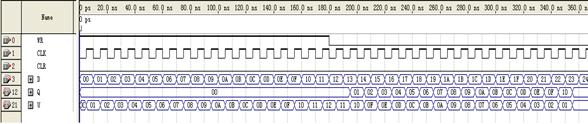

R/W为读/写控制端,低电平时进行读操作,高电平时进行写操作;CLK为读/写时钟脉冲;DATA[7..0]是RAM_dq0的8位数据输入端;A[7..0]是RAM的读出和写入地址; Q[7..0]是RAM_dq0的8位数据输出端。

在波形图一中,刚开始R/W为低电平,读初始化文件中的数据,直到高电平来临,将d数据写入地址a。在波形图二中,R/W为高电平,将d数据写入地址a,低电平来临,进行读操作,将在图一中写入a中的数据读出。

3. FIFO定制与读/写实验

实验课件参考:/CMPUT_EXPMT/Experiments/Expmt3 / 实验3-3.ppt

实验示例参考:/CMPUT_EXPMT/Experiments/Expmt3 / DEMO_3_3_FIFO

一.实验目的

1、掌握FPGA中先进先出存储器lpm_fifo的功能,工作特性和读写方法。

2、了解FPGA中lpm_fifo的功能,掌握lpm_fifo的参数设置和使用方法,

3、掌握lpm_fifo作为先进先出存储器FIFO的工作特性和读写方法。

二.实验原理

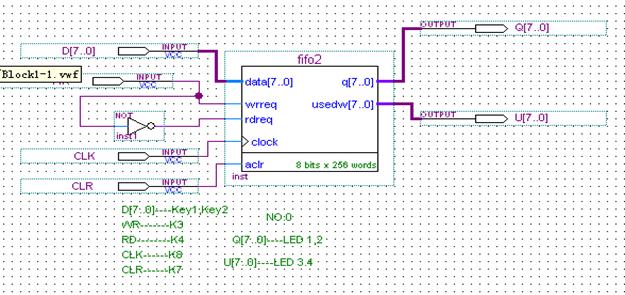

FIFO(First In First Out)是一种存储电路,用来存储、缓冲在两个异步时钟之间的数据传输。使用异步FIFO可以在两个不同时钟系统之间快速而方便地实时传输数据。在网络接口、图像处理、CPU设计等方面,FIFO具有广泛的应用。在FPGA中利用嵌入式阵列块EAB可以构成存储器,lpm_fifo的结构如图3-3-1所示。

WR — 写控制端,高电平时进行写操作; RD — 读控制端,高电平时进行读操作;

CLK — 读/写时钟脉冲; CLR — FIFO中数据异步清零信号;

D [7..0] — lpm_fifo的8位数据输入端; Q[7..0] — lpm_fifo的8位数据输出端;

U[7..0] — 表示lpm_fifo已经使用的地址空间。

三.实验步骤

1.编辑输入lpm_fifo实验电路(双击原理图3-3-1的FIFO元件,可进入该元件的编辑窗)。

2.将编译通过的文件下载到GW-48实验台,实验台选择工作模式NO.0;

3.通过实验台上的键1、键2输入数据,键3控制读/写允许WR(高电平写有效,低电平读有效,)、键7控制数据清0(高电平清0有效)、键8输入CLK信号,数码管4/3显示已占用地址,数码管2/1显示FIFO输出的数据:

(1)将数据写入LPM-FIFO:键3置高电平(写允许);键7清0一次;键1、键2每输入一个新数据(数据显示于发光管D8-D1),键8就给出一个脉冲(按键0-1-0),将数据压入FIFO中;

(2)将数据读出LPM-FIFO:键3置低电平(读允许);随着键8给出脉冲,观察数码管2/1显示的FIFO中输出的数据,与刚才写入的数据进行比较,同时注意数码4/3显示的地址数变化的顺序。

注,验证程序文件工程名是fifo2.bdf,下载fifo2.sof至实验台上的FPGA,选择实验电路模式为NO.0,按以上方式首先进行验证实验。

四.实验原理图

五.实验仿真波形图

WR为读写控制端,低电平时进行读操作,高电平时进行写操作;CLK 为读/写时钟脉冲;CLR为FIFO中数据异步清零信号;D为lpm_fifo的8位数据输入端;Q 为lpm_fifo的8位数据输出端; U为表示lpm_fifo已经使用的地址空间。

WR高电平时,允许写操作,将D数据写入,WR低电平时,允许读操作,将写入的D数据读出,Q为数据输出,按照先进先出的顺序读出。在写入时,已使用的地址空间依次增加,在读出时,已使用的地址空间依次减少。