8位移位寄存器

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY shifter IS PORT ( data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入的数据 n : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位的数量

dir : IN STD_LOGIC; --移动的方向 0:左 1:右 kind : IN STD_LOGIC_VECTOR(1 DOWNTO 0); --移动类型 00:算术移 01:逻辑移 10:循环移

clock : IN BIT; --手动时钟PULSE

data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --移位的结果

); END shifter;

ARCHITECTURE behav of shifter IS BEGIN

PROCESS (data_in, n, dir, kind) VARIABLE x,y : STD_LOGIC_VECTOR(7 DOWNTO 0);

VARIABLE ctrl0,ctrl1,ctrl2 : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN

IF (clock'EVENT AND clock = '1')THEN --产生控制向量ctrl

ctrl0 := n(0) & dir & kind(1) & kind(0); ctrl1 := n(1) & dir & kind(1) & kind(0); ctrl2 := n(2) & dir & kind(1) & kind(0);

CASE ctrl0 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => x := data_in; --n=0时不移动 WHEN --算术左移1位 WHEN --逻辑左移1位 WHEN --循环左移1位 WHEN --算术右移1位 WHEN

"1000" "1001" "1010" "1100" "1101"

=> => => => =>

x x x x x

:= data_in(6 :=

DOWNTO 0) & 0) &

data_in(0); &

data_in(6 DOWNTO

0)

'0';

:= :=

data_in(6 data_in(7) :=

'0'

DOWNTO & &

data_in(7);

data_in(7 data_in(7

DOWNTO DOWNTO

1);

1);

--逻辑右移1位

WHEN

--循环右移1位 "1110" => x := data_in(0) & data_in(7 DOWNTO 1);

WHEN others => null;

END CASE;

CASE ctrl1 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => y := x;

--n=0时不移动

WHEN

--算术左移2位 "1000" => y := x(5 DOWNTO 0) & x(0) & x(0);

WHEN "1001" => y := x(5 DOWNTO 0) & "00"; --逻辑左移2位

WHEN "1010" => y := x(5 DOWNTO 0) & x(7 DOWNTO 6); --循环左移2位

WHEN

--算术右移2位

WHEN

--逻辑右移2位 "1100" "1101" => y := y x(7) := & "00" x(7) & & x(7 DOWNTO DOWNTO 2); => x(7 2);

WHEN "1110" => y := x(1 DOWNTO 0) & x(7 DOWNTO 2); --循环右移2位

WHEN others => null;

END CASE;

CASE ctrl2 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => data_out <= y;

--n=0时不移动

WHEN "1000" => data_out <= y(3 DOWNTO 0) & y(0) & y(0) & y(0) & y(0);

--算术左移4位

WHEN

--逻辑左移4位 "1001" => data_out <= y(3 DOWNTO 0) & "0000";

WHEN "1010" | "1110" => data_out <= y(3 DOWNTO 0) & y(7 DOWNTO 4); --循环左(右)移4位

WHEN "1100" => data_out <= y(7) & y(7) & y(7) & y(7) & y(7 DOWNTO 4);

--算术右移4位

WHEN "1101"

--逻辑右移4位 => data_out <= "0000" & y(7 DOWNTO 4);

WHEN others => null;

END CASE;

END IF;

END PROCESS;

END behav;

第二篇:带清零的8位并行输入串行输出移位寄存器

四川大学锦江学院

四川大学锦江学院

EDA实验

学号: 080611044

班级: 08电工1班

姓名: 杨 洁

摘要

EDA作为电子工程领域的一个新领域,极大的提高了电子系统设计的效率和可靠性,本次设计是利用VHDL语言仿真设计具有八位并行输入串行输出功能的寄存器。

关键词:EDA,VHDL,并行输入串行输出

目录

(一) 选题 …………………………………………………(3)

(二) 芯片设计要求 ………………………………………… .(3).

(三) 引脚定义 ………………………………………………(3)

(四) VHDL源程序设计过程………………………………… (3)

(五) 设计的调试过程…………………………………………(5)

(六) 心得体会…………………………………………………(6)

(七) 参考资料………………………………………………… (6)

(八) 附录 ………………………………………………………(7)

(一)选题:带清零的8位并行输入串行输出移位寄存器

并行与串行通信各有特点,并行速度相对较快,但成本较串行高,在一个系统中有些模块对速度要求高,相对而言有的对速度并没有过高的期望。所以在一个系统可以进行串并或并串变换。在此仅以八位并串变换为例

(二)芯片设计要求

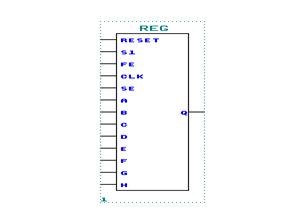

引脚:八个并行输入端口

一个输出端口

时钟信号控制引脚 时钟信号禁止端 移位装载控制 复位

功能:数据并行的输入,串行的输出 实现所谓的并串变化

(三)引脚定义

输入引脚 :a,b,c,d,e,f,g,h 8位并行输入信号

se 串行输入信号

输出引脚:q 串行输出信号

控制引脚: clk 时钟信号

fe 时钟信号禁止端

s1 移位装载控制端

reset 复位信号

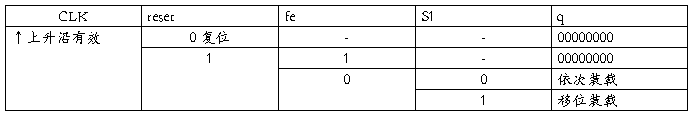

控制信号功能表

(四)VHDL源程序设计过程

包括三个部分,即库和程序包调用、实体部分、结构体部分

程序包调用:LIBRARY ieee;

use ieee.std_logic_1164.all;

实体部分一般格式:

entity 实体名is

类型参数说明

端口说明

end 实体名

注意:实体名与保存的源文件名相同

结构体部分一般格式:

Architecture 结构体名 of 实体名 is

定义语句

Begin

并行处理语句

End结构体名

(五)设计的调试过程

1.创建工程准备工作

新建一个文件夹(文件名不要用汉字)

输入源程序代码 (保存为”实体名.vhd”)

文件存盘

2. 创建工程

打开源程序;

设置为当前工程File->Project->Set Project to Current File

3. 编译前设置

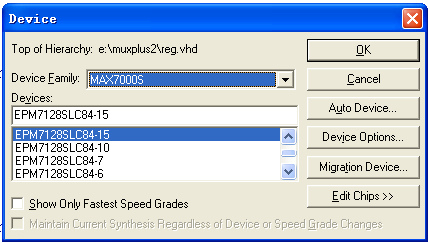

选择FPGA芯片 Assign->Device

4. 全部编译 MAX+plus2->Compiler 直到无错误为止

5. 引脚锁定

选择MAX+plus2->Floorplan Editor打开底层编辑器;

运行Layout->Last Compilation Floorplan,即可显示上次编译所得引脚分配情况。

Layout->Current Compilation Floorplan,可以在Unassigned Nodes&Pin 栏中手动设置各引脚。.

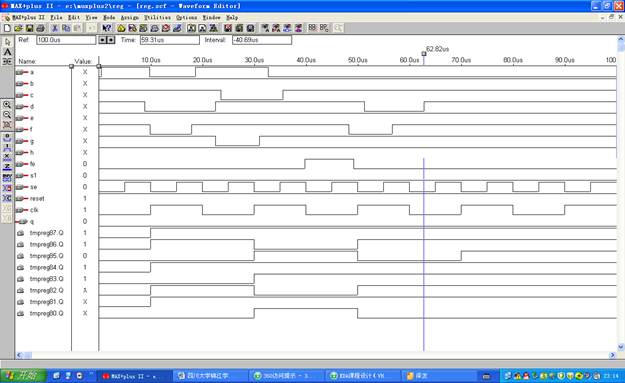

6.波形仿真

MAX+plus2->Waveform Editor

Node->Enter Nodes from SNF

End time =100us Grid size=10ns

设定并行输入值 控制引脚 并保存

7. MAX+plus2->Simulator 仿真图

8.创建器件 File->Create Default Symbol

(六)心得体会

对于这次实验由于以前做做关于VHDL语言实验,所以有软件的使用上还算好,但做起来还是有一些小问题,看似很简单的一个设计,动手做起来却有很多问题需要注意,最后查阅一些资料才解决。

在做实验之前,一定要先理清思路,明确实验要求,查阅相关的实验原理。最后确定实验方案。不能放过任何一个小细节。

在实验过程中,学会了对自己的实验进展、实验方法做自我监控,自我反馈和自我调节。

在实验的最后,学会了对实验结果进行自我检测,自我总结和自我评价与补救。

通过这次实验知道了再简单的东西都要自己亲身力行才能有收获。平时要多动手,勤思考,才能有进步。不懂没有关系,万事开头难,我们可以和同学讨论,上网搜索资料等等方式

(七)参考资料

【1】 赵刚 《EDA技术简明教程》 四川大学出版社

【2】杨颂华 冯毛官 <数字电子技术基础》 西安电子科技大学出版社

【3】《计算机虚拟实验讲义》电工电子基础实验中心 二〇##年九月

(八)附录:

LIBRARY ieee;

use ieee.std_logic_1164.all;

entity reg is

port(reset,s1,fe,clk,se,a,b,c,d,e,f,g,h:in std_logic;

q:out std_logic);

end reg;

architecture behave of reg is

signal tmpreg8:std_logic_vector(7 downto 0);

begin

process(clk,reset,s1,fe)

begin

if(reset='0') then

tmpreg8<="00000000";

q<=tmpreg8(7);

elsif(clk'event)and(clk='1')then

if(fe='0')then

if(s1='0')then

tmpreg8(0)<=a;

tmpreg8(1)<=b;

tmpreg8(2)<=c;

tmpreg8(3)<=d;

tmpreg8(4)<=e;

tmpreg8(5)<=f;

tmpreg8(6)<=g;

tmpreg8(7)<=h;

elsif(s1='1')then

for i in tmpreg8'high downto tmpreg8'low+1 loop

tmpreg8(i)<=tmpreg8(i-1);

end loop;

tmpreg8(tmpreg8'low)<=se;

q<=tmpreg8(7);

end if;

end if;

end if;

end process;

end behave;