第二篇:EDA实验报告 (5)

试验七 VHDL有限状态机设计

一 实验目的:

本次试验是一个设计型试验,参照给出的状态转移图,利用VHDL描述进行状态机设计。通过本次试验,使学生深入理解状态机的VHDL描述的固定语句表达方法,掌握状态机设计的状态说明方法、主控时序进程和主控组合进程的功能及实现方法。

二 实验仪器:

1、PC机一台

2、QUARTUS2软件

三 实验原理:

根据给出的状态转换图,编写VHDL程序并且进行编译和仿真。

图表 1实验原理图

四 实验步骤(自行给出详细步骤):

1 编辑VHDL语言程序

library ieee;

use ieee.std_logic_1164.all;

entity xc is

port(input:in std_logic;

reset:in std_logic;

clk:in std_logic;

y:out std_logic_vector(1 downto 0));

end xc;

architecture behav of xc is

type state_type is(s0,s1,s2,s3);

signal present_state,next_state:state_type; begin

process(reset,clk)

begin

if(reset='1') then

present_state<=s0;

elsif(clk'event and clk='1') then present_state<=next_state;

end if;

end process;

process(present_state,next_state,input) begin

case present_state is

when s0=>if(input='1') then next_state<=s1; else

next_state<=s0; end if;

y<="00";

when s1=>if(input='0') then

next_state<=s2;

else next_state<=s1; end if; y<="01";

when s2=>if(input='1') then

next_state<=s3; else

next_state<=s2; end if;

y<="10";

when s3=>if(input='0') then

next_state<=s0; else

next_state<=s3; end if;

y<="11";

end case;

end process;

end behav;

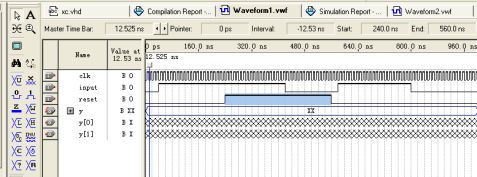

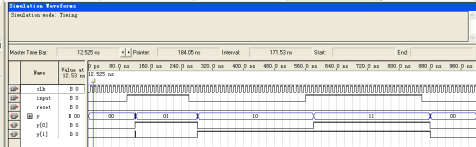

2 编译并进行波形仿真:

仿真结果:

五 实验总结:

实验完成良好,就是到后面仿真的时候付值出现了问题。使得实验得不到良好的仿真结果,经老师说教后再向同学了解讨论后得出了比较看得过去的仿真结果图!!

实验过程中暴露了很多的问题,究其原因还是对课本的不熟悉,对编程的不掌握。下课要多多看书!!