信 息 工 程 学 院

数字逻辑与数字系统 实习报告

学院:信息工程学院 班级:信息103 姓名:张丽玲 学号:2010013077 成绩:

实验五 J-K触发器

一、 实验目的

1.掌握J-K触发器的逻辑功能;

2.掌握集成J-K触发器逻辑功能的测试方法;

3.掌握不同逻辑功能触发器之间的相互转换方法。

二、实验预习要求

1.复习J-K触发器的逻辑功能;

2.掌握D触发器和J-K触发器的真值表及其转换的基本方法。

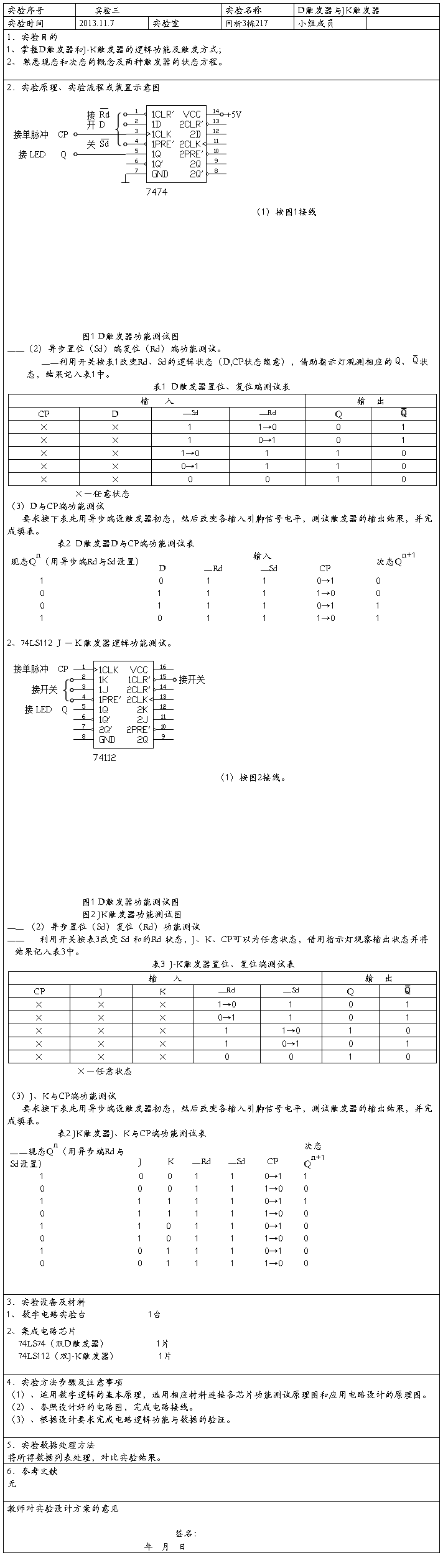

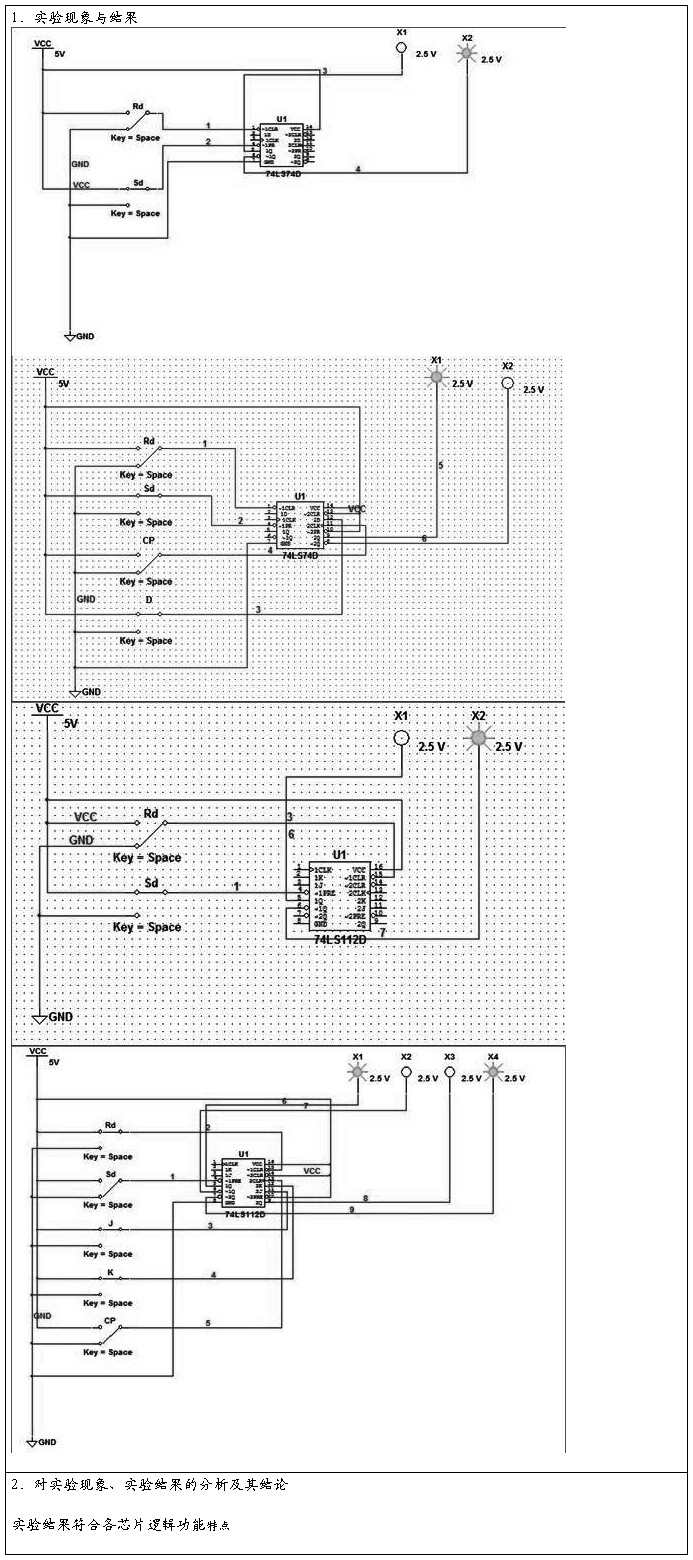

三、实验原理

1.J-K触发器

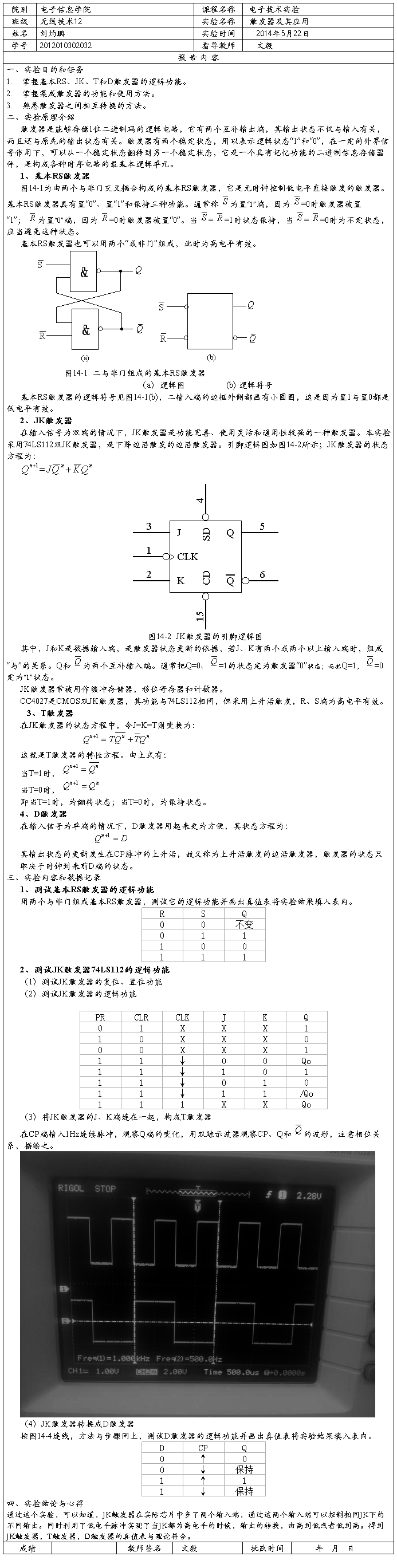

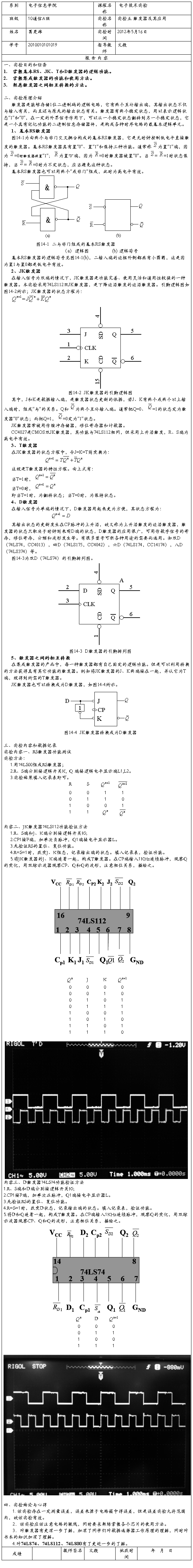

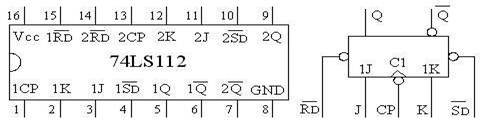

本实验中采用的74LS112为下降沿触发的边沿触发器。其状态方程为:

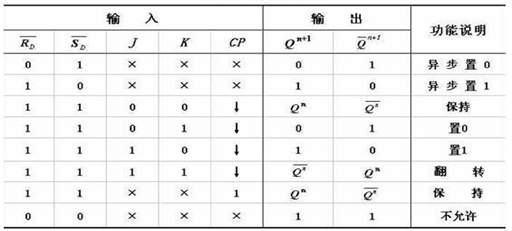

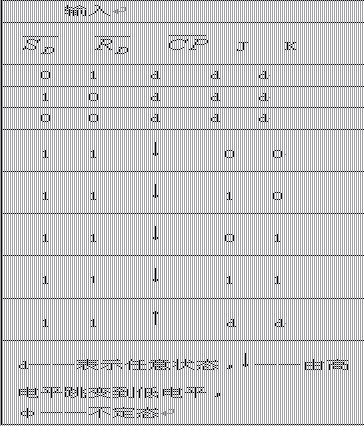

其中J和K 为数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“逻辑与”的关系。触发器的功能表如表实所示。

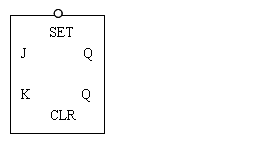

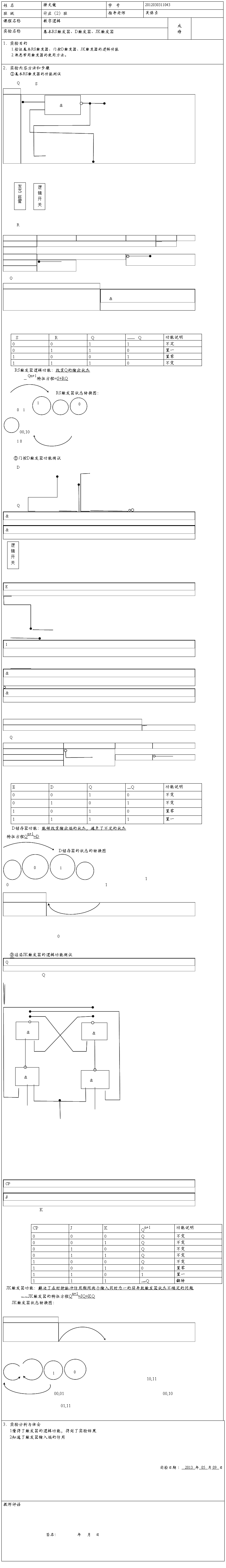

2.触发器功能转换

在集成触发器的产品中,每一种触发器都有自己固定的逻辑功能。但可以利用转换的方法获得具有其它功能的触发器。例如将J-K触发器转换成D触发器、T触发器、Tˊ触发器。其转换电路如图所示。

(a) J-K转换成D (b) J-K转换成T (c) J-K转换成Tˊ

J-K触发器转换成D、T、Tˊ触发器

四、实验仪器设备

1. TPE-AD数字电路实验箱1台

2. 双J-K触发器74LS112(或CC4027)1片

3. 四两输入与非门74LS00(或CC4011)1片

五、实验内容及方法

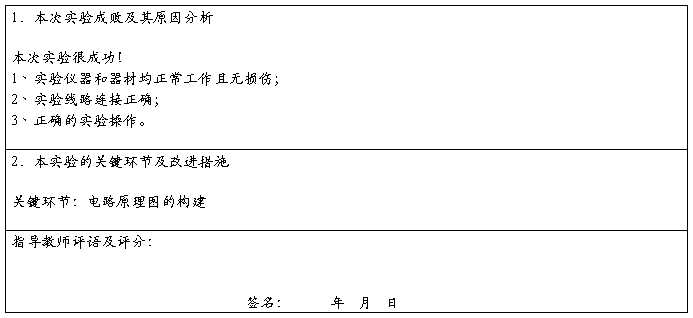

测试并掌握JK触发器74LS112逻辑功能及应用。

1. 测试 的复位、置位功能

将J、K端接逻辑开关输出插口,CP端接单脉冲,Q 、/Q 端接至逻辑电平显示灯接口。在RD?0,SD?1或RD?1,SD?0的作用期间记录J、K及CP的状态,观察Q 、/Q 状态并记录。

2. 测试J-K触发器的逻辑功能

按表实验5.1的要求改变J、K、CP的状态,观察Q、/Q状态变化,观察Q端的状态更新是否发生在CP脉冲的下降沿(即CP由1→0),并记录之。

…… …… 余下全文

异步置位端PRN

异步置位端PRN

J端 输出端Q

J端 输出端Q

CP端

CP端

K端

K端

为置“1”段,因为

为置“1”段,因为 =0(

=0( =1)时触发器被置为“1”;

=1)时触发器被置为“1”; 为置“0”端,因为

为置“0”端,因为

=J

=J +

+

和

和