单片机原理及应用设计报告

题 目 电子时钟的设计

专 业 物理学

院 部 物理与电子工程学院

学 号 -----------

姓 名 -----------

指 导 教 师 -----------

…… …… 余下全文

单片机原理及应用设计报告

题 目 电子时钟的设计

专 业 物理学

院 部 物理与电子工程学院

学 号 -----------

姓 名 -----------

指 导 教 师 -----------

…… …… 余下全文

目 录

一、设计目的、意义 …………………………………………………1

二、设计内容 …………………………………………………………1

1总体设计方案简介 ………………………………………………1

2单元电路设计 ……………………………………………………2

3总电路图 …………………………………………………………6

4仿真结果 …………………………………………………………7

三、结果分析……………………………………………………………8

四、设计总结……………………………………………………………8

五、设计心得……………………………………………………………9

参考文献 ………………………………………………………………10

附录 ……………………………………………………………………11

一、设计目的、意义

1.巩固和加深对电子线路基本知识的理解,提高综合运用课程知识的能力。

2.培养学生根据课程需要自学参考书籍,查阅手册、图表和文献资料的能力。

3.通过实际电路方案的分析比较、设计计算、元件选取、安装调试等环节,初步掌握简单实用电路的分析方法和工程设计方法。

4.掌握常用仪器设备的正确使用方法,学会简单电路的调试和整机指标测试方法,提高动手能力。

5.了解与课程有关的电子线路及元器件工程技术规范,按课程设计任务书的要求编写设计说明书,能正确反映设计的实验结果,能正确绘制电路图。

二、设计内容

1.总体设计方案简介

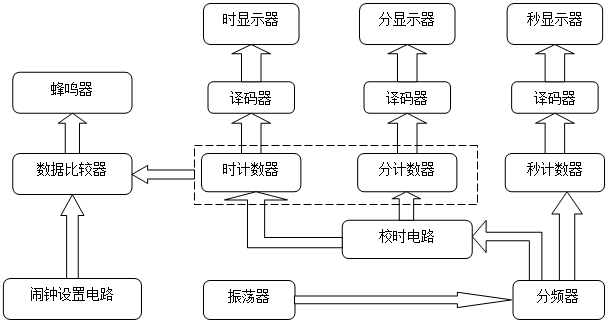

电路总体框图如图2.1所示:

电路总体框图如图2.1所示:

图2.1 数字钟原理框图

电路由振荡器、分频器、“时” “分” “秒”对应的计数器、译码显示器、校时电路、整点报时电路和闹钟电路等构成。

电路的工作原理是:振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲。秒计数器计满60后向分计数器进位,分计数器计满60后向时计数器进位,时计数器设置成24进制计数器。计数器的输出送译码显示器显示。计时出现误差时可以用校时电路进行校时、校分、校秒。由分计数器、秒计数器的结果控制整点报时电路。当时计数器、分计数器计数到与闹钟设置电路设置的时间相同时实现闹钟功能,蜂鸣器响一分钟。

…… …… 余下全文

课程设计报告

设计题目: 电子时钟设计

指导教师:

姓 名:

学 号:

班 级:

专 业:

日 期: 20**-1-5

控制电路的C语言源程序 10

单片机电子时钟

摘要:单片机 即单片微型计算机。(Single-Chip Microcomputer ),是 集 CPU ,RAM ,ROM ,定时,计数和多种接口于一体的微控制器。他体积小,成本低,功能强,广泛应用于工业自动化上和智能产品。时钟,自从它被发明的那天起,就成为了人类的好朋友,但随着时间的推移,科学技术的不断发展,时钟的应用越来越广范,人们对时间计量的精度要求也越来越高。怎样让时钟更好的为人民服务,怎样让我们的老朋友再次焕发青春呢?这就要求我们不断设计出新型的时钟,来不断满足人们的日常生活需要。然而市场上的时钟便宜的比较笨重,简单实用的又比较昂贵。那么,有没有一款既简单实用价格又便宜的时钟呢?

我们课程设计小组设想:可不可以利用单片机功能集成化高,价格又便宜的特点设计一款结构既简单,价格又便宜的单片机电子时钟呢?

基于这种情况,我们课程设计小组成员多方查阅资料,反复论证设计出了这款既简单实用,又价格便宜的——单片机电子时钟。

关键词:单片机 时钟 计时

第一章 系统设计要求

1.1 基本功能

(1)能够显示时分秒

(2)能够调整时分秒

1.2 扩展功能

(1)能够任意设置定时时间

(2)定时时间到闹铃能够报警

(3)实现了秒表功能

第二章 硬件总体设计方案

本次设计时钟电路,使用了STC89C51单片机芯片控制电路,单片机控制电路简单且省去了很多复杂的线路,使得电路简明易懂,使用键盘键上的按键来调整时钟的时、分、秒,用一扬声器来进行定时提醒,同时使用C语言程序来控制整个时钟显示,使得编程变得更容易,这样通过四个模块:键盘、芯片、扬声器、显示屏即可满足设计要求。

2.1系统功能实现总体设计思路

…… …… 余下全文

期末大作业课程设计实验报告

设计题目:基于VHDL电子钟的设计

目录

一、 概述…………………………………………………………3

1.1目的……………………………………………………………3

1.2课程设计的要求和功能………………………………………3

二、总结…………………………………………………………..3

2.1课程设计进行过程及步骤……………………………………3

2.2所遇到的问题,如何解决问题……………………………….15

2.3体会收获以及建议…………………………………………….15

3.4参考资料(书,网络资料)………………………………….15

三、教师评语………………………………………………………16

四、成绩……………………………………………………………16

一、 概述

1.1目的

1. 基于CPLD系统模块板,设计一个电子钟。来熟悉CPLD的工作原理以及对VHDL的使用。

2. 通过设计出一个电子钟具有校时功能,来巩固分频,键盘扫描,计数,动态扫描等知识内容。

1.2课程设计的要求和功能

设计一个电子钟,能进行正常的时分秒计时功能,分别有六个数码管显示24小时,60分钟,60秒的计数器显示。

利用实验箱系统上的按键实现“校时”、“校分”功能:

(1)按下“SA”键时,计时器快速递增,按24小时循环,进行时校正;

(2)按下“SB”键时,计分器快速递增,按60分循环,进行分校正

(3)按下“SC”键时,秒清零,进行秒校正;

二、总结

2.1课程设计进行及步骤

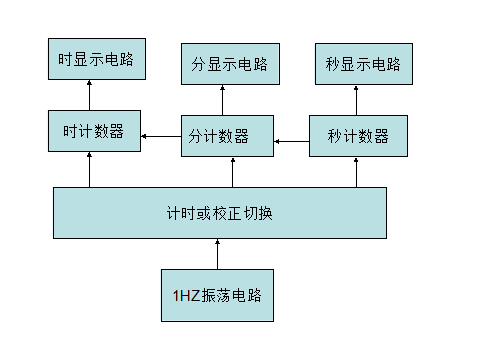

1.设计提示

系统框图见下

…… …… 余下全文

实 验 报 告

实验课程名称 近代电子学实验

实验项目名称 多功能数字电子钟

年 级

专 业

学生姓名

学 号

理 学 院

实验时间: 2012 年 9月 15 日

近代电子学实验报告

实验名称:多功能数字电子钟

设计内容及要求:

实验任务:设计并制作一个数字电子钟。

基本要求:①准确计时,以数字形式显示时、分、秒的时间。②小时为24进制,分和秒为60进制。③具有校时电路。

扩展功能:①定时控制。②整点报时。③仿电台整点报时。④报整点时数。 实验条件:用面包板组建实际电路

实验时间:20xx年9月29日至20xx年10月13日

实验地点:博学楼513S

使用仪器及元器件:面包板(1块),七段共阳数码管(6个),74LS47(6片),74LS90(6片),74LS20(1片),74LS00(4片),74LS08(1片),74LS74(1片),4060(1片),电阻(100欧/6个,3.3k欧/2个,1k欧/2个,1M欧/1个,27欧/1个),电容(51pF/2个),晶振(32768Hz/1个),LED(2个),电平开关(8控/1个),晶体管(9014/1个),扬声器/蜂鸣器(1个),导线(若干)

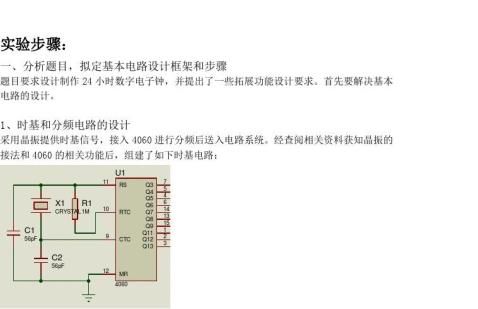

时基和分频电路

由于4060为2^14分频器,其7,5,4,6,14,13,15,1,2,3管脚分别对应2^5,2^6,2^7,2^8,2^9, 2^10,2^11,2^12,2^13,2^14分频信号,此处选择32768Hz的晶振,故由4060的7脚可得1024Hz信号,由5脚可得512Hz信号,由3脚可得2Hz信号。考虑到电路系统需使用1Hz

的信号,故在4060后增加一个T’触发器(由D触发器改装)。而校时信号频率不宜选择过大(不易控制进行校时),也不宜选择过小(校时周期太长),且前面已经使用了一块74LS74,其中有一个D触发器还处于闲置状态,故将1Hz信号接入下一个T’触发器(由D触发器改装)获得0.5Hz信号,并选择了0.5Hz的信号作为校时信号。

…… …… 余下全文

华大计科学院

数字逻辑课程设计说明书

题目: 多功能数字钟

专业: 计算机科学与技术

班级: 网络工程1班

***

学号: ****

完成日期: 20XX-9

一、设计题目与要求

设计题目:多功能数字钟

设计要求:

1.准确计时,以数字形式显示时、分、秒的时间。

2.小时的计时可以为“12翻1”或“23翻0”的形式。

3.可以进行时、分、秒时间的校正。

二、设计原理及其框图

1.数字钟的构成

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路。图 1 所示为数字钟的一般构成框图。

图1 数字电子时钟方案框图

⑴多谐振荡器电路

多谐振荡器电路给数字钟提供一个频率1Hz 的信号,可保证数字钟的走时准确及稳定。

⑵时间计数器电路

时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成。其中秒个位和秒十位计数器、分个位和分十位计数器为60 进制计数器。而根据设计要求,时个位和时十位计数器为24 进制计数器。

⑶译码驱动电路

译码驱动电路将计数器输出的8421BCD 码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

⑷数码管

数码管通常有发光二极管(LED)数码管和液晶(LCD)数码管。本设计提供的为LED数码管。

2.数字钟的工作原理

⑴多谐振荡器电路

555 定时器与电阻R1、R2,电容C1、C2 构成一个多谐振荡器,利用电容的充放电来调节输出V0,产生矩形脉冲波作为时钟信号,因为是数字钟,所以应选择的电阻电容值使频率为1HZ。

⑵时间计数单元

六片74LS90 芯片构成计数电路,按时间进制从右到左构成从低位向高位的进位电路,并通过译码显示。在六位LED 七段显示起上显示对应的数值。

…… …… 余下全文

《开放创新实践1》报告

题 目: 数字电子钟

题 目: 数字电子钟

学 年: 20##-2015 学 期: 1

学 年: 20##-2015 学 期: 1

专 业:电子信息工程 班 级: 电子131

专 业:电子信息工程 班 级: 电子131

学 号:2011013958 姓 名:李佳斌

学 号:2011013958 姓 名:李佳斌

学 号:2011011391 姓 名:陈锦锋

学 号:2011011391 姓 名:陈锦锋

指导教师: 王 阳

指导教师: 王 阳

时 间:2014年12 月21日~ 2015年1 月4 日

浙江万里学院电子信息学院

一、设计要求和指标

1、用24小时小时制进行时间显示。

2、能显示时、分、秒。

3、校时功能(2HZ信号调时)。

4、整点报时(发生在00时00分),红灯亮5秒。

…… …… 余下全文