实验四 数字钟设计

一、实验目的

1) 进一步学习更复杂的EDA熟练项目设计,更的掌握VHDL语言设计。

2) 学习动态数码管的VHDL编程。

3) 更加熟练计时显示、进位和校时的编程方法。

二、实验内容与要求

1、在实验箱上实现动态扫描数码管显示时分秒;

2、可以预置为12小时计时显示和24小时计时显示;

3、一个调节键,用于调节目标数位的数字。对调节的内容敏感,如调节分钟或秒时,保持按下时自动计数,否则以脉冲计数;

4、一个功能键,用于切换不同状态:计时、调时、调分、调秒。

三、设计思路

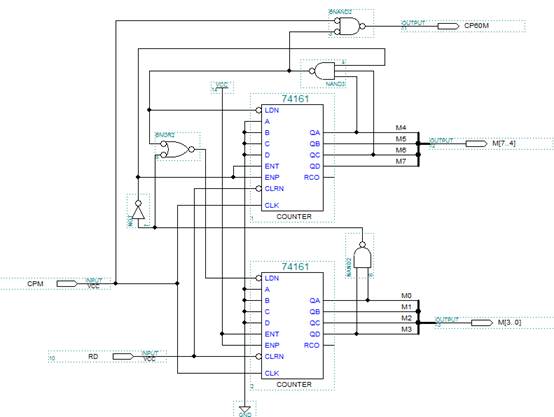

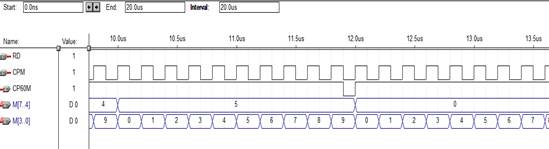

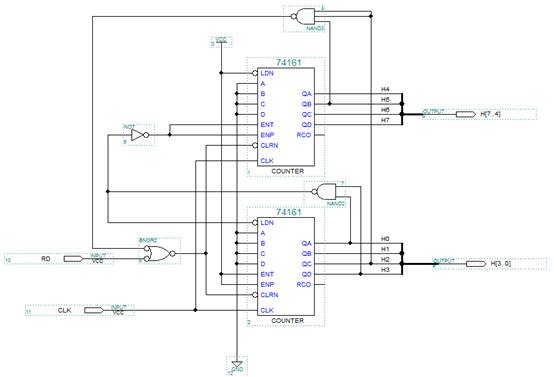

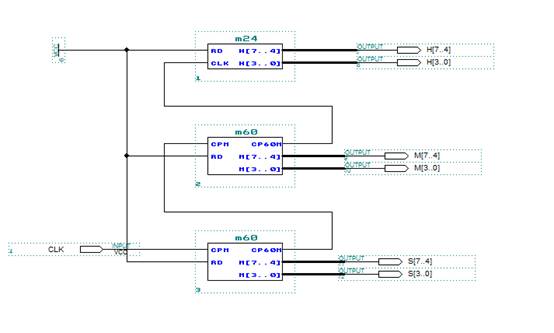

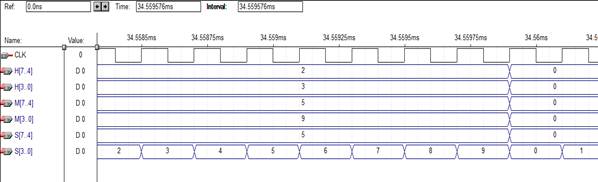

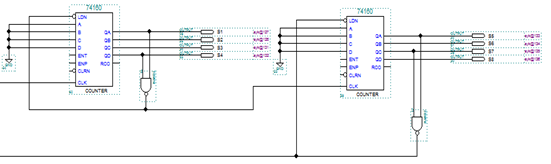

首先设计分和秒的计时模块,由于分和秒都是模六十计数,输出都设计有一个进位,当计时到59后又从零开始计数,此时进位输出由零变为1,进位端形成一个上升沿作为下一模块的计数脉冲,所以秒模块的进位用来作为分模块的计数脉冲,分模块的计数模块用来作为时模块的计数脉冲。小时计数计数模块设置一个控制端用来控制模24和模12计数。此外设计一个校时控制模块,输入端分别为秒、时、分的手动控制计数端和正常计数时的各计时模块的计时脉冲,以及一个控制端控制正常计时和校时。最后设计一个动态扫描模块,用来动态显示时间。由于实际实验箱最小频率脉冲为2HZ,因此需要设计一个二分频的模块用来得到1HZ秒计时模块。

四、实验程序(程序来源:独立设计编写)

二分频模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY div2 IS

…… …… 余下全文

南昌大学实验报告

南昌大学实验报告