实验五 D触发器及其应用

实验人员: 班号: 学号:

一、实验目的

1、熟悉D触发器的逻辑功能;

2、掌握用D触发器构成分频器的方法;

3、掌握简单时序逻辑电路的设计

二、实验设备

74LS00 ,74LS74,数字电路实验箱,数字双踪示波器,函数信号发生器

三、实验内容

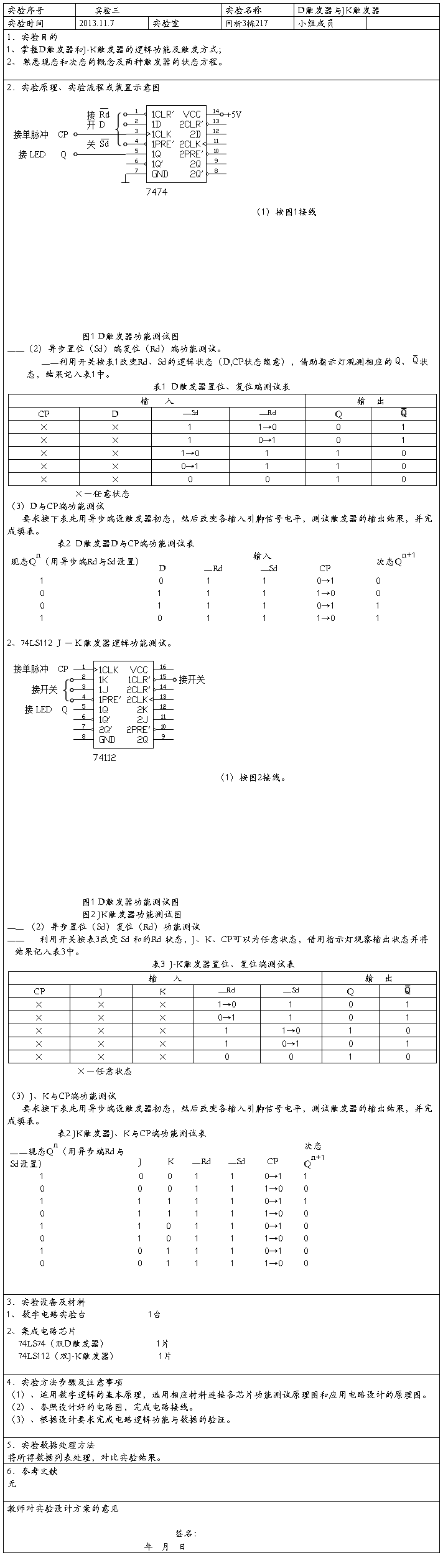

1、用74LS74(1片)构成二分频器、四分频器,并用示波器观察波形;

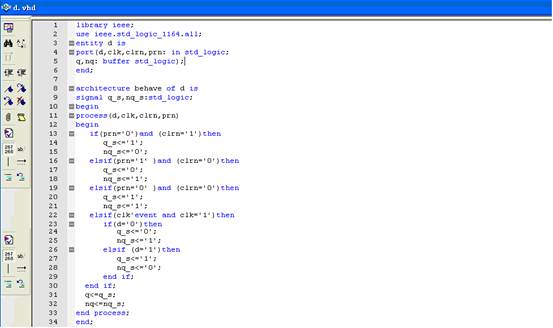

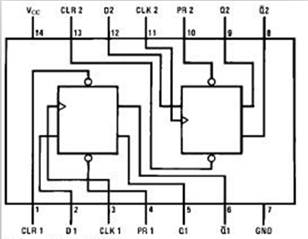

74LS74是双D触发器(上升沿触发的边沿D触发器),其管脚图如下:

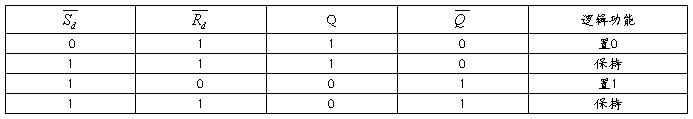

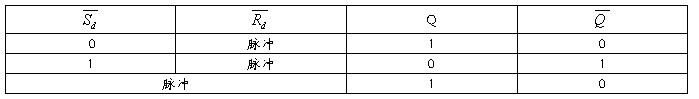

其功能表如下:

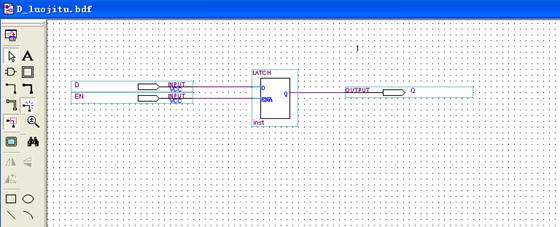

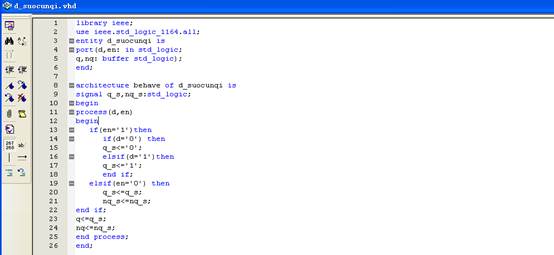

1构成二分频器:用一片74LS74即可构成二分频器。实验电路图如下:

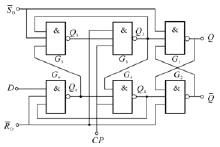

2构成四分频器:需要用到两片74LS74。实验电路图如下:

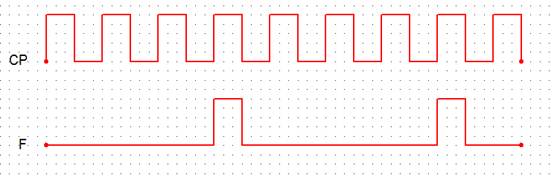

2、实现如图所示时序脉冲 ( 用74LS74和74LS00各1片来实现)

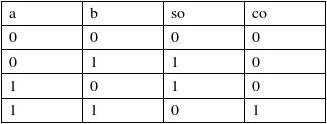

将欲实现功能列出真值表如下:

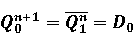

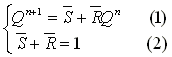

通过观察上面的真值表,可以得出下面的表达式:

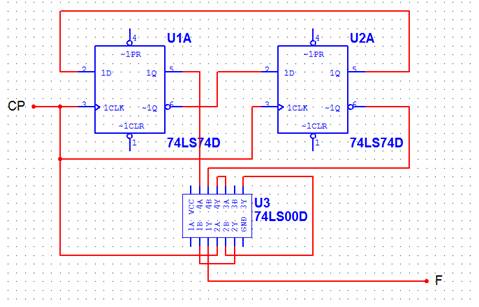

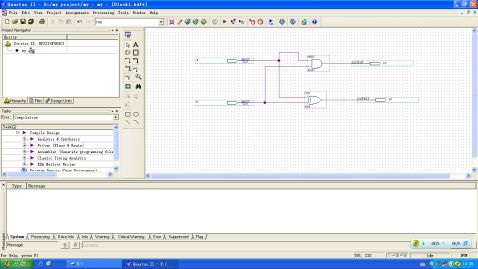

连接电路图如下:

四、实验结果

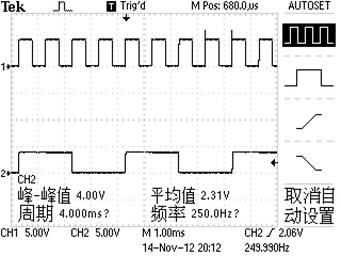

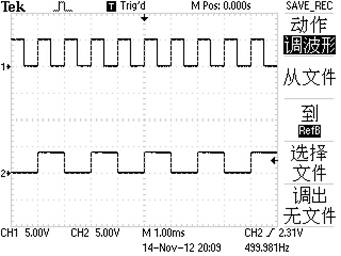

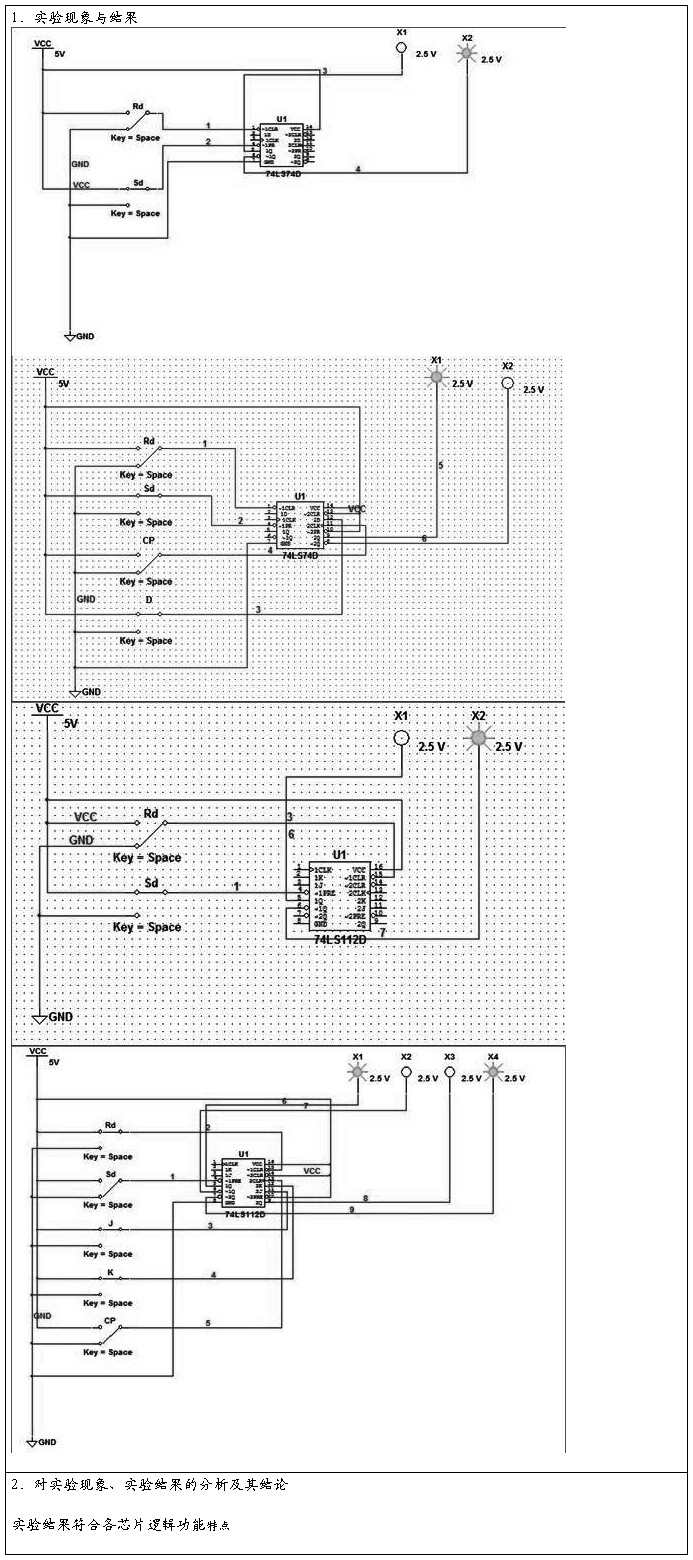

1、用74LS74(1片)构成二分频器、四分频器。示波器显示波形如下:

1二分频器:

2四分频器:

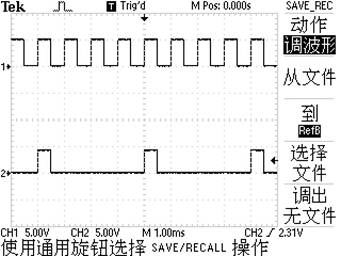

2、实现时序脉冲。示波器显示波形如下:

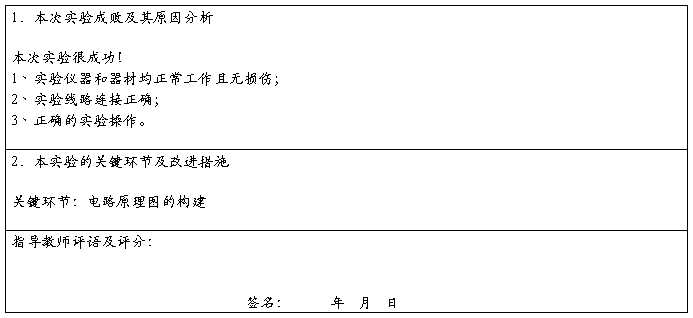

五、故障排除

在做“用74LS74(1片)构成二分频器、四分频器”时,连接上示波器后,发现通道二总显示的是类似于电容放电的波形,但表现出了二分频。反复排查问题均没有发现原因。最后换了一根连接示波器的线,便得到了理想的结果。

…… …… 余下全文

1、双踪示波器

1、双踪示波器 、

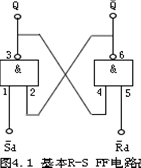

、 端加信号:

端加信号: 端的状态,将结果填入表4.1 中,并说明在上述各种输入状态下,

端的状态,将结果填入表4.1 中,并说明在上述各种输入状态下,