数字电子技术实验报告

实验四:计数器及其应用

一、实验目的:

1、熟悉常用中规模计数器的逻辑功能。

2、掌握二进制计数器和十进制计数器的工作原理和使用方法。

二、实验设备:

1、数字电路实验箱;

2、74LS90。

三、实验原理:

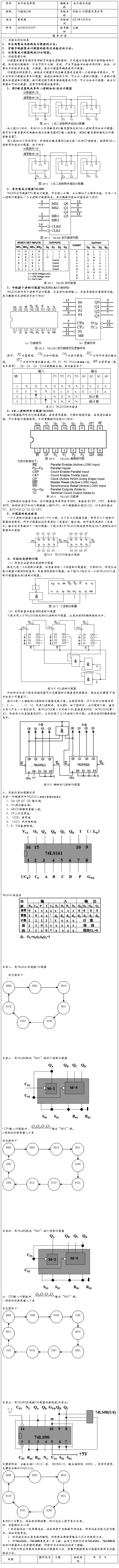

1、 计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时具有分频功能。计数器按计数进制分有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。

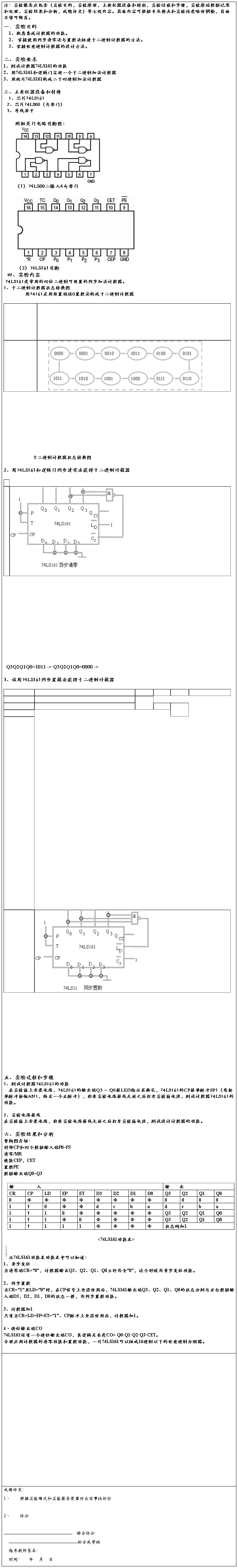

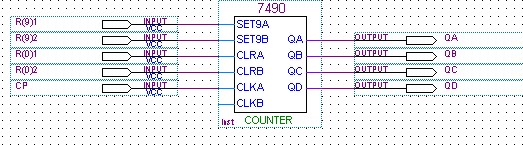

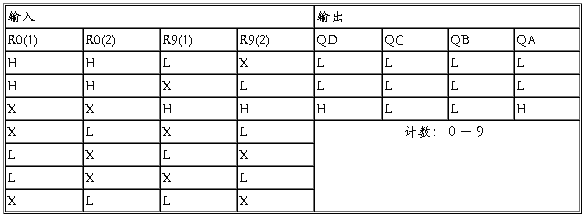

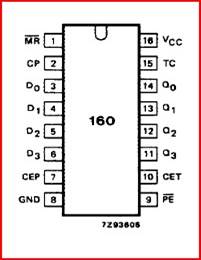

2、 74LS90是一块二-五-十进制异步计数器,外形为双列直插,NC表示空脚,不接线,它由四个主从JK触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器构成异步五进制计数器。在74LS90计数器电路中,设有专用置“0”端R0(1),R0(2)和置“9”端S9(1)S9(2)。。其中前两个为异步清0端,后两个为异步置9端。CP1, CP2为两个时钟输入端;Q0 ~Q3为计数输出端。当R1=R2=S1=S2=0时,时钟从CP1引入,Q0输出为二进制;从CP2引入,Q3输出为五进制。时钟从CP1引入,二Q0接CP1,则Q3Q2Q1Q0输出为十进制(8421码);时钟从CP2引入,而Q3接CP1,则Q0Q3Q2Q1输出为十进制(5421码)。

四、实验原理图及实验结果:

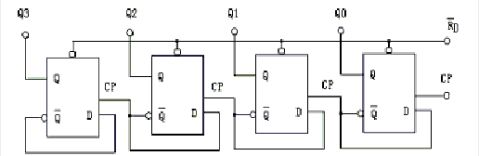

1、实现0~9十进制计数。

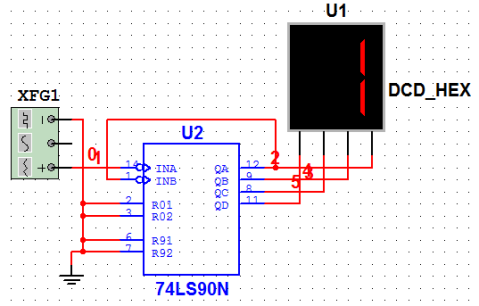

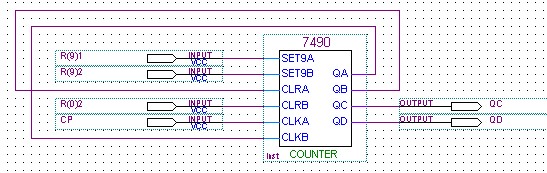

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)

2)实验结果:

解码器上依次显示0~9十个数字。

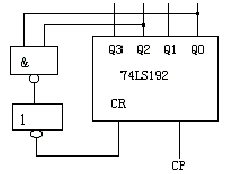

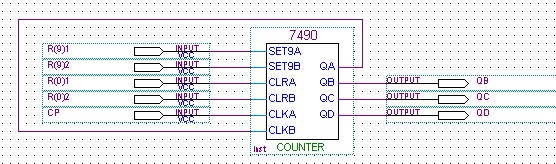

2、实现六进制计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)

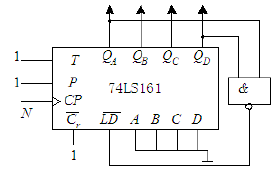

…… …… 余下全文

、

、 和置“9”端

和置“9”端 、

、 。其中

。其中 学院实验报告

学院实验报告 专业名称 软件工程

专业名称 软件工程