实验4 计数器及其应用

一、实验目的

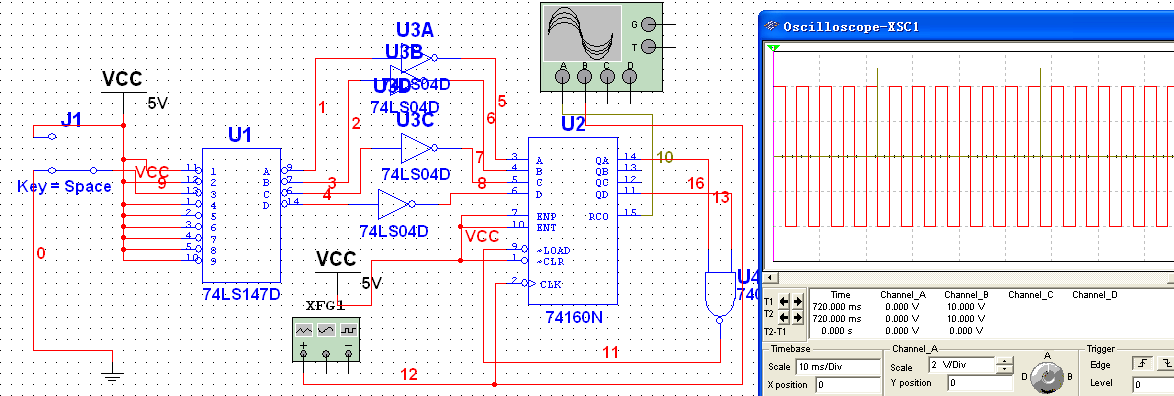

1、学习用集成触发器构成计数器的方法

2、掌握中规模集成计数器的使用及功能测试方法

二、实验原理

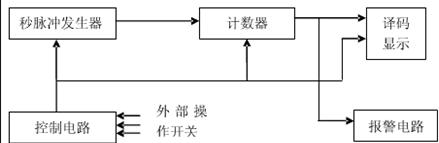

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等等。目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

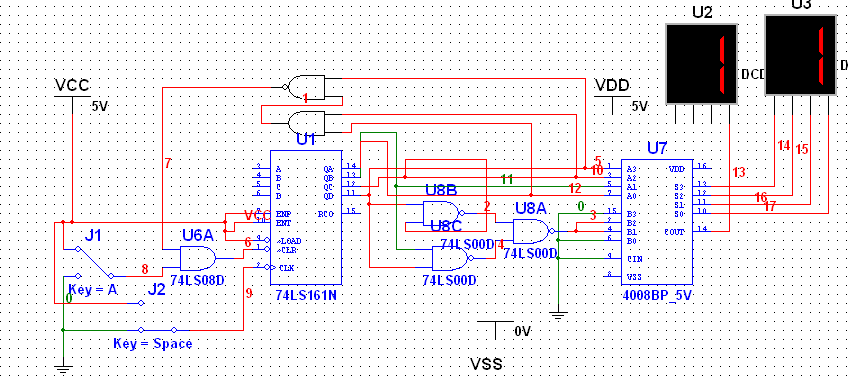

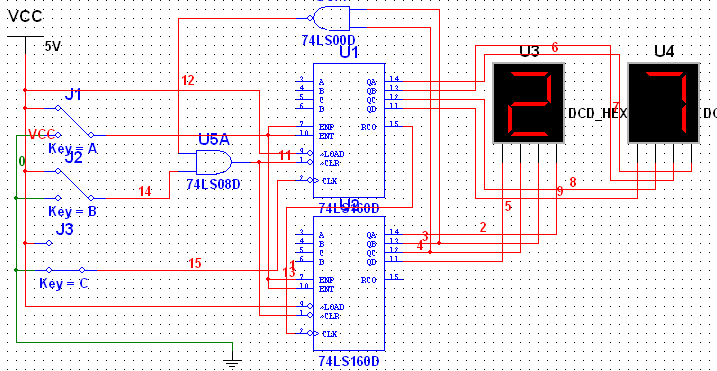

1、中规模十进制计数器

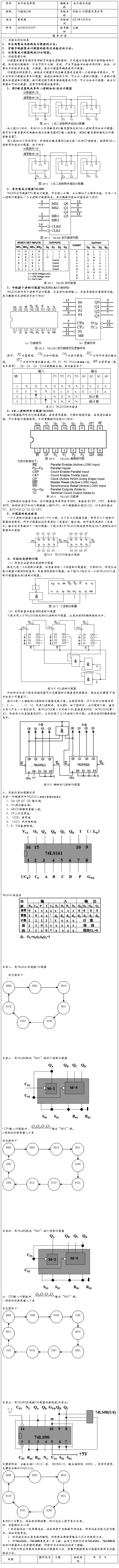

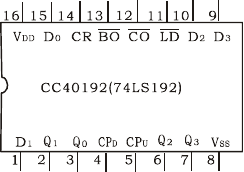

CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。

图5-9-1 CC40192引脚排列及逻辑符号

图中  —置数端 CPU—加计数端 CPD —减计数端

—置数端 CPU—加计数端 CPD —减计数端

—非同步进位输出端

—非同步进位输出端  —非同步借位输出端

—非同步借位输出端

D0、D1、D2、D3 —计数器输入端

Q0、Q1、Q2、Q3 —数据输出端 CR—清除端

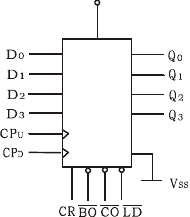

CC40192的功能如表5-9-1,说明如下:

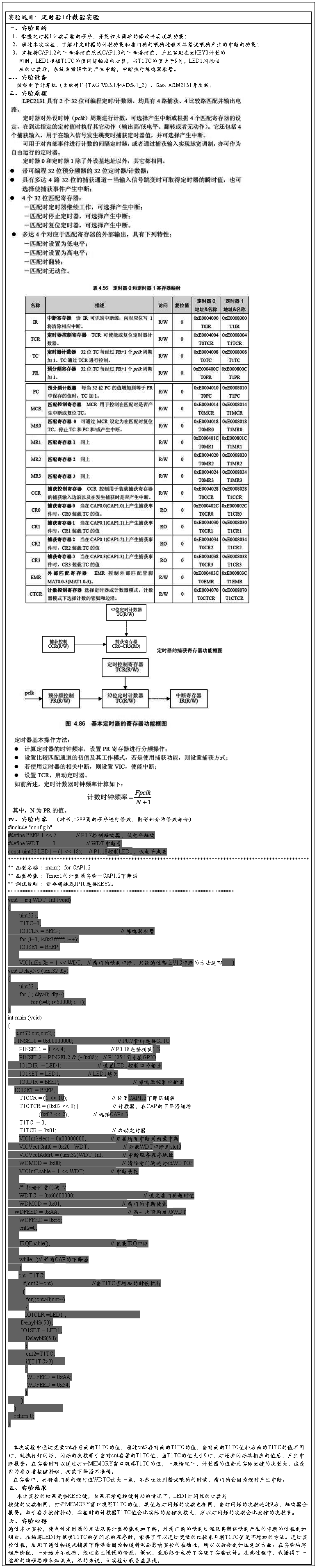

表5-9-1

当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端 也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

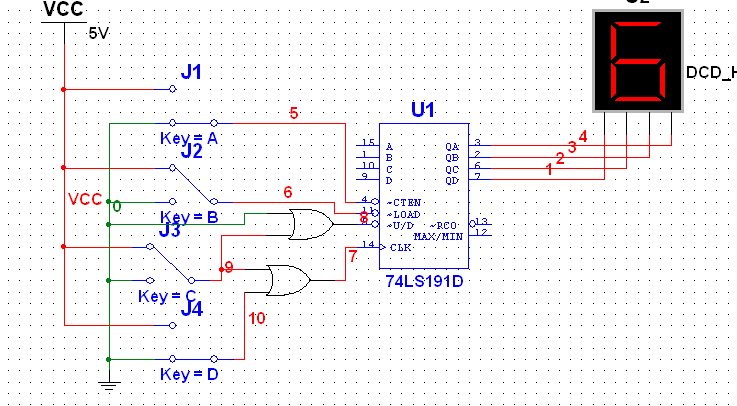

当CR为低电平, 为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421码十进制加、减计数器的状态转换表。

为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421码十进制加、减计数器的状态转换表。

…… …… 余下全文

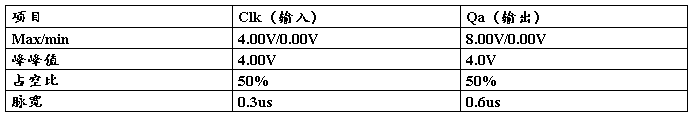

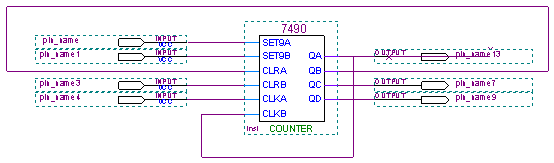

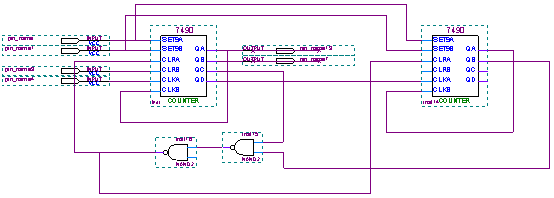

实验四:计数器的设计

实验四:计数器的设计

![文本框: [广东水利电力职业技术学院]](https://upload2.fanwen118.com/wk001/2616734/2616734_img_002.png)