实验报告

实验报告

课程名称:数字电子技术基础实验 指导老师:樊** 成绩:

实验名称:组合逻辑电路实验 实验类型:设计类 同组学生姓名:

一、实验目的和要求(必填) 二、实验内容和原理(必填)

三、主要仪器设备(必填) 四、操作方法和实验步骤

五、实验数据记录和处理 六、实验结果与分析(必填)

七、讨论、心得

一.实验目的

1.加深理解全加器和奇偶位判断电路等典型组合逻辑电路的工作原理。

2.熟悉74LS00、74LS11、74LS55等基本门电路的功能及其引脚。

3.掌握组合集成电路元件的功能检查方法。

4.掌握组合逻辑电路的功能测试方法及组合逻辑电路的设计方法。

二、主要仪器设备

74LS00(与非门) 74LS55(与或非门) 74LS11(与门) 导线 电源 数电综合实验箱

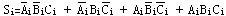

三、实验内容和原理及结果

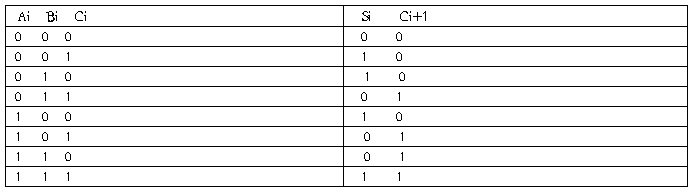

(一)一位全加器

实验原理:全加器实现一位二进制数的加法,输入有被加数、加数和来自相邻低位的进位;输出有全加和与向高位的进位。

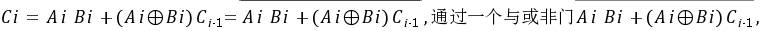

实验内容:用 74LS00与非门和 74LS55 与或非门设计一个一位全加器电路,并进行功能测试。

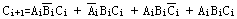

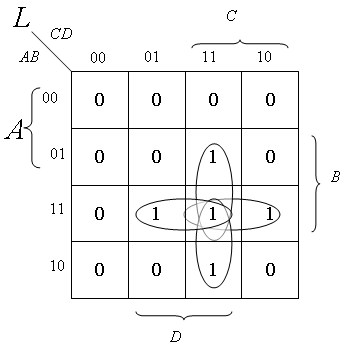

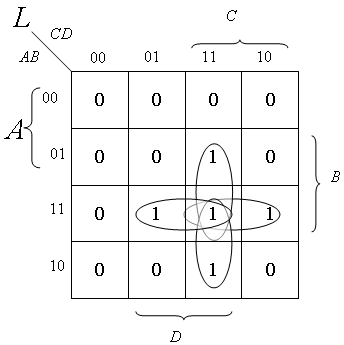

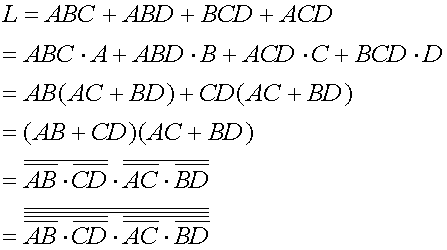

设计过程:首先列出真值表,画卡诺图,然后写出全加器的逻辑函数,函数如下:

异或门可通过

异或门可通过 即一个与非门(74LS00),一个与或非门(74LS55)来实现。

即一个与非门(74LS00),一个与或非门(74LS55)来实现。

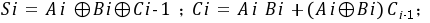

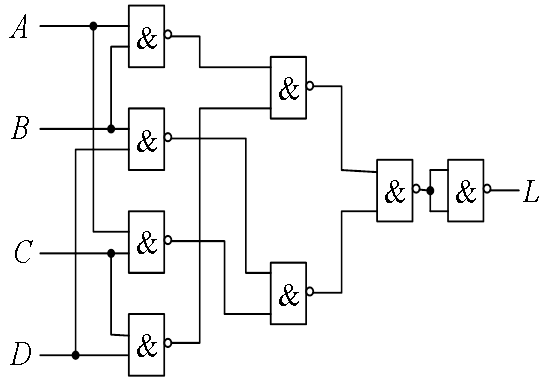

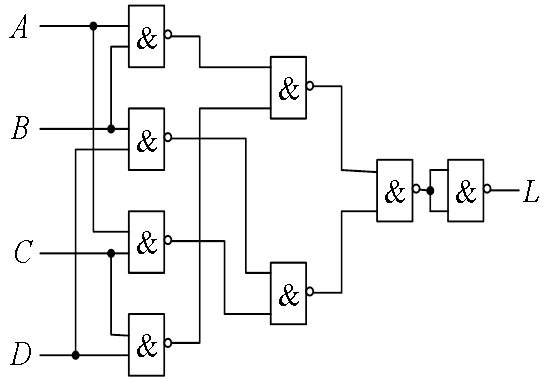

仿真与实验电路图:仿真与实验电路图如图 1 所示。

仿真与实验电路图:仿真与实验电路图如图 1 所示。

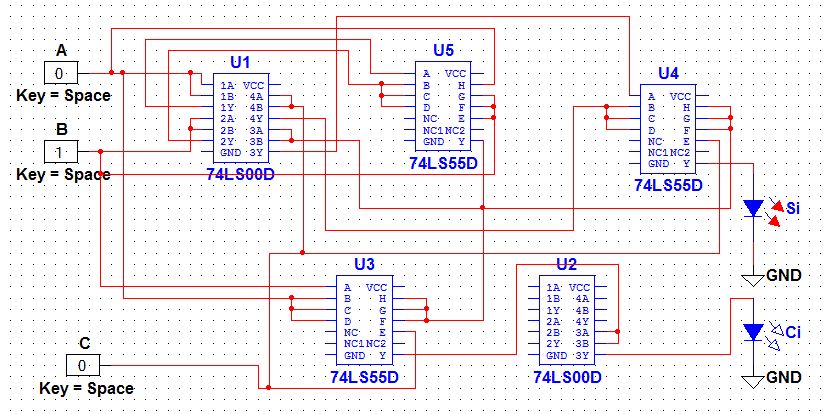

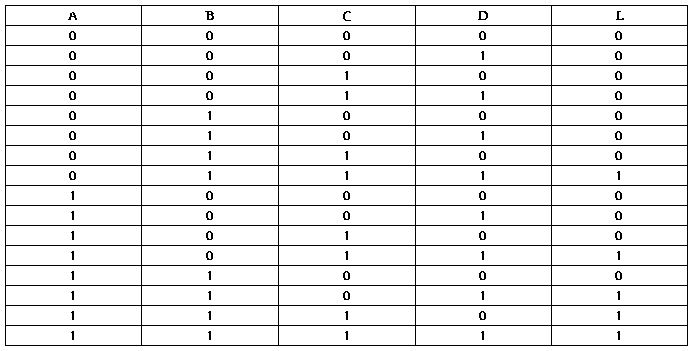

实验数据记录以及实验结果

全加器实验测试结果满足全加器的功能,真值表:

(二)奇偶位判断器

实验原理:数码奇偶位判断电路是用来判别一组代码中含 1 的位数是奇数还是偶数的一种组合电路。

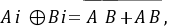

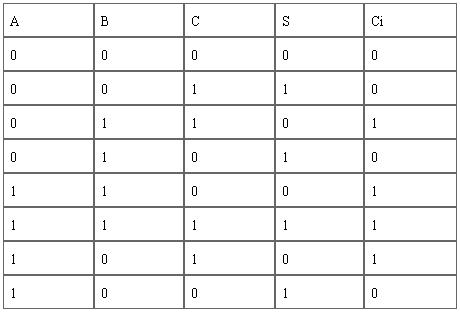

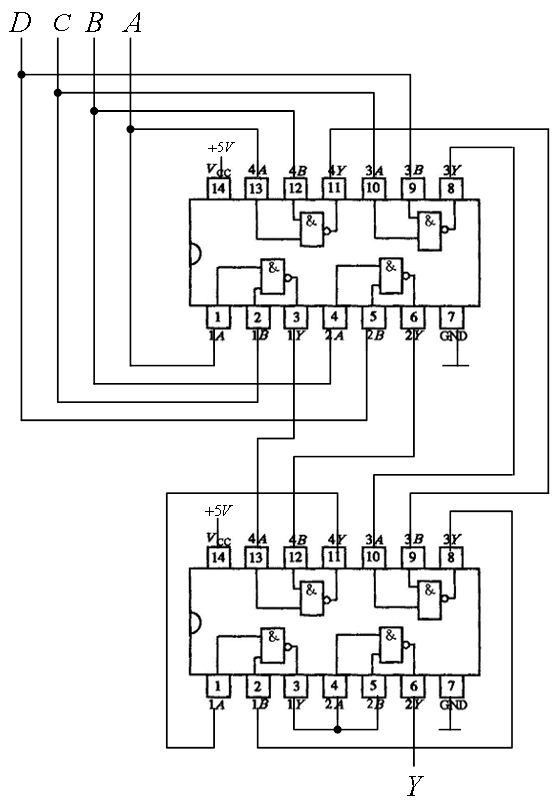

实验内容:用 74LS00与非门和 74LS55 与或非门设计四位数奇偶位判断电路,并进行功能测试。

设计过程:首先列出真值表,画卡诺图,然后写出电路的逻辑函数,即 Z=A⊕B⊕C⊕D ,当代码中含1的位数为奇时,输出为1,二极管发光。然后根据所提供的元件(两个 74LS00与非门、三个 74LS55与或非门),对该逻辑函数进行转化,使得能在现有元件的基础上实现该逻辑函数。Z=((A⊕B)⊕(C⊕D)),可用设计三个异或门来实现,即两个 74LS00与非门(实际用到了6个独立的与非门)、三个 74LS55与或非门来实现。

…… …… 余下全文

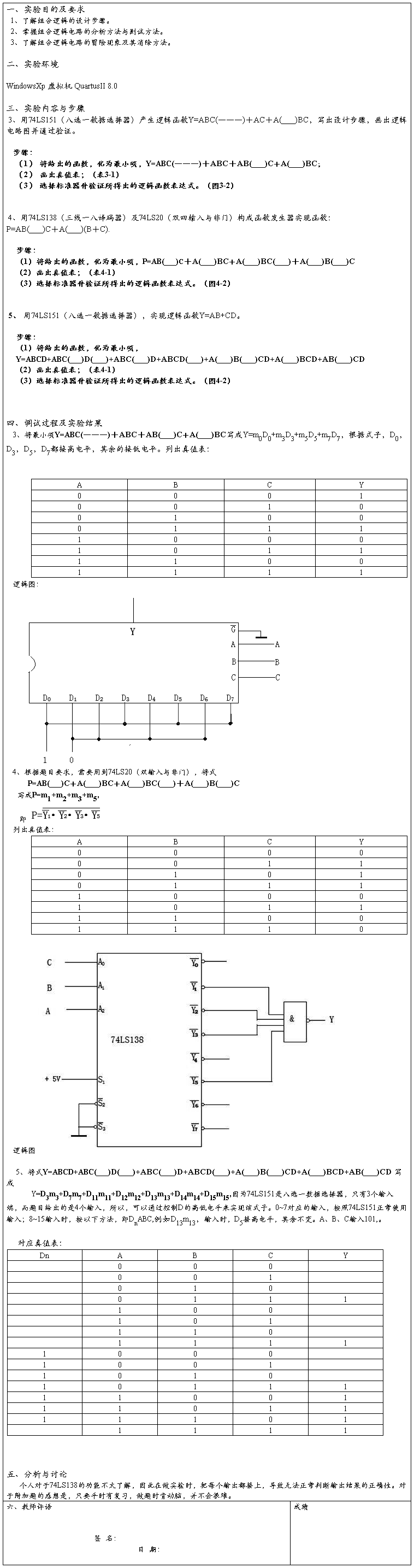

实验线路图

实验线路图

实验线路图

实验线路图